# AWAY FROM LINEAR MODELS OF CONCURRENT PROGRAMS

A THESIS SUBMITTED TO

THE UNIVERSITY OF KENT

IN THE SUBJECT OF COMPUTER SCIENCE

FOR THE DEGREE

OF PHD.

By Daniel Wright October 2022

## Abstract

Traditional approaches to imperative programming language semantics rely on first defining how each individual statement modifies the memory state, and then composing these definitions into a whole program via the interpretation of the sequential composition operator: the humble semicolon. The creation of the multiprocessor and advent of parallelism began to challenge this model. No longer was a program a single, linear sequence of statements, but it had statements which might occur in one order or another, or even simultaneously. To add to the complexity, compilers and hardware began to optimise their input programs, reordering and removing statements to improve runtime performance. The resulting stack of transformations and complications caused runtime executions to drift progressively further away from the program that a programmer believed they were writing.

Several approaches to this have appeared: process calculi which forbid processes from sharing memory and instead force them to communicate directly, maintaining sequential consistency, in which an execution must at least *appear* to be respecting the ordered sequence of statements model, and permitting weak memory ordering, in which an execution must maintain orders involving explicitly synchronised accesses but is free to reorder everything else. While weak memory is preferred by engineers building high-performance code, due to the relatively high cost of both passing messages and maintaining sequential consistency, the problem of creating a sound weak memory semantics for a real-world programming language with shared memory concurrency has yet to be fully solved.

Here we present a weakly ordered semantics for shared memory concurrency, given as an extension to a previously published model. We show that the existing model can be integrated into reasoning techniques which rely on an operational semantics, and that program transformations which cannot introduce new behaviours can be expressed as a relation over the objects of this semantics. We then add a layer of abstraction to the model which allows us to represent dynamic memory allocation in a weak memory context for the first time.

## Acknowledgements

My sincere thanks go to my supervisor Mark for letting me run off into the weeds and return with this, to my mother Oleander for raising a computer scientist, and to my sister Jade for being my rock for so many years.

## Contents

| A | Abstract                                   |         |                                           |    |  |  |  |  |

|---|--------------------------------------------|---------|-------------------------------------------|----|--|--|--|--|

| A | Acknowledgements                           |         |                                           |    |  |  |  |  |

| 1 | Introduction                               |         |                                           |    |  |  |  |  |

|   | 1.1                                        | Struct  | sure                                      | 2  |  |  |  |  |

| 2 | Background and Related Work                |         |                                           |    |  |  |  |  |

|   | 2.1                                        | Semar   | ntics for Sequential Programs             | 4  |  |  |  |  |

|   | 2.2                                        | Failur  | e Modes of Sequential Semantics           | 6  |  |  |  |  |

|   |                                            | 2.2.1   | Reordering Optimisations                  | 6  |  |  |  |  |

|   |                                            | 2.2.2   | Non-Multicopy Atomic Hardware             | 9  |  |  |  |  |

|   |                                            | 2.2.3   | The Thin Air Problem                      | 10 |  |  |  |  |

|   | 2.3                                        | Comp    | eting Semantics for Weak Memory Programs  | 11 |  |  |  |  |

|   |                                            | 2.3.1   | Promising                                 | 12 |  |  |  |  |

|   |                                            | 2.3.2   | The Java Memory Model                     | 19 |  |  |  |  |

|   | 2.4 Moving Away From Trace-Based Semantics |         |                                           |    |  |  |  |  |

|   |                                            | 2.4.1   | Event Structures                          | 28 |  |  |  |  |

|   |                                            | 2.4.2   | WeakestMO                                 | 30 |  |  |  |  |

|   |                                            | 2.4.3   | The Sewell and Pichon-Pharabod model      | 40 |  |  |  |  |

| 3 | Modular Relaxed Dependencies               |         |                                           |    |  |  |  |  |

|   | 3.1                                        | Labell  | led Event Structures                      | 49 |  |  |  |  |

|   |                                            | 3.1.1   | Operations on Labelled Event Structures   | 51 |  |  |  |  |

|   |                                            | 3.1.2   | Interpreting Programs as Event Structures | 51 |  |  |  |  |

|   |                                            | 3.1.3   | Executions                                | 56 |  |  |  |  |

|   | 3.2                                        | Justifi | cation and Dependency                     | 57 |  |  |  |  |

|   |     | 3.2.1                                       | Forwarding                            |  |  |  |  |  |  |

|---|-----|---------------------------------------------|---------------------------------------|--|--|--|--|--|--|

|   |     | 3.2.2                                       | Coproduct                             |  |  |  |  |  |  |

|   |     | 3.2.3                                       | Expanding Coproduct to Sets           |  |  |  |  |  |  |

|   | 3.3 | Worked                                      | d Examples                            |  |  |  |  |  |  |

|   |     | 3.3.1                                       | Freezing                              |  |  |  |  |  |  |

|   |     | 3.3.2                                       | Updates and Rationale                 |  |  |  |  |  |  |

|   | 3.4 | Advant                                      | tages Over Trace-Based Models         |  |  |  |  |  |  |

| 4 | A R | A Refinement Relation For MRD Structures 73 |                                       |  |  |  |  |  |  |

|   | 4.1 | Prelimi                                     | inaries                               |  |  |  |  |  |  |

|   | 4.2 | Observ                                      | ational Refinement                    |  |  |  |  |  |  |

|   | 4.3 | Modula                                      | ar Refinement                         |  |  |  |  |  |  |

|   |     | 4.3.1                                       | Environment Tracking                  |  |  |  |  |  |  |

|   |     | 4.3.2                                       | Embeddings and Validity               |  |  |  |  |  |  |

|   |     | 4.3.3                                       | Execution Simulation                  |  |  |  |  |  |  |

|   |     | 4.3.4                                       | Common Prefix Preservation            |  |  |  |  |  |  |

|   |     | 4.3.5                                       | Full Definition                       |  |  |  |  |  |  |

|   | 4.4 | Proper                                      | ties of Refinement                    |  |  |  |  |  |  |

|   |     | 4.4.1                                       | Soundness                             |  |  |  |  |  |  |

|   |     | 4.4.2                                       | Closure under continuation            |  |  |  |  |  |  |

|   |     | 4.4.3                                       | Closure under context                 |  |  |  |  |  |  |

|   | 4.5 | Symbo                                       | lic Environment Event Structures      |  |  |  |  |  |  |

|   |     | 4.5.1                                       | Conditionals                          |  |  |  |  |  |  |

|   |     | 4.5.2                                       | Executions                            |  |  |  |  |  |  |

|   |     | 4.5.3                                       | Justification                         |  |  |  |  |  |  |

|   |     | 4.5.4                                       | Freezing                              |  |  |  |  |  |  |

|   |     | 4.5.5                                       | Semantic Interpretation               |  |  |  |  |  |  |

|   |     | 4.5.6                                       | Soundness                             |  |  |  |  |  |  |

|   | 4.6 | Closure                                     | e under environment                   |  |  |  |  |  |  |

|   | 4.7 | Refiner                                     | ment in the Java Causality Test Cases |  |  |  |  |  |  |

|   |     | 4.7.1                                       | Test Cases 2 and 3                    |  |  |  |  |  |  |

|   |     | 4.7.2                                       | Test Case 6                           |  |  |  |  |  |  |

|   |     | 4.7.3                                       | Test Case 7                           |  |  |  |  |  |  |

|   |     | 4.7.4                                       | Test Case 17                          |  |  |  |  |  |  |

|   |     | 4.7.5                                       | Conclusions                           |  |  |  |  |  |  |

| 5 | $\mathbf{A}\mathbf{n}$ | MRD         | Based Owicki-Gries Style Logic                        | 113   |  |  |

|---|------------------------|-------------|-------------------------------------------------------|-------|--|--|

|   | 5.1                    | Hoare       | Logic and the Owicki-Gries Method                     | . 114 |  |  |

|   |                        | 5.1.1       | A Semicolon-Free Hoare Logic                          | . 116 |  |  |

|   | 5.2                    | An O        | perational Semantics With MRD                         | . 120 |  |  |

|   |                        | 5.2.1       | Program Futures                                       | . 120 |  |  |

|   |                        | 5.2.2       | Abstract Machine and Transition Relation              | . 121 |  |  |

|   |                        | 5.2.3       | Example                                               | . 124 |  |  |

|   |                        | 5.2.4       | Equivalence between MRD and the operational semantics | . 125 |  |  |

|   | 5.3                    | Progra      | am Logic                                              | . 129 |  |  |

|   |                        | 5.3.1       | Worked Examples                                       | . 132 |  |  |

|   | 5.4                    | Drawl       | oacks and Room for Improvement                        | . 135 |  |  |

| 6 | Syn                    | nbolic      | Event Structures                                      | 137   |  |  |

|   | 6.1                    | Struct      | cures, Events, and Conditions                         | . 138 |  |  |

|   |                        | 6.1.1       | Condition Notation                                    | . 139 |  |  |

|   | 6.2                    | Buildi      | ing SES                                               | . 140 |  |  |

|   |                        | 6.2.1       | Read Appends                                          | . 140 |  |  |

|   |                        | 6.2.2       | Write Appends                                         | . 141 |  |  |

|   |                        | 6.2.3       | Branch Appends                                        | . 141 |  |  |

|   |                        | 6.2.4       | While loops                                           | . 142 |  |  |

|   |                        | 6.2.5       | Sequential Composition                                | . 143 |  |  |

|   |                        | 6.2.6       | Parallel Composition                                  | . 143 |  |  |

|   |                        | 6.2.7       | Full Semantic Interpretation Function and Examples    | . 144 |  |  |

|   | 6.3 Executions         |             |                                                       |       |  |  |

|   | 6.4                    | Deper       | ndency Calculations                                   | . 147 |  |  |

|   |                        | 6.4.1       | Forwarding                                            | . 148 |  |  |

|   |                        | 6.4.2       | Initial Justifications and Single-Execution Rewrites  | . 148 |  |  |

|   |                        | 6.4.3       | Coproduct                                             | . 151 |  |  |

|   |                        | 6.4.4       | Freezing                                              | . 154 |  |  |

|   |                        | 6.4.5       | Program-Wide Guarantees                               | . 154 |  |  |

|   |                        | 6.4.6       | Worked Examples                                       | . 155 |  |  |

|   | 6.5                    | Equiv       | alence to Concrete Value MRD                          | . 165 |  |  |

| 7 | Poi                    | Pointers 17 |                                                       |       |  |  |

|   | 7.1                    | Unint       | erpreted Symbolic Locations                           | . 177 |  |  |

|                |       | 7.1.1  | Retrofitting Existing Events                      | . 177 |

|----------------|-------|--------|---------------------------------------------------|-------|

|                |       | 7.1.2  | Reading, Writing, and Dereferencing Pointers      | . 178 |

|                |       | 7.1.3  | Allocation and Freeing                            | . 179 |

|                |       | 7.1.4  | Undefined Behaviour                               | . 181 |

|                |       | 7.1.5  | Uninterpreted Location Test Cases                 | . 183 |

|                | 7.2   | Choice | es of Location Semantics                          | . 185 |

|                |       | 7.2.1  | Plain Integers                                    | . 186 |

|                |       | 7.2.2  | The CompCert Model                                | . 187 |

|                |       | 7.2.3  | Provenance Models                                 | . 191 |

|                | 7.3   | Explor | ring the Differences Between Pointer Semantics    | . 196 |

|                |       | 7.3.1  | Plain Integers                                    | . 197 |

|                |       | 7.3.2  | CompCert                                          | . 198 |

|                |       | 7.3.3  | VIP                                               | . 199 |

| 8              | Con   | clusio | ns and Future Work                                | 200   |

| 8.1 Conclusion |       |        | ısion                                             | . 200 |

|                | 8.2   | Future | Work                                              | . 201 |

|                |       | 8.2.1  | Program Logics Over Symbolic MRD                  | . 201 |

|                |       | 8.2.2  | Integration of Canonical Synchronisation Orders   | . 201 |

|                |       | 8.2.3  | Tooling and Automation                            | . 201 |

|                |       | 8.2.4  | Completeness Results Over Optimisations           | . 202 |

|                |       | 8.2.5  | Mixed Size Accesses and Alignment                 | . 202 |

|                |       | 8.2.6  | Dependency Beyond Weak Memory: Garbage Collection | . 202 |

| Bi             | bliog | graphy |                                                   | 205   |

## Chapter 1

### Introduction

Computer programmers generally consider it a virtue to know what a program will do without needing to execute it first. This is a difficult virtue to attain, in part because computers

are very complicated. Interacting with memory involves a surprisingly large number of specialised components designed to make memory operations as fast as possible - not only does the

hardware make decisions about execution order, allowing instruction pipelining, determining

when to flush cache lines, and even more complex optimisations such as branch predictions and

speculative execution, but programs are almost always written using compilers and assemblers

(or interpreters), not as raw machine code, and these tools can likewise make decisions about

which parts of the program should run at which times, and which can be delayed or even optimised away entirely. To avoid requiring that all programmers understand every nuance of both

the hardware and software involved in creating and running a computer program, we rely on

abstractions.

Typically, a programmer will view their program as a linear sequence of statements which are executed in the order in which they are written. Programming languages usually describe themselves from this perspective, both those with mathematical descriptions of their behaviour like Haskell or ML family languages and those with natural language definitions such as C. Great efforts have been made by compiler and hardware engineers to preserve the soundness of this abstraction, even while implementing optimisations that alter execution order at runtime.

When trying to execute a program that accesses the same shared memory in multiple concurrent threads, however, this abstraction breaks down despite these efforts. These optimisations are now observable — we are now not only observing memory state when our own thread performs a read, but also whenever another thread could potentially perform a read. Swapping

the order of two writes to unrelated locations is no longer undetectable. However, these optimisations are valuable. Disabling them risks counteracting the performance improvements that concurrency is intended to provide. An ideal solution would be to define exactly when any given statement in the program might run, so that programmers can still predict what their program will do even after these reorderings, but this is a complicated task. A single optimisation can be described easily in terms of the contexts in which is occurs and the change it makes to the program, but describing an entire chain of such optimisations simply by composing their individual semantics is undesirable. The description would only work for that chain — the same C program would have one "meaning" under GCC with one set of flags and another under Clang with a different set of flags.

We want one semantics for our language, but we want one that captures all of these optimisation chains, using all common components, in any order. Or, equivalently, we want a semantics that captures all of the ways we can't reorder the statements in our program. This problem is captured in the idea of dependencies. If one statement depends on the state observed by another, then they should never be reordered. If two statements are independent, then any optimisation should be free to reorder them. The goal of a weak memory model is to combine some idea of dependency with the set of explicit and implicit synchronisation operations provided by a particular language or architecture to describe what an input program may be allowed to do. This thesis discusses one such model, called the Modular Relaxed Dependencies model, and compares it to other models in the same space.

#### 1.1 Structure

This thesis is divided into 6 chapters beyond the introduction. In chapter 2, we give a brief overview of why weak memory models are used and how four existing models, namely the Promising semantics, and the Java memory model, the WeakestMO model, and the "Bubbly" model, explain what an input program may or may not do. We also introduce event structures, which are used as the basis for the Modular Relaxed Dependencies model.

In chapter 3, we present the Modular Relaxed Dependencies, or MRD, model in its entirety, with a small change from the definitions given in the initial publication in Paviotti et al. (2020). We show by example how the behaviours permitted and forbidden by the MRD model differ from the models introduced in chapter 2, and how this approach is unique. I was a co-author on this publication, but joined late in the development of the model and predominantly worked on the refinement relation described in the next chapter.

In chapter 4, we introduce a relation over MRD structures which can be used to reason about the validity of program transformations which change the observable behaviour of a program but preserve its correctness, by taking in a set of significant locations as a parameter and allowing more transformations of accesses to the remaining insignificant locations. By parameterising the relation over a set of locations whose value is considered significant to correctness, we can discuss particular cases of optimisation in detail without relying on a global, application-insensitive definition of "correctness-preserving". This appears in the appendix of Paviotti et al. (2020), but not in the main body of the publication, and is entirely my own work.

We further investigate program correctness in a weak memory context in chapter 5, where we construct a program logic to create correctness proofs over weakly ordered concurrent programs, published in Wright, Batty and Dongol (2021). In the process, we construct an operational semantics which uses a partial order over program events to nondeterministically choose an execution order from a set of permissable orders, demonstrated with the semantic dependency relation generated by MRD. We then construct an indexing function which can guide a Hoare logic-style pre- and postcondition chain across this operational semantics. This presents a novel approach to the verification of weak memory programs by decoupling the traditionally syntax-driven method of program logics from the syntax-induced ordering of program statements. I constructed the proof that the operational semantics describes executions of the underlying model, while the semantics and program logic were produced in collaboration with Mark Batty and Brijesh Dongol. This logic has subsequently been formalised in Isabelle/HOL by Dalvandi et al. (2022).

In chapter 6, we introduce Symbolic MRD, a generalisation of MRD structures designed to allow more compact representations of larger input programs. This construction was made in part to increase the size and complexity of the litmus tests for which the model could give a legible output in a reasonable amount of computation time, but also to remove the restriction that all values read in a program come from a finite, pre-determined set. This paves the way for the work in chapter 7, which introduces addresses as values to symbolic MRD and opens the door to the inclusion of pointer manipulation and dynamic memory allocation in programs using shared memory concurrency. These chapters are entirely original contributions, and as yet unpublished.

## Chapter 2

## Background and Related Work

#### 2.1 Semantics for Sequential Programs

The semantics of any language is generally comprised of a definition for each type of statement in the language, and a description of how these definitions interact. It allows one to model what the language is saying about the world outside of the language itself. Where natural languages tend to talk about the real world, and have sentences to describe objects, places, properties, and so on, programming languages prefer to talk about the computer. As a result, statements in a programming language generally describe either an expression whose value is to be computed or the storage or retrieval of a value from memory.

When defining the semantics of a programming language, its creators must balance the thoroughness of the definition against the ease with which any program written in the language may be reasoned about. We tend to want a large amount of abstraction for a semantics, especially from the details of the hardware. A compiler for a given language on a given target architecture is functionally a semantics, as it describes all the statements of the language in terms of assembly instructions, but it isn't a very useful one. It has too many complexities which don't influence the properties of a program that a programmer is likely to care about, it is too hard to read, and it only describes behaviour under one specific architecture. At the other end of the scale, a simple description of what each operation should do in a natural language such as English can also be a semantics. For instance, writing "The + operator takes two parameters and returns their sum" is an acceptable definition of "+", provided the reader understands concepts such as return values and summation. However, this sometimes doesn't give enough information: what happens if I were to try using letters in place of numbers? What if my arguments cause

side effects when evaluated and I care about what order they execute in? The more details I include, the longer the sentence becomes, and the harder it is to read. Instead of either plain English, which is too imprecise, or machine instructions, which contain substantially more detail than is desirable, semantics for programming languages are often given in mathematics. When this mathematics is being written, a large number of design decisions, both conscious and unconscious, are made. Authors of a semantics must decide which parts of the execution of a statement are important to the meaning of a program and should be represented, and which parts are unimportant and should be left to the implementor's discretion.

If we were to build a toy programming language, we would likely want programs written in it to be *able* to do the following:

- Evaluate arithmetic expressions, as in 1 + 2

- Compute truth values, as in 1 < 2

- Store values in variables, as in a := 1

- Substitute the values in those variables during arithmetic expressions, as in a + 2

- Change their behaviour based on truth values, as in if (a < 2) { b } else { c }

- Repeat statements, as in GOTO or while (a) { b }

These means we want a mathematical description of what each of these types of statements does.

Describing the first two is easy; we can delegate this to the mathematics we're already using to describe everything else. We don't need to do any heavy lifting yet.

The next two points are trickier, since they need to refer to some piece of memory. We don't want to think about machine addresses or page tables or any of the other complexities of accessing memory in a computer, so we abstract them away into some fairly simple model of a bag of labelled boxes. To evaluate a := 1, fetch the box labelled "a" from memory and update the contents to be "1". To evaluate a + 2, fetch the box labelled "a" again and evaluate the expression after you replace all instances of "a" with its contents. The mechanical details of doing this are left to the engineers who implement our language. The mathematical details usually rely on tracking the current set of mappings from symbols to values, often in terms of a partial function which is updated every time a write is interpreted.

The final two points require us to start modelling, or at least referring to, the rest of the program text somehow. If we break the text into statements and number each of them sequentially, we can define actions like "evaluate the program starting at statement 3", or "evaluate

everything between statement 4 and statement 10". We now assume that whenever we finish evaluating statement n, we maintain our memory state and start evaluating statement n + 1 unless the program tells us to do otherwise.

These decisions seem very intuitive to us. They might seem so intuitive that we don't notice them being made at all. We might even spend decades writing semantics which make decisions just like these, and then, after successfully engineering computers that can run multiple instructions at once, start adding ideas like threads to our semantics to make better use of this new hardware. That might not work.

#### 2.2 Failure Modes of Sequential Semantics

While purely sequential styles of semantics are intuitive, the actual evaluation of a program is vastly more complex. There is a sequence of transformations which takes us from source code to hardware behaviour, and each of them can slightly alter the behaviour of its input. Even in relatively simple cases, first the source code must be compiled down to assembly and may be optimised by the compiler during this process. It can remove trips to memory via constant propagation, lift statements out of loop bodies or conditionals, and generally deviate from the assumed behaviour of the program as long as its output is consistent with the sequential semantics of the language. The assembly must then be assembled into machine instructions and executed by the hardware, which promises particular outcomes given particular inputs via the architecture specification but often provides weak guarantees about ordering. It may include cache hierarchies, branch predictors, or pipelines which reorder memory accesses. More portable languages such as Java may compile down to bytecode to be executed by a virtual machine, which will have its own set of optimisation steps.

In this section we give an overview of how these various components can alter the order in which program statements execute, and how concurrent threads can change their behaviour based on these reorderings.

#### 2.2.1 Reordering Optimisations

The term Sequential Consistency or SC, articulated by Lamport (1979), applies to any specification for a multiprocessor in which the observed behaviour of said processor is indistinguishable from a purely sequential execution of the same program. Contemporary multiprocessors often violate this restriction in various ways for the sake of performance improvements.

#### Store and Load Buffering

Suppose we have a program fragment that looks like this:

When we run this program fragment, it turns out that accessing y is very fast - in fact, it's in our L1 cache. Unfortunately, it's been too long since we last accessed anything near x and as a result it isn't mapped to any of our cache space. The write to x is going to take a very long time (in computer terms) to complete. We could sit here and twiddle our thumbs for a while, idling the entire machine until the write finishes, but this would be a very inefficient thing to do. We wouldn't see any difference, from the perspective of a single-threaded program, if we performed the load before we were done with the store. We refer to this as  $store\ buffering$ : we are allowed to perform other operations while we wait for a store to commit to memory, as long as the store wouldn't impact their outcome.

This is precisely what even the relatively restrictive x86 hardware is allowed to do in this situation. Specifically, according to the litmus tests provided by Intel, the following program is allowed to terminate with both the EAX and EBX registers containing 0 (Sewell et al. (2010)):

A simple operational semantics closely linked to program order cannot arrive at this outcome. There's no way of executing this while modelling memory as a bag of instantaneously available bits and program execution as only starting statement 2 with the environment it arrives at after executing statement 1 that arrives at this outcome.

Store buffering has a similar counterpart, known as *load buffering*. This time, instead of waiting for a store to finish updating memory, we would be waiting for a load to finish retrieving a value from memory.

A similar cache hierarchy can cause load buffering in this example:

Suppose the location y is rarely used and takes multiple cycles to access, so we want to avoid waiting for the value if we could be performing other operations in that time. We don't need to be sure that we have the correct value in r1 before executing the store, so we may as well perform it before the load has returned.

This can likewise result in counterintuitive behaviours in a concurrent context, as in this program fragment where the outcome  $\mathtt{r1} = \mathtt{r2} = 1$  is permitted, though not currently observed, on POWER multiprocessors (Sarkar et al. (2011a)) and both permitted and observed on ARMv7 (Alglave et al. (2011)):

In the following, we can try to describe which conditions cause non-sequentially consistent optimisations to be allowed. We can start with our initial observations about reordering stores and loads:

If a pair of memory accesses in a thread are unrelated, they may be executed in any order. If two accesses are to different variables, they are by default unrelated.

#### **Branch Elimination**

We have mentioned that *unrelated* reads and writes may be reordered, accesses to the same variable are not the only type of related accesses. In the following case, it's clear that performing the read after the write is impossible:

We can't know if the guard will evaluate to true or false if we don't have the correct contents for r1. This means we need to tighten our definition of "unrelated":

If a load event is used by a branch statement, the load is related to any stores within the scope of the branch statement.

As branch instructions are relatively slow, however, it's preferable for program optimisations to remove any unnecessary branch statements. This might happen in cases where the guard is always true:

In this case, a compiler could determine that the check always passes and remove the branch entirely. This means we need to further tighten our definition of relatedness: If the value observed at a load operation cannot impact the truth of the guard condition, the load event and the writes below the guard are unrelated.

There is another case where a load and store might be unrelated despite the syntactic presence of a branch condition, but this time due to the presence of another store:

```

r1 := x;

if (r1 = 1) {

y := 1;

} else {

y := 1;

}

```

In this case, while we do need the value of the load to determine the truth of the guard, we don't need the truth of the guard to determine whether or not to perform the store. Branch elimination optimisations are well-known (Bodík, Gupta and Soffa (1997), Mueller and Whalley (1995)) and widely implemented (Kotzmann et al. (2008), Calder, Grunwald and Zorn (1994), llv (2014)).

If a store is within the scope of a branch statement but an identical store appears in the other branch, the store is unrelated to any loads required by the guard.

#### 2.2.2 Non-Multicopy Atomic Hardware

Multicopy atomicity is the guarantee that if one thread reads some value v from a global variable, every other thread must also read v if they access it between that read and any subsequent write. It promises that regardless of the complexity of our memory layout, which might sometimes have multiple copies of the same address holding different values at the same time, the programmer can still view memory as being a single, universally accessible object.

Hardware designed around multiple physical cores can violate this abstraction by having a small per-core cache that does not need to flush its contents to main memory between every operation. A program that one would expect to write to a global location can write to this local cache and perform several other operations before that write becomes visible. This means that if location x contains the value 0 and thread  $t_1$  performs a write of 1 to it, thread  $t_1$  can observe that x now contains 1 while thread  $t_2$  observes that it still contains 0.

This type of behaviour is not permitted on x86 (Sewell et al. (2010)) or ARMv8 (Pulte et al. (2017))<sup>1</sup>, but it is permitted by POWER (Mador-Haim et al. (2012)).

To give an example of non-MCA behaviour in action, consider the following program:

<sup>&</sup>lt;sup>1</sup>Non-MCA behaviour was allowed in an initial version of the standard but later removed.

```

x := 0;

x := 1;

r1 := x;

y := r1;

v := 2;

r2 := y;

if (r2 = 2) {

r3 := x;

```

At the end of this program, we are allowed to observe the state r1 = 1, r2 = 2, r3 = 0. This means that the final load into r3 has observed the value from the first write to x, while the load into r1 has observed the second one. We can tell that every line in the first thread is related to its neighbours, but the second thread is still free to observe them out of order.

In non-MCA settings, relatedness is only visible within the thread containing the memory accesses.

#### 2.2.3 The Thin Air Problem

Gathering together our requirements from the previous section, we end up with the following:

- Memory accesses which are unrelated are reorderable.

- Memory accesses to the same variable within a thread are related.

- Loads whose value is used in a guard are related to any stores which only appear in either the true or false branch of the statement which uses the guard.

- In a non-MCA environment, accesses which are related in one thread may be observed to have been reordered by another thread.

If we want to allow the reordering of loads and stores within a thread, we encounter a problem whenever we try to interpret a load within a program. That is: we can't know, at the time of interpreting it, what the memory state might be. We can be sure that any related stores that come before it syntactically have happened, but we can't make assertions about what the other thread could have done so far. However, if a semantics is too permissive about what a load can observe, it allows so-called *thin air* values. It's clear that if, say, the value 42 is never written to the location x during the execution of a program, the value 42 should never be observed in a load from x. It is likewise true that if the value 42 can only be stored *after* the load in question, it should similarly never be allowed to observe 42.

In the above example, a naïve semantics allows both threads to read 42 at their respective accesses and copy the values into global memory, and then asserts that, since 42 has been written to both global variables, the reads must be possible. Thread 1 can observe 42 at x prior to thread 2 observing 42 at y and vice versa. The key observation here should be that both of these things can't simultaneously be true:

The role of a memory model therefore cannot be described as simply defining when operations may be reordered according to their context, but also to detect when a particular behaviour relies on these types of causality cycles.

#### 2.3 Competing Semantics for Weak Memory Programs

The field of weak memory models, while relatively young, is somewhat crowded. Out-of-order accesses have the potential to cause undiagnosable bugs and security vulnerabilities, to violate type safety, and to invalidate formal correctness proofs which assume sequential consistency (Boehm and Demsky (2014)). They have also been incorrectly described in a publicly available standards documents for major languages (Pugh (1999), Ševčík and Aspinall (2008), Boehm and Demsky (2014), Vafeiadis et al. (2015), Lahav et al. (2017)).

In this section we offer a brief overview of a handful of existing models, with worked examples, and later we show how Modular Relaxed Dependencies handles the same programs.

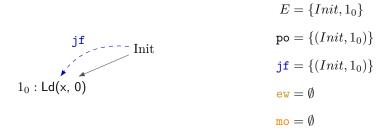

#### The Initialisation Program

Before diving into any particular memory model, it is helpful to mention a feature they often have in common: the inclusion of an initialisation program. Whenever a program is compiled or interpreted and a new variable is declared, one of three things may happen: the compiler or runtime may set the value to an acceptable default, it may refuse to compile if a value is not set before the variable is accessed, or the language standard may declare it "undefined behaviour" to access the variable prior to initialising it and cause the program to have no semantics at all.

As memory models intend to be as explicit as possible about the state of memory at all times, they produce unreliable outputs, or outright halt, if "invisible" writes such as variable initialisation are left out. The common solution is to have a section at the beginning of any

program, sometimes called the initialisation program or Init, which sets the value of every global variable to 0.

#### 2.3.1 Promising

The Promising semantics uses program order driven execution, but allows non-sequentially consistent interleavings by allowing a thread to observe writes which have yet to be interpreted. A thread can promise that at some point later in execution it will perform a write, given its current state would allow it to do so. Other threads can then read this promise as though it were a write that had actually been performed. It is a per-execution model, meaning it describes when an individual execution of a program is permitted.

This section, as with all subsequent descriptions of memory models, begins with a technical description of the semantics and proceeds into a series of examples demonstrating how these descriptions evaluate a program.

#### **Definitions**

Any write to a location in memory is represented as a timestamped message  $\langle x, v@t \rangle$ , where:

- x is the location being written to

- $\bullet$  v is the value being written

- t is the time at which the write occurred

The memory is not represented as a map from locations to values, but instead as a set of these messages which grows as the program executes.

The thread state is represented as a tuple  $(\sigma, V, P)$ , where:

- $\sigma$  is a function from thread-local variables to values.

- V is a *view* function, which maps global variables to the timestamp of the last memory access observed by this thread.

- P is a set of outstanding promises made by this thread.

Whenever a thread performs a load of x, it must load from a message which has a timestamp value greater than or equal to V(x). Whenever a thread performs a store to x, it must create a message which has a timestamp value strictly greater than V(x). Both of these operations update V(x) with the new latest value.

SILENT

$$\frac{\sigma \xrightarrow{silent} \sigma'}{\langle \langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma', V, P \rangle, M \rangle} \qquad \text{STEP} \frac{\langle \mathcal{TS}(i), M \rangle \rightarrow^{+} \langle \mathcal{TS}', M' \rangle}{\langle \mathcal{TS}', M' \rangle \text{ is consistent}} \\ \frac{\sigma \xrightarrow{R(x,v)} \sigma' \quad \langle x, v@t \rangle \in M}{V(x) \leq t \quad V' = V[x \mapsto t]} \qquad \frac{\sigma \xrightarrow{W(x,v)} \sigma' \quad M' = M \leftrightarrow \langle x, v@t \rangle}{V(x) < t \quad V' = V[x \mapsto t]} \\ \frac{V(x) \leq t \quad V' = V[x \mapsto t]}{\langle \langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma', V', P \rangle, M \rangle} \qquad \text{WRITE} \frac{\sigma \xrightarrow{W(x,v)} \sigma' \quad M' = M \leftrightarrow \langle x, v@t \rangle}{\langle \langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma', V', P \rangle, M' \rangle} \\ \frac{M' = M \leftrightarrow m \quad P' = P \leftrightarrow m}{\langle \langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma', V', P' \rangle, M' \rangle} \\ \frac{\sigma \xrightarrow{W(x,v)} \sigma' \quad \langle x, v@t \rangle \in P \quad P' = P \setminus \{\langle x, v@t \rangle\}}{V(x) < t \quad V' = V[x \mapsto t]} \\ \frac{V(x) < t \quad V' = V[x \mapsto t]}{\langle \langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma', V', P' \rangle, M \rangle}$$

Figure 1: The operational rules for the Promising semantics handling only reads and writes.

After performing any memory access or updating its local state, a thread must validate that each of the promises in P are consistent with the new global memory state. A promise P is consistent with memory state M and thread states  $\mathcal{TS}$  if executing the remainder of the program under these states could lead to the promise being fulfilled, meaning that a message is generated writing the promised value to the promised location at the promised time.

We give the formal operational rules for the Promising semantics in Fig. 1.

#### Permitted Reordering by Example

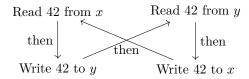

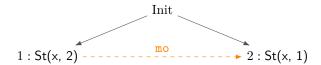

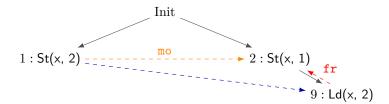

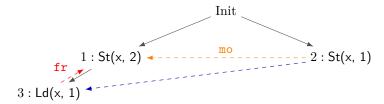

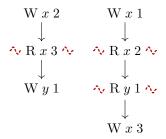

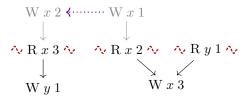

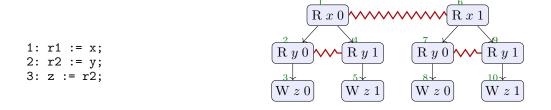

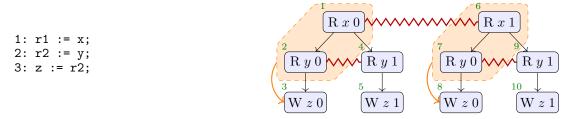

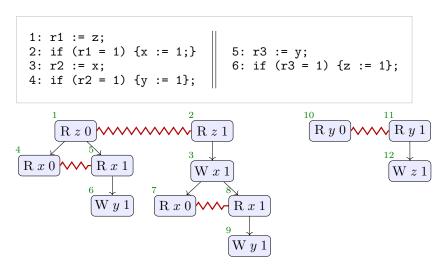

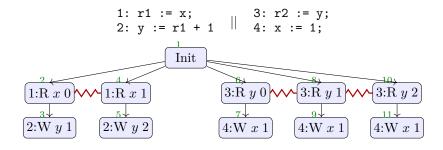

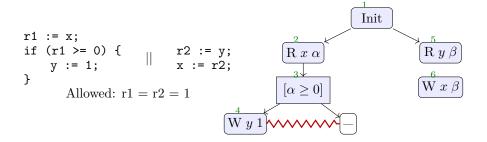

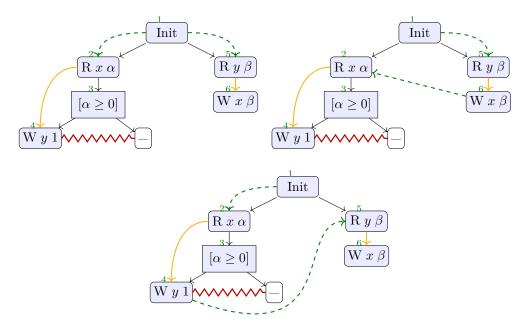

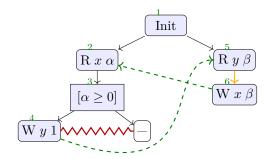

Figure 2: Allowed: r1 = r2 = 1

The program above shows a permitted non-SC reordering potentially being observed by another thread. There is no interleaving of statements between the first and second thread which allows the outcome  $\mathtt{r1} = \mathtt{r2} = 1$ , but the reordering of line 2 above line 1 is permitted and results in this outcome. We now step through an execution of this program under the Promising semantics which does exactly this.

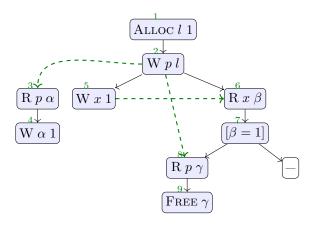

We begin by promising a message  $\langle y, 1@1 \rangle$  in thread 1 and verifying its consistency. Since the value written at line 2 must be 1 regardless of context, this is trivial. Here we show the steps taking by Promising so far, next to the program source. We highlight the point at which we need to fulfil a promise in light green, and link the proposed source of a message observed by a read using a dashed green arrow.

```

0: Write \langle x, 0@0 \rangle, \langle y, 0@0 \rangle

Promise: \langle y, 1@1 \rangle

1: Read \langle x, 0@0 \rangle

2: Write \langle y, 1@1 \rangle

0: x := 0;

0: y := 0;

1: r1 := x;

2: y := 1;

4: x := r2

```

Thread 2 then copies the value of 1 into x, creating the message  $\langle x, 1@1 \rangle$ . This doesn't touch any of the statements used in the initial verification of our promise, so we elide the re-verification step. We highlight program statements in darker green to indicate that they have executed.

```

Promise: \langle y, 1@1 \rangle

1: Read \langle x, 0@0 \rangle

2: Write \langle y, 1@1 \rangle

3: Read \langle y, 1@1 \rangle

4: Write \langle x, 1@1 \rangle

1: r1 := x;

2: y := 1;------3: r1 := y;

4: x := r2;

```

Thread 1 reads this value, and re-verifies that it can still fulfil its earlier promise. Finally, it creates the message  $\langle y, 1@1 \rangle$ .

```

Promise: \langle y, 1@1 \rangle

1: Read \langle x, 0@0 \rangle

2: Write \langle y, 1@1 \rangle

3: Read \langle y, 1@1 \rangle

4: Write \langle x, 1@1 \rangle

1: Read \langle x, 1@1 \rangle

Verify: \langle y, 1@1 \rangle

2: Write \langle y, 1@1 \rangle

2: Fulfil \langle y, 1@1 \rangle

2: Fulfil \langle y, 1@1 \rangle

```

#### Permitted OOTA Execution

```

1: x := 2;

2: r1 := x;

if (r1 != 2){

3: y := 1;

}

4: x := 1;

5: r2 := x;

6: r3 := y;

if (r3 != 0){

7: x := 3;

```

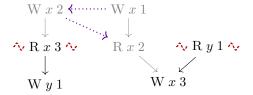

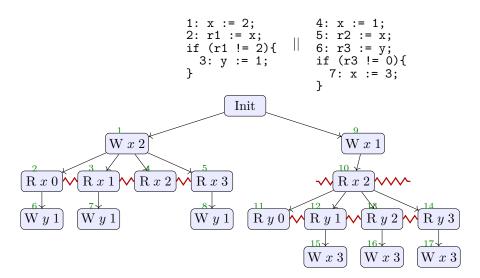

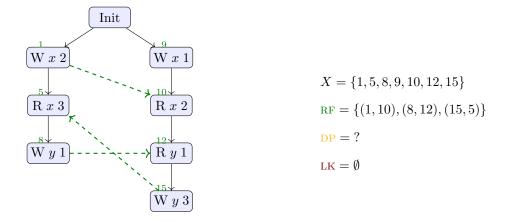

Figure 3: The litmus test OOTA7, with the forbidden outcome  $r1 = 3 \land r2 = 2 \land r3 = 1$ .

In this program, due to Jagadeesan, Jeffrey and Riely (2020), an execution which terminates with the forbidden outcome  $\mathtt{r1} = 3 \land \mathtt{r2} = 2 \land \mathtt{r3} = 1$  may be considered a thin-air execution. We take the description of the permitted execution from (Chakraborty and Vafeiadis (2019)):

- Line 2 reads from line 7

- The execution of line 3 depends on the value at line 2

- Line 6 reads from line 3

- The execution of line 7 depends on the value at line 6

Drawing these constraints as arrows, we see the figure 8 shape in the code reflect the circular reasoning required to observe the forbidden behaviour. The green "reads from" arrows are relatively trivial to construct using any style of semantics, but the calculation of the orange "depends on" arrows is the role of a weak memory model.

We begin by executing the write to  $\mathbf{x}$  on line 4 to obtain memory state  $M_1 = \{\langle x, 1@2 \rangle\}$ . We can now promise that the write to  $\mathbf{y}$  on line 3 will execute: line 1 could create message  $\langle x, 2@1 \rangle$ , allowing line 2 to read the value 1. This gives us  $M_2 = \{\langle x, 1@2 \rangle, \langle y, 1@1 \rangle\}$ .

Figure 4: Execution up to memory state  $M_2 = \{\langle x, 1@2 \rangle, \langle y, 1@1 \rangle\}.$

We can now promise that the write to x on line 7 will execute, as the read of y on line 6 can observe the new value of y in  $M_2$ . We choose timestamp t=4, leading to  $M_3=\{\langle x,1@2\rangle,\langle x,3@4\rangle,\langle y,1@1\rangle\}.$

```

4: Write \langle x, 1@2 \rangle

Promise: \langle y, 1@1 \rangle

1: Write \langle x, 2@1 \rangle

2: Read \langle x, 2@1 \rangle

3: Write \langle y, 1@1 \rangle

Promise: \langle x, 3@4 \rangle

5: Read \langle x, 1@2 \rangle

6: Read \langle y, 1@1 \rangle

3: Write \langle x, 3@4 \rangle

3: Write \langle x, 3@4 \rangle

3: Write \langle x, 3@4 \rangle

```

Figure 5: Execution up to memory state  $M_3 = \{\langle x, 1@2 \rangle, \langle x, 3@4 \rangle, \langle y, 1@1 \rangle\}.$

When we execute the write to x on line 1, we ignore the trace we used to verify the promises and instead generate message  $\langle x, 2@3 \rangle$ . This allows the outcome r2 = 2, but doesn't invalidate either promise: thread 2's promise to write to y is unaffected by the value stored in r2, and

thread 1 can read the promised  $\langle x, 3@4 \rangle$  instead of  $\langle x, 1@2 \rangle$ . We end with memory state  $M_4 = \{\langle x, 1@2 \rangle, \langle x, 2@3 \rangle, \langle x, 3@4 \rangle, \langle y, 1@1 \rangle\}$ .

```

4: Write \langle x, 1@2 \rangle

Promise: \langle y, 1@1 \rangle

1: Write \langle x, 2@1 \rangle

2: Read \langle x, 1@2 \rangle

4: x:= 1;

5: r2 := x;

3: Write \langle y, 1@1 \rangle

2: r1 := x; <--

if (r1 != 2) {

Promise: \langle x, 3@4 \rangle

5: Read \langle x, 1@2 \rangle

6: Read \langle y, 1@1 \rangle

7: Write \langle x, 3@4 \rangle

1: Write \langle x, 2@3 \rangle

Verify: \langle y, 1@1 \rangle

2: Read \langle x, 3@4 \rangle

3: Write \langle y, 1@1 \rangle

```

Figure 6: Execution up to memory state  $M_4 = \{\langle x, 1@2 \rangle, \langle x, 2@3 \rangle, \langle x, 3@4 \rangle, \langle y, 1@1 \rangle\}.$

The sequence of reads then executes as described by the desired outcome. Line 2 observes  $\langle x, 3@4 \rangle$ , and line 5 observes  $\langle x, 2@3 \rangle$ . Each thread finishes by fulfilling its promise

```

4: Write \langle x, 1@2 \rangle

Promise: \langle y, 1@1 \rangle

1: Write \langle x, 2@1 \rangle

2: Read \langle x, 1@2 \rangle

3: Write \langle y, 1@1 \rangle

Promise: \langle x, 3@4 \rangle

1: x := 2;----->5: r2 := x;

5: Read \langle x, 1@2 \rangle

6: Read \langle y, 1@1 \rangle

7: Write \langle x, 3@4 \rangle

if (r1 != 2) {

if (r3 != 0){

1: Write \langle x, 2@3 \rangle

Verify: \langle y, 1@1 \rangle

2: Read \langle x, 3@4 \rangle

3: Write \langle y, 1@1 \rangle

2: Read \langle x, 3@4 \rangle

3: Fulfil \langle y, 1@1 \rangle

5: Read \langle x, 2@3 \rangle

6: Read \langle y, 1@1 \rangle

7: Fulfil \langle x, 3@4 \rangle

```

Figure 7: Completed execution, terminating with  $r1 = 3 \land r2 = 2 \land r2 = 1$ .

This execution is permitted because the lines of reasoning used to certify promises at each machine step are allowed to change. We are initially allowed to write y := 1 under the condition that x := 1 occurs after x := 2, and if we are allowed to write y := 1 then we are allowed to write x := 3. When we proceed in our execution, however, we lose track of the requirement that x := 1 happens last when we choose to read from x := 3 instead. Note that these requirements are still transitive -y := 1 no longer requires the orderings from before, instead it requires the execution of x := 3, but x := 3 still requires y := 1. Since we have already assumed both of

these events will happen, these requirements resolve each other and the cyclicity is never flagged as a problem.

#### A Characteristic for the Promising OOTA Behaviour

Suppose that each message in the Promising semantics is given an additional flag indicating whether or not it originates from a promise which has yet to be fulfilled. Promises are written (Promise m) while writes are written (Write m), while Writes(M) gives the set of Write messages in memory M. We also add a precondition to our stored promises in the form of a message set:

$$\{\mu\}_{\langle \mathcal{TS}, M, S \rangle} \ P \ \langle l, v@t \rangle \ \text{iff} \ \langle \mathcal{TS}, Writes(M) \cup \mu, S \rangle \Longrightarrow \langle \mathcal{TS}', M', S' \rangle \ \text{and} \ (\text{Write} \ \langle l, v@t \rangle) \in M'$$

Where the semantics of  $\Longrightarrow$  are identical to  $\to$  but without the promise and fulfil rules and P is a unique identifier for the promise. Any promise we use during a speculative execution which generates the message promised by P is noted in the precondition.

Whenever we take an operational step over program S, we take S' to be the remaining program and re-validate all our promises, updating the stored objects p from  $\{\mu_1\}_{\langle \mathcal{TS}_1, M_1, S_1 \rangle} p \langle l, v@t \rangle$  to  $\{\mu_2\}_{\langle \mathcal{TS}_2, M_2, S_2 \rangle} p \langle l, v@t \rangle$ .

Finally, in order to validate promises we include the program text S explicitly in the operational semantics.

$$\langle \mathcal{TS}(i), M, S \rangle \to^{+} \langle \mathcal{TS}', M', S' \rangle$$

$$\langle \mathcal{TS}', M', S' \rangle \text{ is consistent}$$

$$\langle \mathcal{TS}, M, S \rangle \to \langle \mathcal{TS}[i \mapsto \mathcal{TS}'], M', S' \rangle$$

$$PROMISE' \xrightarrow{M' = M} \langle \text{(Promise } m) \quad P' = P \leftarrow (\mu, p_i, m) \quad \{\mu\}_{S,M} \ p_i \ m \}$$

$$\langle \langle \sigma, V, P \rangle, M, S \rangle \to \langle \langle \sigma, V, P' \rangle, M', S \rangle$$

$$\sigma \xrightarrow{W(x,v)} \sigma' \quad (\mu, p_i, \langle x, v@t \rangle) \in P \quad P' = P \setminus \{(\mu, p_i, \langle x, v@t \rangle)\}$$

$$V(x) < t \quad V' = V[x \mapsto t] \quad M' = M \cup \{\text{Write } m\} \setminus \{\text{Promise } m\}$$

$$\langle \langle \sigma, V, P \rangle, M, (x := v; S) \rangle \to \langle \langle \sigma', V', P' \rangle, M', S \rangle$$

Figure 8: The modified operational rules which track promise preconditions.

We can describe an OOTA execution as one in which two promises provide messages that are in each other's respective preconditions.

Any execution of the classic OOTA litmus test which produces a thin air value will at some point contain promises  $p_1$  and  $p_2$ :

Promising correctly forbids this because we cannot construct an initial speculative execution for either  $p_1$  or  $p_2$  without the other. We cannot make  $p_1$  first, because we cannot construct an execution from a blank memory state which writes 42 to y. Likewise we cannot make  $p_2$  first because no such execution will write 42 to x either.

The sequence in Fig. 7, however, results in this OOTA shape by swapping one promise from a permissable precondition into a cyclical one *after* both promises have been made.

```

4: Write \langle x, 1@2 \rangle

Promise: \emptyset_{\langle \mathcal{TS}_1, M_1, S_1 \rangle} p_1 \langle y, 1@1 \rangle

1: Write \langle x, 2@1 \rangle

2: Read \langle x, 1@2 \rangle

3: Write \langle y, 1@1 \rangle

Promise: \{\langle y, 1@1 \rangle\}_{\langle \mathcal{TS}_1, M_1, S_1 \rangle} p_2 \langle x, 3@4 \rangle

5: Read \langle x, 1@2 \rangle

6: Read \langle y, 1@1 \rangle

7: Write \langle x, 3@4 \rangle

1: Write \langle x, 2@3 \rangle

Verify: \{\langle x, 3@4 \rangle\}_{\langle \mathcal{TS}_2, M_2, S_2 \rangle} p_1 \langle y, 1@1 \rangle

2: Read \langle x, 3@4 \rangle

3: Write \langle y, 1@1 \rangle

:

```

Figure 9: The operational steps of the OOTA7 program with promise preconditions annotated.

It begins by making two promises from the same point in evaluation, where  $S_1$  is the remainder of the program after executing line 4:

$$\emptyset_{\langle \mathcal{TS}_1, M_1, S_1 \rangle} \ p_1 \ \langle y, 1@1 \rangle \qquad \{\langle y, 1@1 \rangle\}_{\langle \mathcal{TS}_1, M_1, S_1 \rangle} \ p_2 \ \langle x, 3@4 \rangle$$

In the next verification step, where  $S_2$  is the remainder of the program after lines 1 and 4, we are forced to use the result of  $p_2$  to verify  $p_1$ :

$$\{\langle x, 3@4 \rangle\}_{\langle \mathcal{TS}_2, M_2, S_2 \rangle} p_1 \langle y, 1@1 \rangle \qquad \{\langle y, 1@1 \rangle\}_{\langle \mathcal{TS}_2, M_2, S_2 \rangle} p_2 \langle x, 3@4 \rangle$$

We now have that  $p_1$  provides the precondition for  $p_2$  and likewise  $p_2$  provides the precondition for  $p_1$ .

#### 2.3.2 The Java Memory Model

The Java memory model, released as JSR-133: The Java Memory Model and Thread Specification by Pugh, Adve and Lea (2011), describes the permitted behaviour of concurrent programs running on the Java Virtual Machine using the *Thread* class. The goal of the model is to provide defined behaviour for all well-typed programs which use *Thread*, including those with data races, while simultaneously allowing existing optimisations and preserving type safety. Similar to Promising, it is a per-execution model which begins evaluating programs in syntactic order and progressively justifies out-of-order accesses. Unlike Promising, however, it correctly forbids justification cycles but as a collateral forbids optimisations which should be permitted.

The model divides program variables into local variables, which can only be accessed within a thread, and global variables. An assignment to a local variable from a global variable is a *read*. An assignment to a global variable from a local variable is a *write*. Any operations which only impact local variables and cannot impact global ones are handled by the existing intra-thread semantics for Java, and largely ignored by the memory model. It includes a handful of other special actions not given in detail here, but used for synchronisation operations and special circumstances such as interrupts and exceptions.

#### **Definitions**

The operations performed by a program are called actions, and given by a tuple

#### Where:

- $\bullet$  t identifies the thread in which the action occurs

- k describes the kind of the action, which will be one of the categories mentioned above (for our purposes, read or write)

- v gives the variable referenced by an action

- u is a unique identifier for this action

A write has a static value, described by the function V(w). The value observed by a read within a particular execution is described by the value of its corresponding write, where W(r) gives the write being observed and V(W(r)) gives the resulting value. Note that it is impossible

to define a read which does not have a corresponding write. All programs must begin with a series of initialising writes, which usually set all global values to 0.

An execution consists of a set of these actions, the program which generates them, and a series of relations over them. Executions are written as a tuple

$$(P, A, \sqsubseteq, \xrightarrow{so}, W, V, \xrightarrow{sw}, \xrightarrow{hb})$$

Where:

- P is the program

- A is a set of actions

- <u>□</u> is the *program order* relation, which is the order in which actions occur in the program text (note that this is a partial order, as actions from one thread are not <u>□</u> before or after actions in a different thread)

- $\xrightarrow{so}$  is the *synchronisation order* relation, which is a total order over all synchronisation actions in A

- ullet W and V are the observed write and value functions

- $\xrightarrow{sw}$  is the *synchronises-with* relation, which is not used in the examples given here but, in the full model, orders various synchronisation primitives and special actions

- $\xrightarrow{hb}$  is the *happens-before* relation, which is the transitive closure of program order and synchronises-with:  $(\sqsubseteq \cup \xrightarrow{sw})^+$

The specification is careful to note that two events being related by  $\xrightarrow{hb}$  does not cause them to always be performed by the JVM in this order. Instead, all executions must preserve a property called *happens-before consistency*.

Happens-before consistency requires that, if we have a read r which observes write w (such that W(r) = w), the following must hold:

- The write w is not  $\xrightarrow{hb}$ -after r

- There is no write w' to the same variable in A such that  $w \xrightarrow{hb} w' \xrightarrow{hb} r$

Not all happens-before consistent executions are permitted by the model. It also requires that one can define an order in which events are *committed*, using a somewhat operational-style construction.

An execution E can be restricted to a *sub-execution*  $E_i$  by taking a subset of the actions and restricting all relations in E to this subset. The actions in  $E_i$  are written  $A_i$ , the functions V and W as  $V_i$  and  $W_i$ , and the relations likewise disambiguated by subscript. For each such execution we define a set of *committed* actions  $C_i$  such that  $C_i \subseteq A_i$ .

The values written by all committed writes (meaning writes in  $C_i$ ) must be the values written in the final execution, but we do *not* require this for values in  $A_i \setminus C_i$ . The writes observed by reads in the *previous* commit set  $C_{i-1}$  must be equal to the writes observed by the complete execution, but likewise we do *not* require this for writes in  $A_i \setminus C_i$  or in  $C_i \setminus C_{i-1}$ .

$$V_i|_{C_i} = V|_{C_i}$$

$$W_i|_{C_{i-1}} = W|_{C_{i-1}}$$

This means that we are allowed to "swap" the value observed by a read when we move it from  $A_{i-1}$  to  $C_i$ , but we cannot swap again afterwards. This is necessary to observe potentially racy values, because we also require that whenever we initially add a read to our execution, it must observe a value from a write which is guaranteed to be observable by being  $\xrightarrow{hb}$ -before it. However, the write it observes in the final execution must also have been added to a previous commit set even if this is not the write it observes in the execution  $E_i$ .

For any read

$$r$$

in  $A_i \setminus C_{i-1}$ , we have  $W_i(r) \xrightarrow{hb_i} r$ .

For any read  $r$  in  $C_i \setminus C_{i-1}$ , we have  $W_i(r) \in C_{i-1}$  and  $W(r) \in C_{i-1}$ .

We require that the union of all these commit sets is equal to the action set of our final execution:  $A = \cup (C_0, C_1, ...)$ . If the set A is finite, then we will arrive at some final  $C_n = A$ . If A is not finite, then the infinite union of  $C_i$  must be equal to A.

This is best demonstrated by example.

#### Reordering by Example

0:

$$x = 0$$

0:  $y = 0$

1:  $r1 = x$ ; | 3:  $r2 = y$ ;

2:  $y = 1$ ; | 4:  $x = r2$ ;

Programs are assumed to begin with all variables set to 0. As each read requires a corresponding write, a series of initialising writes are included at the start of the program and denoted by the

line number 0. For ease of reading, the line numbers are used here as identifiers. This is not mandated by the standard, as action identifiers need only be unique for each action performed by an execution and do not need to be unique for each potential action in the program, but it clarifies the relationship between actions and program syntax.

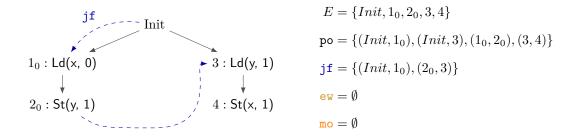

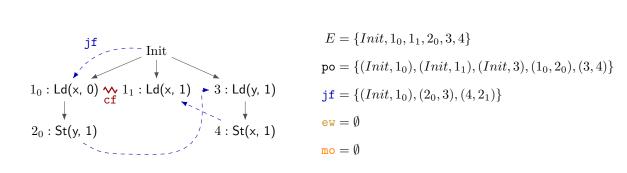

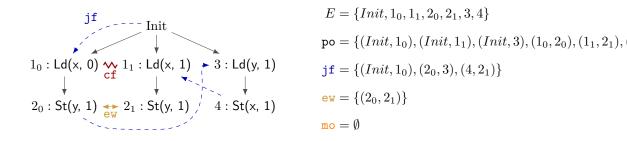

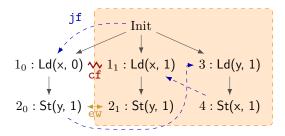

This code contains a data race: there's no synchronisation between the write on line 2 and the read on line 3, so the read may either observe the write of 1 or the initial write of 0. Due to the reorderings described in section 2.2.1, the outcome r1 = r2 = 1 is allowed here. The write on line 2 commits before the read on line 3, and the write on line 4 before the read on line 1. Using line numbers as action identifiers, this gives us the following components for our final execution E:

$$A = \{0, 1, 2, 3, 4\}$$

$$V(2) = 1 \quad V(4) = 1$$

$$W(1) = 4 \quad W(3) = 1$$

Our first execution  $E_1$  must be a well-formed execution of the program, which means every read must have a corresponding write and the action set must correspond to an acceptable execution of each thread under the thread-local semantics. Since the initial commit set  $C_0$  is the empty set, every read in the execution must be in  $A_1 \setminus C_0 = A_1$ , which means that all r must satisfy the requirement  $W_1(r) \xrightarrow{hb_1} r$ . The only writes we can observe at lines 1 and 3 are the initialising writes of 0, as the other writes are in different threads and do not synchronise before their respective reads.

We then create the commit set  $C_1 = \{0, 2\}$ . This means we have committed the initial writes, as well as the write of 1 to y on line 2. We don't want to commit line 4 yet, because its value in our final execution is not the value we observe here. As long as 4 isn't in  $C_1$ , then  $V_1(4)$  and V(4) can differ.

The program text in Fig. 10 has been annotated with the  $W_1$  function shown as dashed green arrows and  $C_1$  highlighted in light green.

$$A_1 = \{0, 1, 2, 3, 4\}$$

$V_1(2) = 1$

$V_1(4) = 0$

$V_1(4) = 0$

$V_1(5) = 0$

$V_2(5) = 0$

$V_3(6) = 0$

$V_4(6) = 0$

$V_1(6) = 0$

$V_1(6) = 0$

$V_1(6) = 0$

$V_2(6) = 0$

$V_3(6) = 0$

$V_3(6) = 0$

$V_4(6) = 0$

$V_1(6) = 0$

$V_1(6) = 0$

$V_2(6) = 0$

$V_3(6) = 0$

$V_3(6) = 0$

$V_4(6) = 0$

$V_1(6) = 0$

$V_1(6) = 0$

$V_2(6) = 0$

$V_3(6) = 0$

$V_4(6) = 0$

$V_4(6$

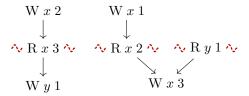

Figure 10: Execution  $E_1$  and commit set  $C_1$

The next event we want to commit is 3, so  $C_2 = \{0, 2, 3\}$ . We can't initially set  $W_2(3) = 2$ , as in our final execution, because reads outside of  $C_{n-1}$  can only observe writes which are  $\xrightarrow{hb}$  before them. The only such event for line 3 is the initialising write of 0. We will be allowed to change the write being observed in our next execution, but for now our only option is to set  $W_2(3) = 0$ . We now need to verify that  $W_2(3) \in C_1$  and  $W(3) \in C_1$ . This clearly holds, since both 0 and 2 are in  $C_1$ .

In Fig.11, the events we committed in the set  $C_1$  are shown in a darker green.

$$A_1 = \{0, 1, 2, 3, 4\}$$

$V_1(2) = 1$

$V_1(4) = 0$

$V_1(3) = 0$

$0: x := 0;$

$0: y := 0;$

$0: y := 0;$

$1: r1 := x;$

$2: y := 1;$

$1: r2 := y;$

$4: x := r2;$

Figure 11: Execution  $E_2$ , which is the same as  $E_1$ , and commit set  $C_2$ .

Moving on to  $C_3$ , the next event we want to commit is the write on line 4. This gives us  $C_3 = \{0, 2, 3, 4\}$ . Because 3 is no longer in  $A_i \setminus C_{i-1}$ , we no longer need it to observe a write that comes before it in  $\xrightarrow{hb}$ . In addition, we now need to ensure that  $W_3(3)$  is the same as W(3): it must be true that  $W_3|_{C_2} = W|_{C_2}$ . We swap from  $W_2(3) = 0$  to  $W_3(3) = 2$ , and this changes the value written on line 4 from 0 to 1. Having not yet committed 4, this value swap is permitted.

Figure 12: Execution  $E_3$  and commit set  $C_3$

Finally, we add line 1 to the commit set  $C_4 = \{0, 1, 2, 3, 4\}$ . Note again that we can't have  $W_4(1) = 4$ , because we're still restricted to writes which are  $\xrightarrow{hb}$ -before 4. This isn't a problem though, as we're still allowed to swap which read we observe in the step between executions  $E_4$  and E as we did with the previous read between  $E_2$  and  $E_3$ .

$$A_4 = \{0, 1, 2, 3, 4\}$$

$V_4(2) = 1$

$V_4(4) = 1$

$V_4(4) = 0$

$V_4(3) = 2$

$V_4(4) = 0$

$V_4(5) = 0$

$V_4(6) = 0$

$V_4(6$

Figure 13: Execution  $E_4$  and commit set  $C_4$

Figure 14: Execution E with all actions committed

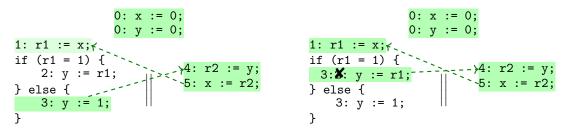

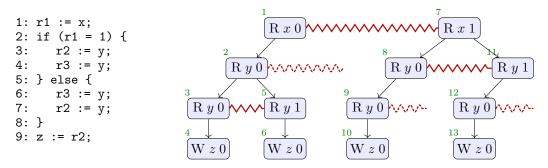

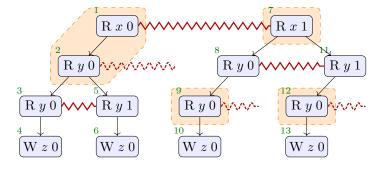

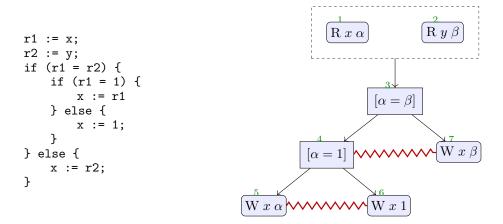

#### Branch Elimination by Example

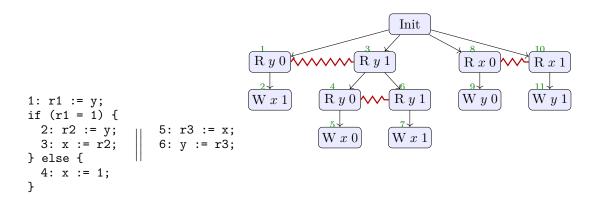

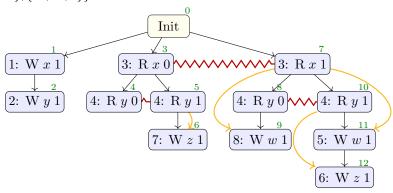

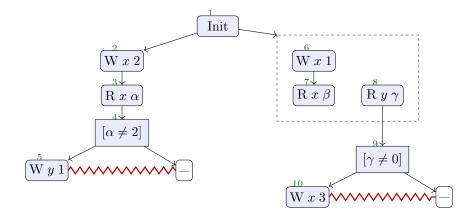

The model is also able to represent optimisations in the presence of branches. We can illustrate this by adding a branch statement to the previous program and looking for the same execution:

```

1: r1 := x;

if (r1 = 1) {

2: y := r1;

} else {

3: y := 1;

}

```

The write on line 2 is always going to have value 1, thus we should be able to observe an execution in which y := 1 happens above the guard.

We initially proceed as before, beginning with the write of the constant and propagating this value to the second thread, then copying it into  $\mathbf{x}$ .

$$C_1 = \{0,3\}$$

$C_2 = \{0,3,4\}$   $C_3 = \{0,3,4,5\}$   $C_4 = \{0,1,3,4,5\}$

Figure 15: Commit sets  $C_4$  and  $C_5$

We now want to change from observing 0 at line 1 to observing 1. This means that the thread-local semantics will no longer allow us to execute line 3, and we must instead execute line 2. Recall, however, that the unique identifier corresponding to an action is arbitrary. We can perform an action at line 2 which is identical to line 3 simply by declaring that the identifiers are the same, since they are the same type of access to the same location with the same associated value. This results in our final commit set  $C_5 = \{0, 1, 2, 4, 5\}$ .

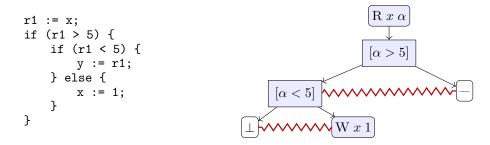

#### Failure to Permit Known Optimisations

This model has shown to be too restrictive with respect to the actual behaviour of the Hotspot compiler by Ševčík and Aspinall (2008). The following sequence of optimisations has been observed in practice, but results in behaviours that are forbidden by the model:

```

1: r1 := y;

if (r1 = 1) {

2: r2 := y;

3: x := r2; \rightarrow 1: r1 := y; \rightarrow 1: x := 1;

} else {

2: x := 1; \rightarrow 2: r1 := y;

4: x := 1;

```

To work out how and why this is forbidden, let us first create a context that can distinguish the first program from the last:

```

1: r1 := y;

if (r1 = 1) {

2: r2 := y;

3: x := r2; | 5: r3 := x;

6: y := r3;

} else {

4: x := 1;

```

If the reordering between the read from y and the write to x is permitted, then we can observe an execution where line 1 observes the value 1 from the write at line 6, while the read at line 5 observes the write on line 3, hoisted above the branch.

$$0: x := 0; \\ 0: y := 0;$$

$$1: r1 := y; \\ 1: r1 := y; \\ 1: r1 := y; \\ 2: r2 := y;$$

$$3: x := r2; \\ 1: r3 := x;$$

$$3: x := r3;$$

$$4: x := 1;$$

As before, we need to commit the hoisted write first in order to observe its value later, and then swap branch after altering the value observed at line 1. We take the following path through the program:

$$C_1 = \{0,4\}$$

$C_2 = \{0,4,5\}$   $C_3 = \{0,1,4,5,6\}$

In order to let line 1 read from line 6 and swap branch, we need to ensure that line 3 writes a value of 1 to match line 4. As before, we must invoke the thread-local semantics to propagate the value in r2. This is a problem: line 2 can only observe the value of 0 until the commit set after this one. We need to have at least one set in which it takes its value from a write which is  $\stackrel{hb}{\longrightarrow}$ -before it, and the only such write is the initialising write of 0. On the other hand, this is the last commit step where we can change the value we observe at line 1. If we take another step while reading from the initialisation write, then our final execution must also read from the initialisation write here.

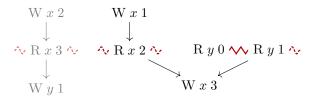

Because we can't read 1 into  $\mathbf{r2}$  in the next commit step, line 3 cannot perform the already-committed write of 1 to x created at line 4. It would need to spend at least one commit step writing 0, which changes the commit set. This is illustrated in Fig. 16.

```

0: x := 0;

0: y := 0;

1: r1 := y;

if (r1 = 1) {

2: r2 := y;

3: x := r2;

} else {

4: x := 1;

```

Figure 16: Line 5 expects to see value 1, but the left thread is copying value 0 into x.

The main issue here is a failure to recognise that not all reads in a program will actually take their value from a write. There is a sequentially permissable optimisation which removes line 2 entirely, and propagates the value 1 into all in-scope references to r3. The model, meanwhile, is insensitive to the guarantees from the guard condition.

#### 2.4 Moving Away From Trace-Based Semantics

The JMM and Promising have a particular feature in common which underlies both of their failures. They want to determine which values a read could potentially observe by starting at a sequentially consistent trace, then using a set of modification steps over that trace in order to change the observed value. Java does this execution-by-execution via the commit sets, while Promising does this step-by-step operationally via promises. In either semantics, the values a read is allowed to observe are given by the set of writes which "might" happen before it, and the machinery of the model is dedicated to filling that set prior to executing the read and continuing in the program. This causes the JMM to fail in cases where a read cannot observe the desired value within a single commit step, and Promising to fail in cases where earlier operational steps make assertions about program invariants that aren't preserved at later steps.

In either case, the potential ordering of statements in one thread is strongly dependent on any other threads running in parallel. Intra-thread reordering operations are never represented explicitly, thus optimisations which will always be permitted in one thread are not always visible to the semantics. This gives rise to degenerate contexts in which an intra-thread reordering operation which should be observable can be blocked by one component of a parallel thread but should be observed by another, as in the  $\mathbf{x}:=\mathbf{y}$  context for the JMM (in which the load from x observes a reordered write of 1 and the store to y blocks the reordering). It can also cause a semantics to allow a reordering that is sequentially unsound, such as the removal of the guard in if  $(\mathbf{r}1 := 0)$   $\{\mathbf{x} := 3\}$  allowed by the Promising semantics.

If the link between these is the requirement to validate the plausibility of the input to a semantic step prior to executing it and allowing the output, then we might propose a semantics which avoids this entirely. We instead move to validate every choice at a point of nondeterminism – be it the ordering of events or the value observed by a read – from the context of the entire program, rather than attempting during interpretation to construct a program fragment which might be plausibly before it.

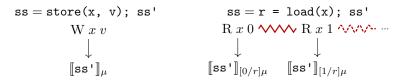

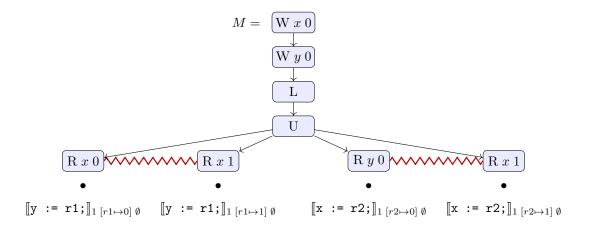

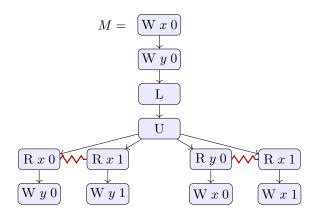

Rather than the "permit, then proceed" approach shown here, other models take a "proceed, then permit" approach. However, this requires an overview of potential executions which is substantially more modular than a constructed set of execution traces. The MRD model uses event structures to represent the control and data flow within a program explicitly, which allows it to represent a theoretical execution without needing to validate beforehand that every step of the execution may happen given prior knowledge of the program.

In the next section we introduce event structures, and give an overview of two other memory models which use them to make decisions about program execution.

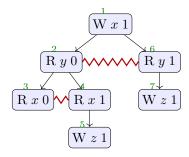

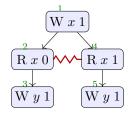

#### 2.4.1 Event Structures

Event structures were introduced by Nielsen, Plotkin and Winskel (1981) to combine various formalisms for the evolution of a computational state given internal computational steps and external inputs. Several memory models have already been proposed, by Ševčík and Aspinall (2008), Jeffrey and Riely (2016), Lahav et al. (2017), and Chakraborty and Vafeiadis (2019), which use event structures to describe concurrent programs.

An *event*, at its most basic, has three properties: it is atomic, it has a set of events which must occur before it can begin, and it has a set of events with which it cannot simultaneously occur. In the context of a program running on an abstract machine, any operational step can be considered an "event". In MRD, we consider only global memory accesses and fences to be events, while any arithmetic operation over local variables is invisible.

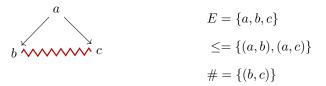

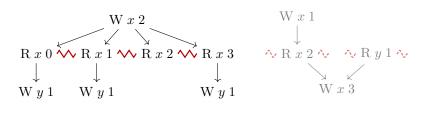

Event structures are written as a tuple  $(E, \leq, \#)$ , where E is the set of events,  $\leq \subseteq E \times E$  is a causality relation, and  $\# \subseteq E \times E$  is a conflict relation. These are commonly presented as graphs, where  $\leq$  is used as a parent-child relation.

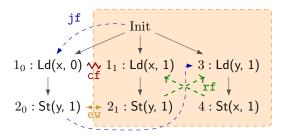

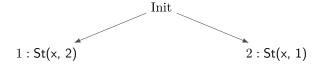

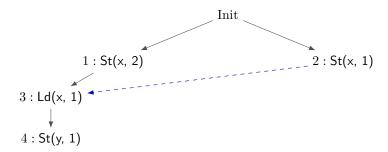

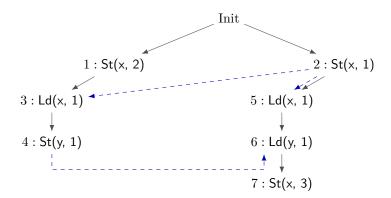

Figure 17: A graph representation (left) and set representation (right) of the same event structure

If  $e_1 \leq e_2$ , then  $e_2$  cannot occur until  $e_1$  has finished. If  $e_1 \# e_2$ , then  $e_1$  and  $e_2$  cannot both happen.

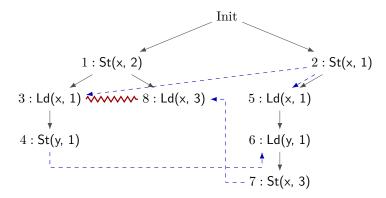

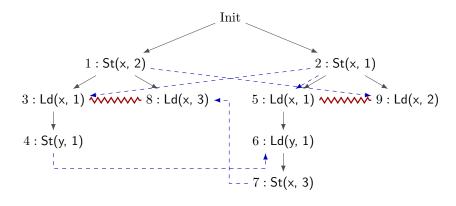

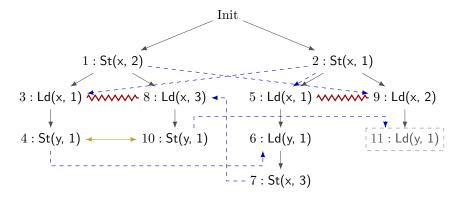

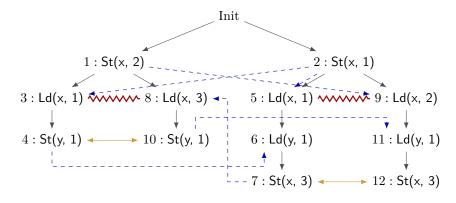

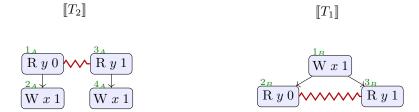

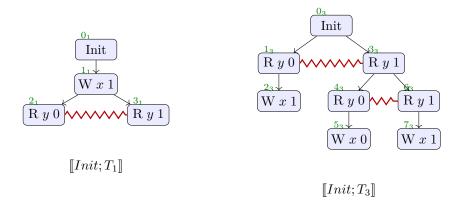

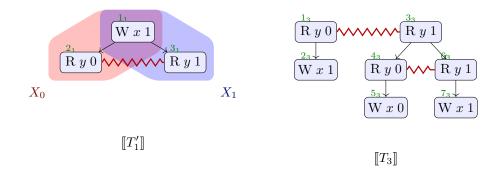

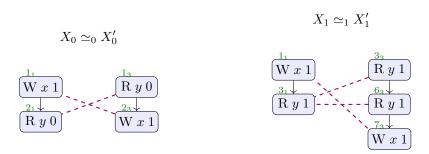

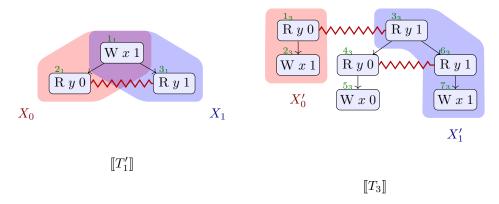

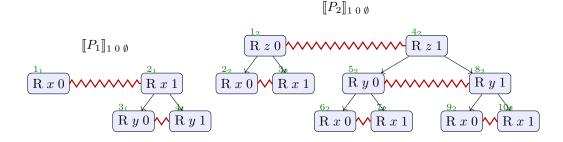

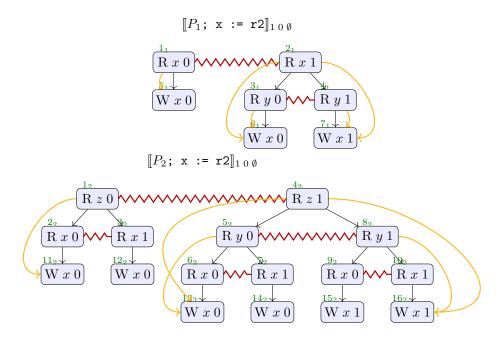

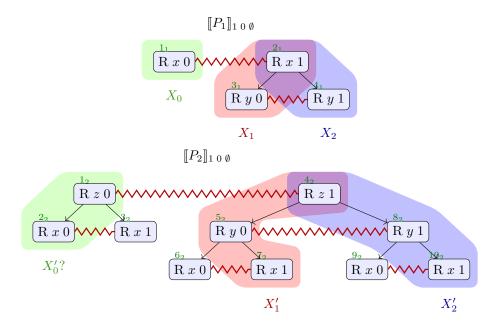

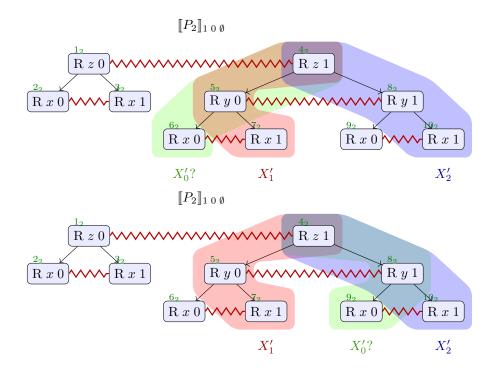

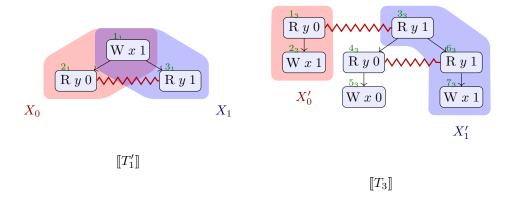

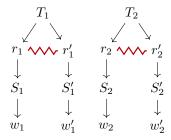

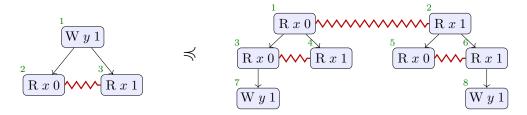

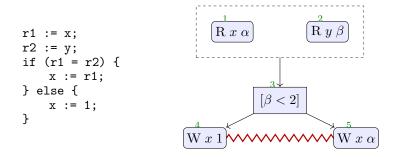

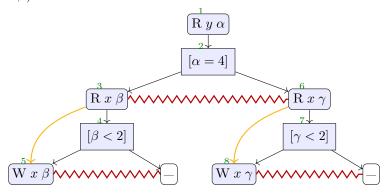

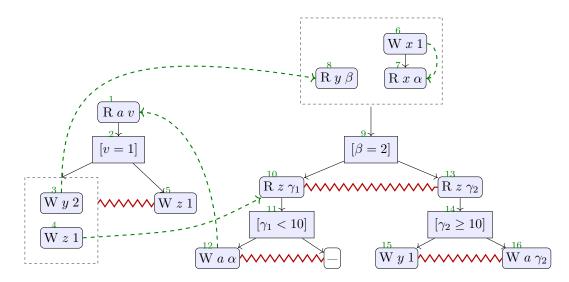

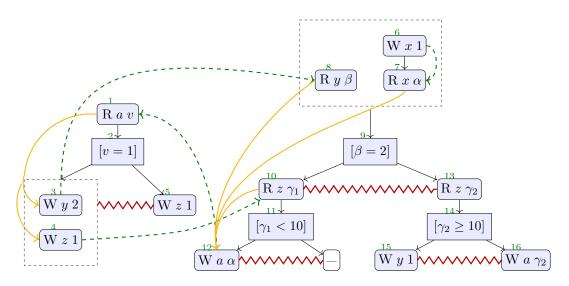

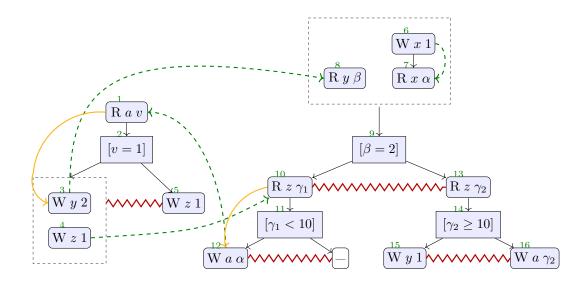

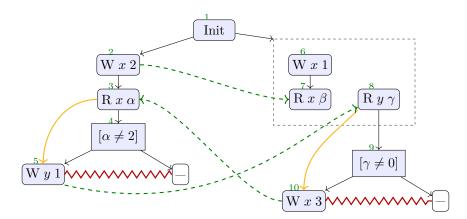

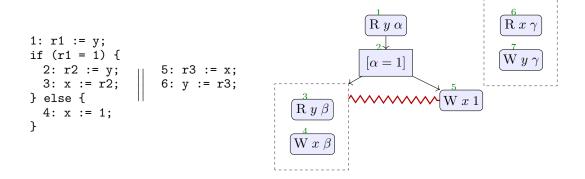

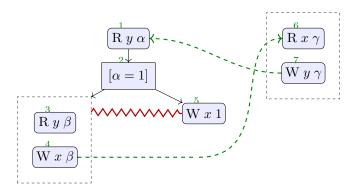

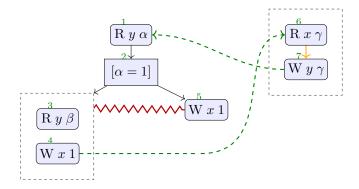

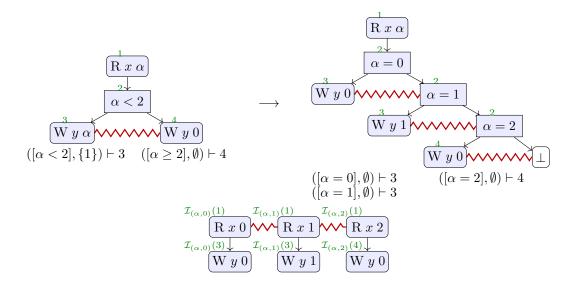

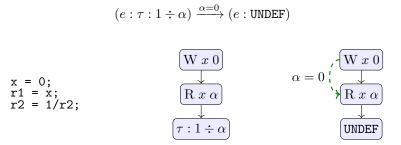

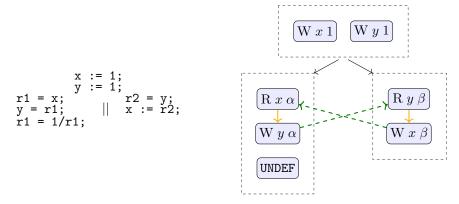

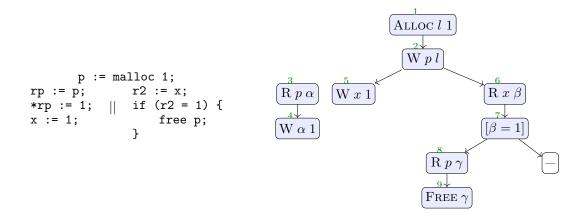

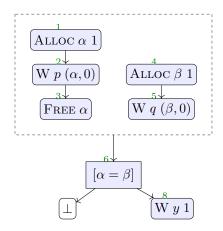

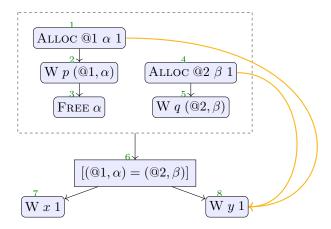

When considering events as memory accesses and event structures as programs, we can use  $\leq$  to denote the syntactic order in which these accesses are written. If line 1 causes event  $e_1$  and line 2 causes event  $e_2$ , then we can assert that  $e_1 \leq e_2$ . This loosens the interpretation of the  $\leq$  relation from "causality" to "ordering" – there doesn't need to be any causal relationship between the events being ordered, but nonetheless we would expect them to occur in the order given.