## **Kent Academic Repository**

Glover, R. J. (1985) *An adaptive computing system.* Doctor of Philosophy (PhD) thesis, University of Kent.

## **Downloaded from**

https://kar.kent.ac.uk/94371/ The University of Kent's Academic Repository KAR

## The version of record is available from

https://doi.org/10.22024/UniKent/01.02.94371

#### This document version

**UNSPECIFIED**

**DOI** for this version

#### Licence for this version

CC BY-NC-ND (Attribution-NonCommercial-NoDerivatives)

#### **Additional information**

This thesis has been digitised by EThOS, the British Library digitisation service, for purposes of preservation and dissemination. It was uploaded to KAR on 25 April 2022 in order to hold its content and record within University of Kent systems. It is available Open Access using a Creative Commons Attribution, Non-commercial, No Derivatives (https://creativecommons.org/licenses/by-nc-nd/4.0/) licence so that the thesis and its author, can benefit from opportunities for increased readership and citation. This was done in line with University of Kent policies (https://www.kent.ac.uk/is/strategy/docs/Kent%20Open%20Access%20policy.pdf). If you ...

#### Versions of research works

#### **Versions of Record**

If this version is the version of record, it is the same as the published version available on the publisher's web site. Cite as the published version.

### **Author Accepted Manuscripts**

If this document is identified as the Author Accepted Manuscript it is the version after peer review but before type setting, copy editing or publisher branding. Cite as Surname, Initial. (Year) 'Title of article'. To be published in *Title of Journal*, Volume and issue numbers [peer-reviewed accepted version]. Available at: DOI or URL (Accessed: date).

## **Enquiries**

If you have questions about this document contact <a href="ResearchSupport@kent.ac.uk">ResearchSupport@kent.ac.uk</a>. Please include the URL of the record in KAR. If you believe that your, or a third party's rights have been compromised through this document please see our <a href="Take Down policy">Take Down policy</a> (available from <a href="https://www.kent.ac.uk/guides/kar-the-kent-academic-repository#policies">https://www.kent.ac.uk/guides/kar-the-kent-academic-repository#policies</a>).

## AN ADAPTIVE COMPUTING SYSTEM

by

R. J. GLOVER

A Thesis Submitted for the Degree

of Doctor of Philosophy at the

University of Kent at Canterbury

1978

## ACKNOWLEDGEMENTS

I wish to acknowledge the financial support provided by the Science Research Council for this project.

I express my sincere thanks to Professor I. Aleksander for his guidance and encouragement.

I would like to thank the Staff of the Electronics Laboratories of the University of Kent for providing the research facilities and the Staff of the Department of Electrical Engineering and Electronics at Brunel University for allowing the research to continue.

I am particularly indebted to all my colleagues and friends for their discussions that set the seed of many ideas.

Thanks must also be given to John Ryan, John Husband and Ian Fisher who have helped in the arduous task of constructing the hardware.

Finally, I would like to thank Clare Fisher for the care and concern she has taken in the typing of this thesis.

R. J. Glover

Brunel University

Uxbridge

## ABSTRACT

Several natural systems are comprised of networks of similar cells or processes which possess an intelligence or overall stability when interacting among themselves. Well known though not fully understood examples are the central nervous system or the activity of genes during cell replication.

Theoretical studies of network systems have been restricted by complexity to networks of cells possessing linear properties. Computer simulation of networks with non-linear cells is impractical because of the very large number of internal states possessed by networks of non-trivial size.

This thesis presents a practical approach to a system capable of modelling some networks using Random Access Memory (R.A.M.) circuits. Interconnections may be arbitarily specified between the address inputs and data outputs of R.A.M. elements and external network data inputs and outputs. The subsequent output state-activity of the network may be "adapted" according to external data using the R.A.M. write enable inputs.

A custom made R.A.M. integrated circuit is described which has provision for the simultaneous setting and resetting of its store. This is used in a mini-computer controlled network of 1,280 R.A.M.'s with interconnections specified by software.

An interactive high-level language is described that simplifies the specification and manipulation of networks. Its use is illustrated by programs for a single-layer classifier and a feedback network with natural clustering properties.

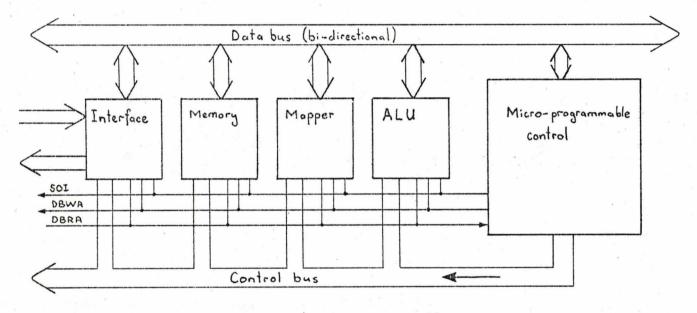

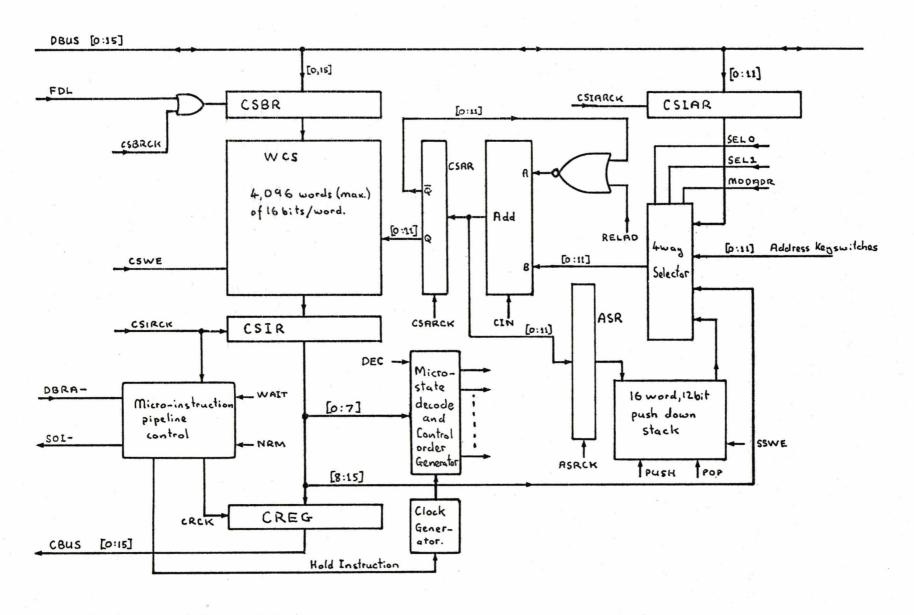

Finally the optimisation of the programmable network - interconnections and the execution of the high-level network language is presented using hardware micro-program controlled modules.

It is concluded that the system may be useful in a range of activities such as the design of Read Only Memory R.O.M. based pattern recognisers to testing hypotheses regarding neural networks.

## CONTENTS

## Acknowledgements

Abstract

| ~~~   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CHAP  | TER 1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -    |

| Intro | oduction a | and Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.0   | Introduc   | tion and Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1    |

| 1.1   | The Orga   | nisation of a Cellular Adaptive Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3    |

| 1.2   | Systems    | Considerations for an Adaptive Cellular Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3    |

| 1.3   | Artifici   | al Intelligence: Aims for Adaptive Processing Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4    |

| 1.4   | Neural M   | fodels and Learning Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7    |

|       | 1.4.0      | Neuron Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8    |

|       | 1.4.1      | Pattern Recognition by Perceptrons and<br>Learning Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11   |

|       | 1.4.2      | Models of Some Neural Pathways                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13   |

|       | 1.4.3      | Single-Layer Learning Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15   |

|       | 1.4.4      | Networks with Feedback Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19   |

|       | 1.4.5      | Stability and Networks with Feedback<br>Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21   |

|       | 1.4.6      | Other Feedback Network Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23   |

| 1.5   | A Commer   | at entremental and the second | 25   |

| 1.6   | Micro-pr   | rogramming Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26   |

|       | 1.6.0      | The Development of Micro-Programmed<br>Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28   |

|       | 1.6.1      | Writable Control Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31   |

|       | 1.6.2      | Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32   |

|       | 1.6.3      | The Execution of High Level Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34   |

|       | 1.6.4      | Micro-programming and Modular Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36   |

| 1.7   | Concludi   | ng Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37   |

|       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| CHAP  | TER 2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| The I | Design and | Fabrication of an Integrated Circuit Adaptive Logic Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 2.0   | Adaptive   | Logic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39   |

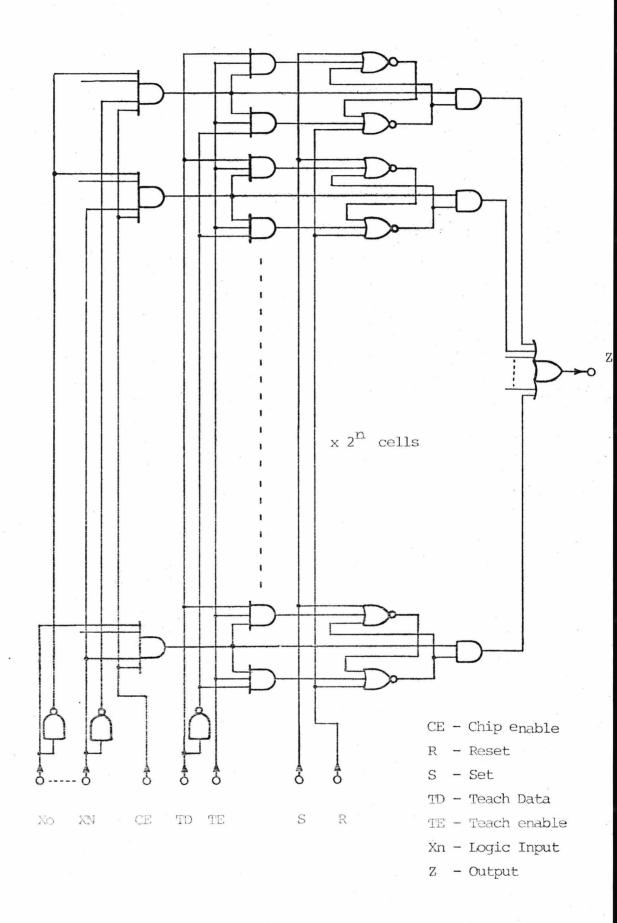

|       | 2.0.0      | S.L.A.M.'s and R.A.M.'s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41   |

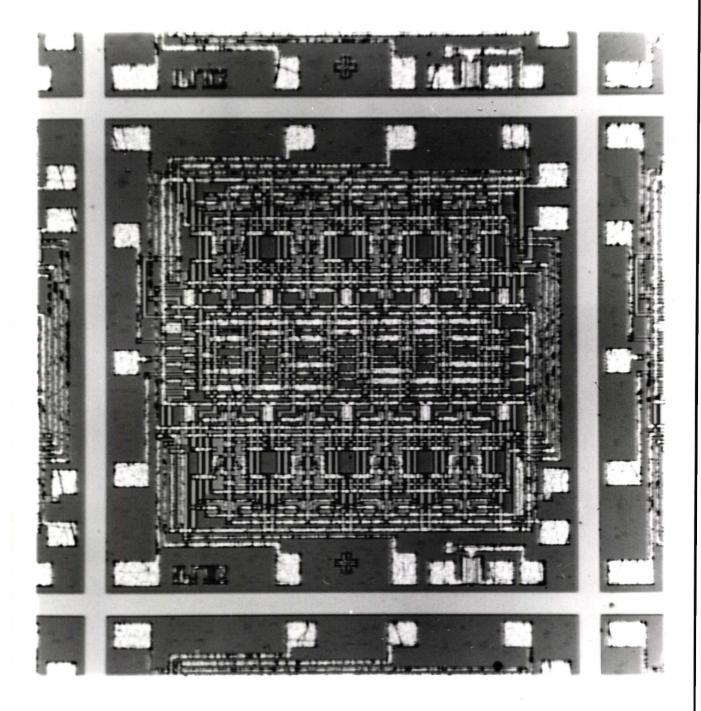

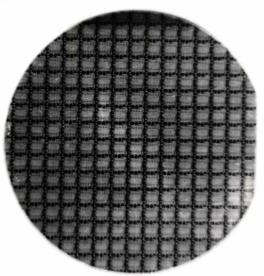

| 2.1   | The Deve   | elopment of S.L.A.M16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45   |

|       | 2.1.0      | Specification of S.L.A.M16                                    | 45   |

|-------|------------|---------------------------------------------------------------|------|

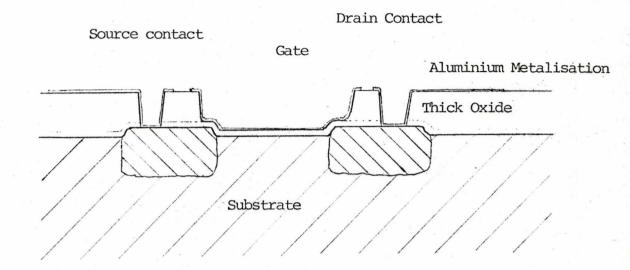

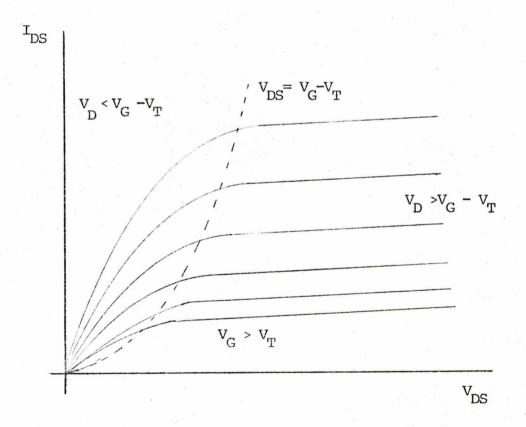

|       | 2.1.1      | The M.O.S. Process Used for S.L.A.M16                         | 47   |

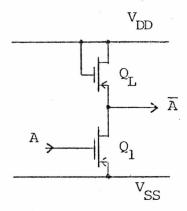

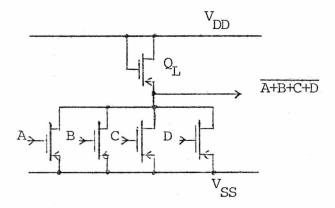

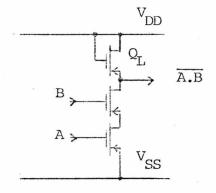

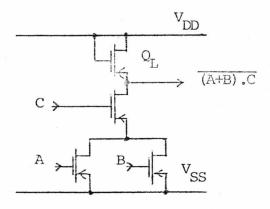

|       | 2.1.2      | Logic Design Using M.O.S. Transistors                         | 50   |

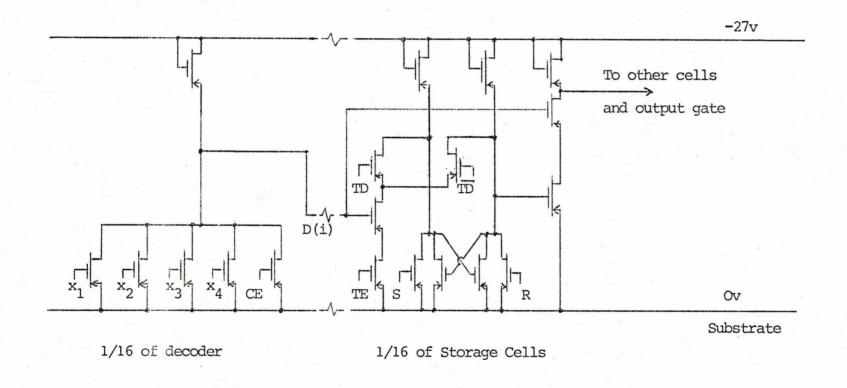

| 2.2   | Circuit    | Design of S.L.A.M16                                           | 54   |

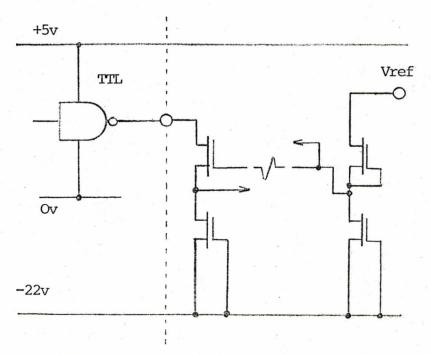

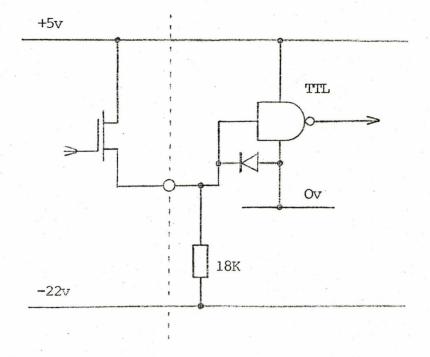

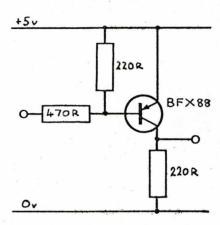

|       | 2.2.0      | Interface Circuitry                                           | 56   |

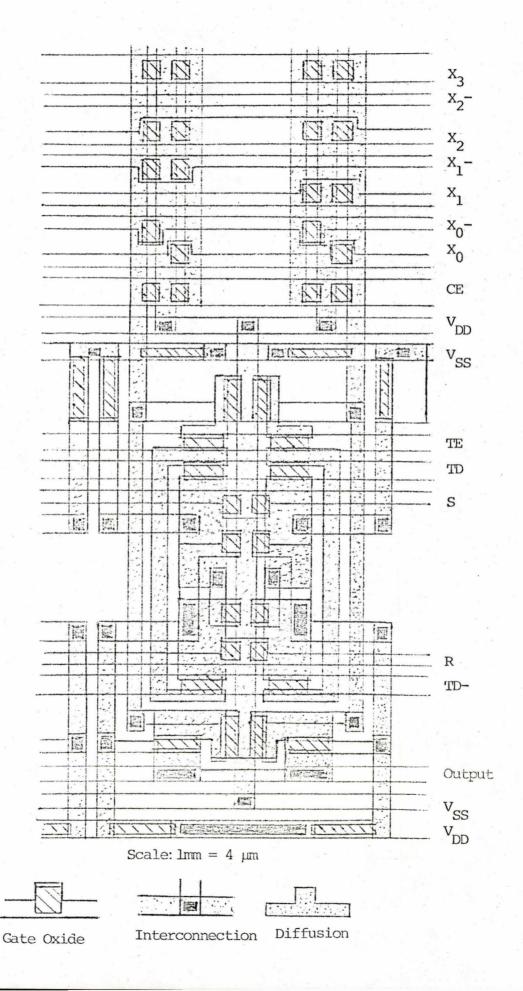

|       | 2.2.1      | Photo-mask Implementation for S.L.A.M16                       | 59   |

| 2.3   | Device T   | esting                                                        | - 61 |

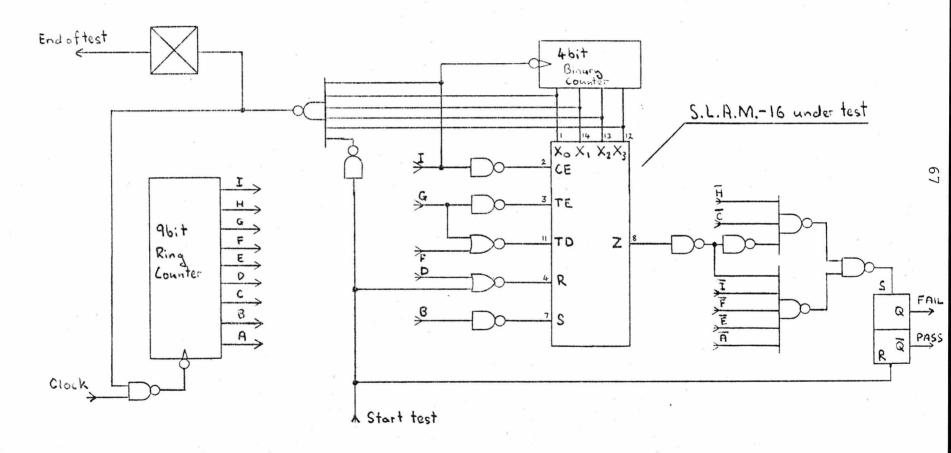

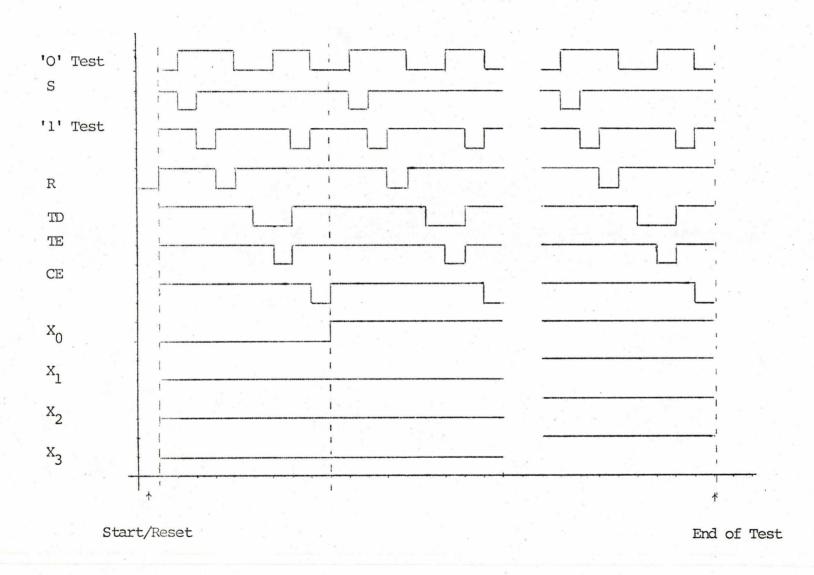

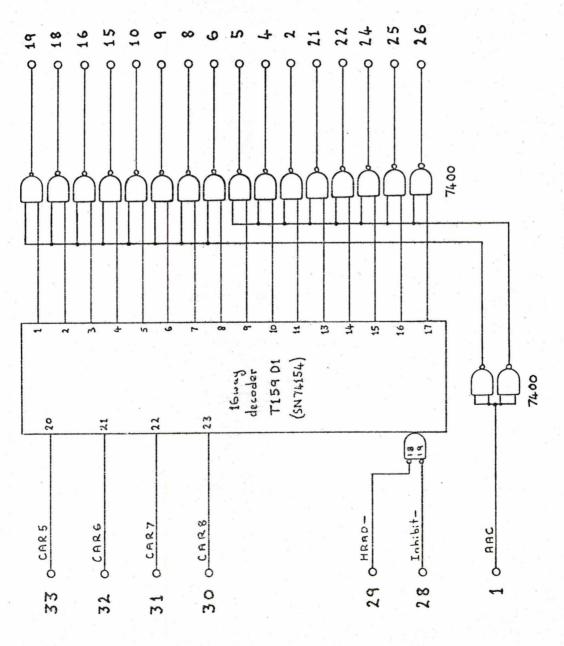

|       | 2.3.0      | Test Sequence Design                                          | 64   |

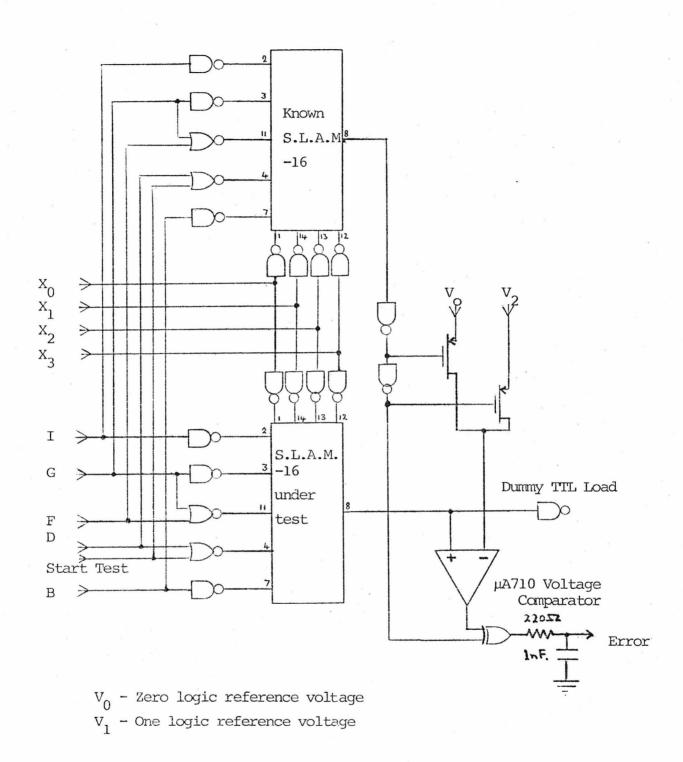

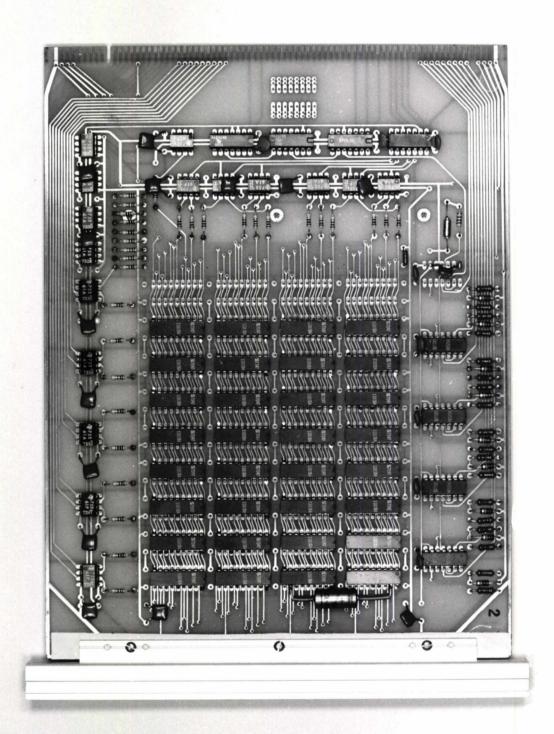

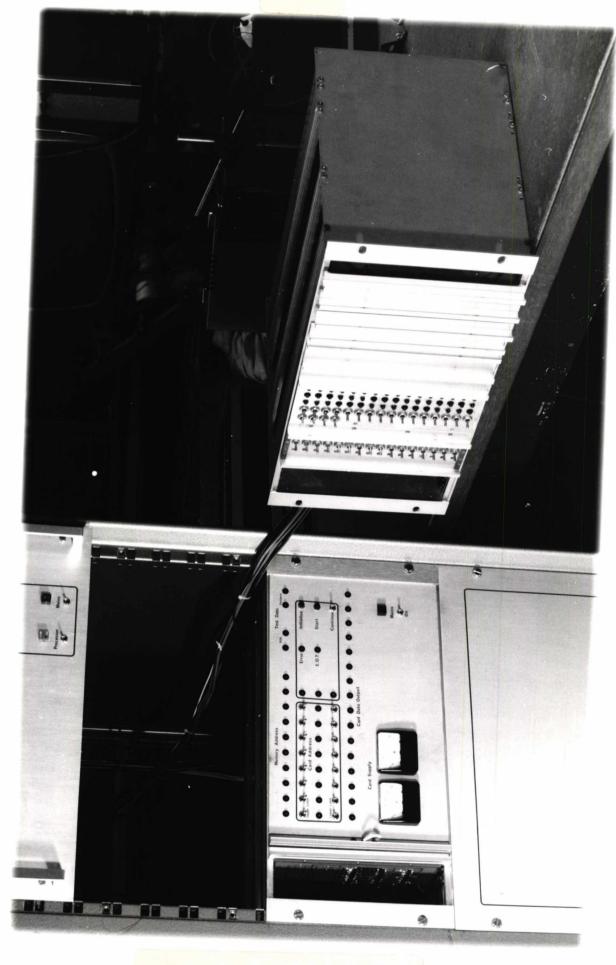

|       | 2.3.1      | Test Equipment Design                                         | 65   |

|       | 2.3.2      | Performance of Produced S.L.A.M16 Devices                     | 70   |

| 2.4   | A Discus   | sion                                                          | 72   |

|       |            | 나를 되는 이 그릇하는 내용하고 있다. 이 뭐 뭐 그리가 이 속에서 되었습니다.                  |      |

|       |            |                                                               |      |

|       |            |                                                               |      |

| CHAP  | TER 3      | 어린 병원 등 등 등 생생님 아무리는 사람이 되었다. 그는 나를                           |      |

|       |            |                                                               |      |

| The I | Design and | Construction of Learning Network Hardware Using S.L.A.M1      | 6    |

| 2 0   |            |                                                               | 75   |

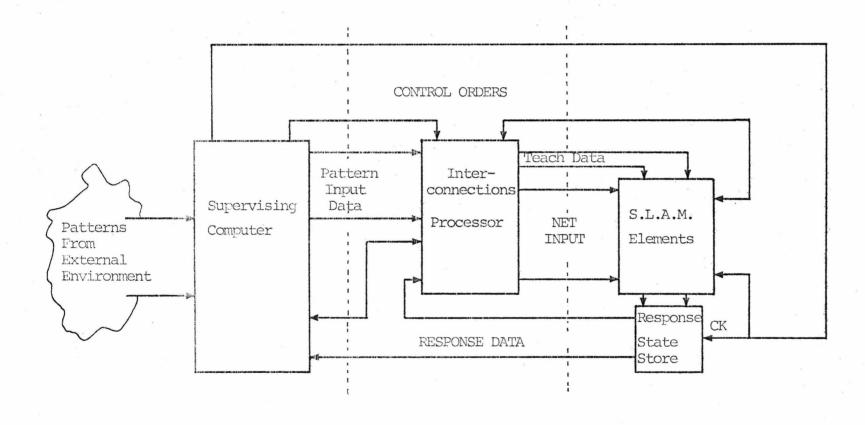

| 3.0   | Introduc   |                                                               | 75   |

| 3.1   |            | System Design Considerations                                  | 75   |

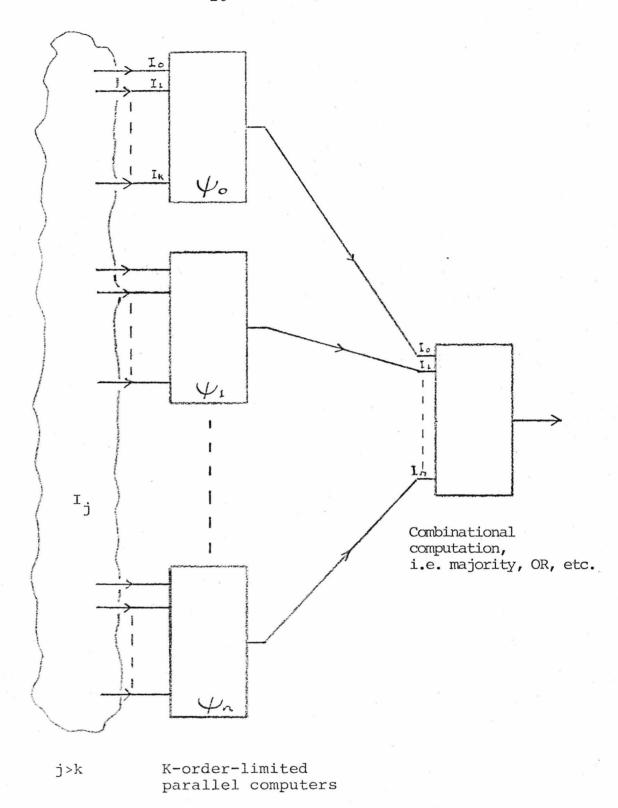

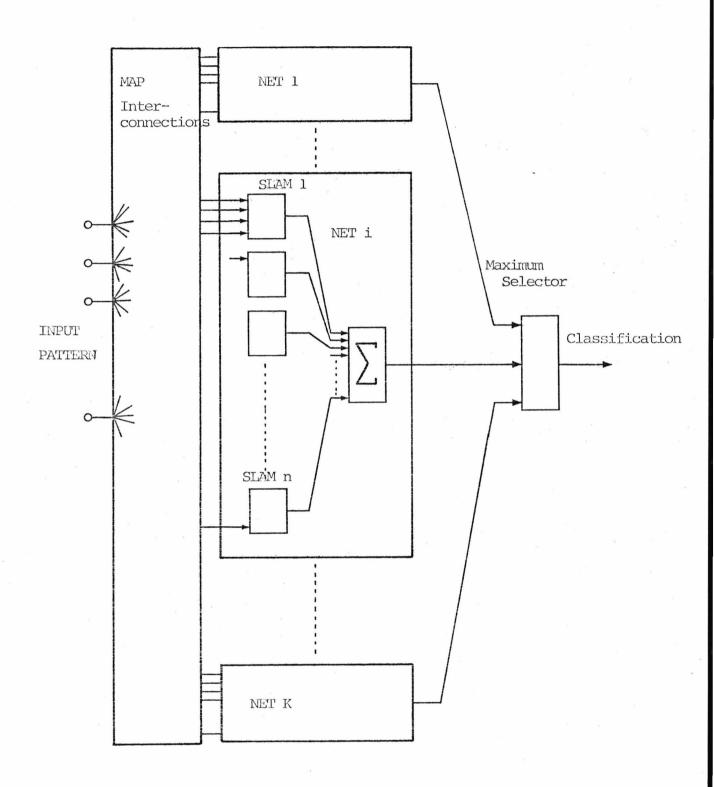

|       |            | Single-layer Networks                                         | 76   |

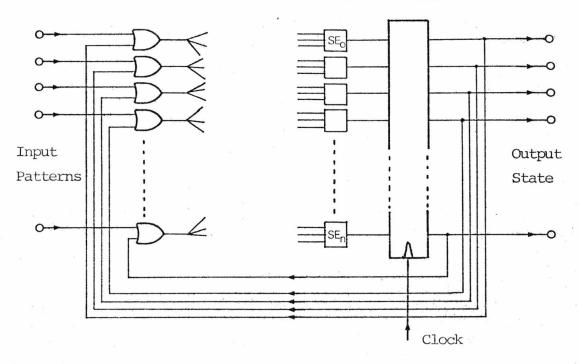

|       |            | Feedback Networks                                             | 77   |

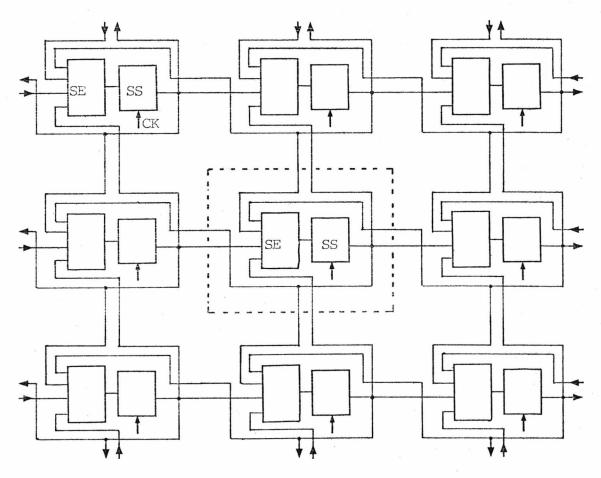

|       |            | Other Network Structures                                      | 79   |

| 3.2   |            | lised Network Model                                           | 79   |

|       |            | Network Systems Design Considerations                         | 82   |

|       | 3.2.1      | The Realisation of Network Interconnectings by Software       | 87   |

|       | 3.2.2      | Data Through-put of Various Network Implementations           | 88   |

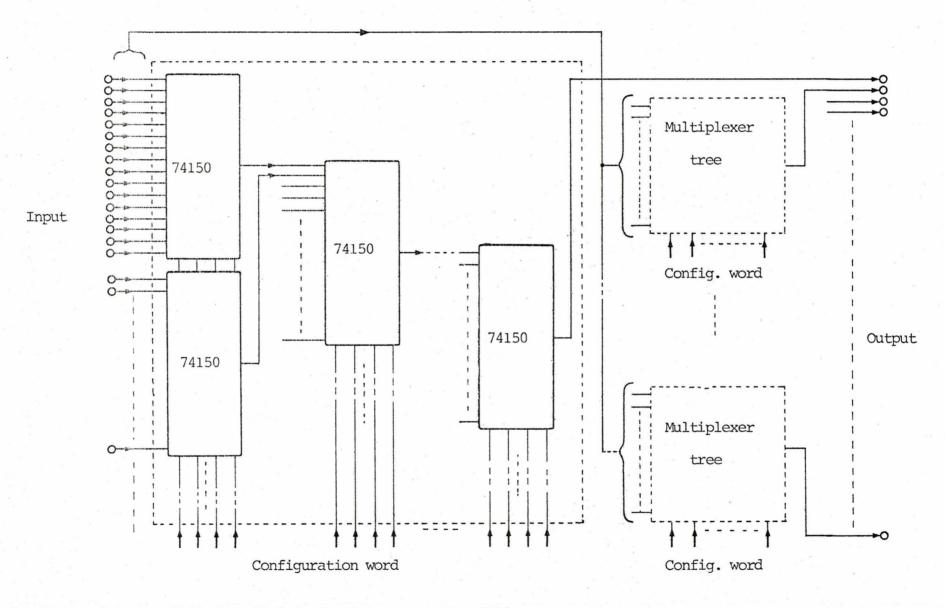

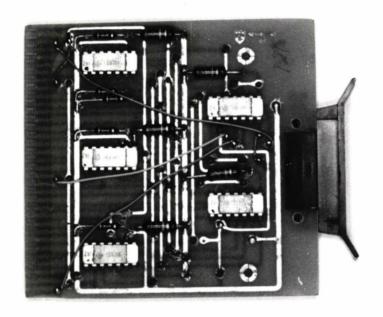

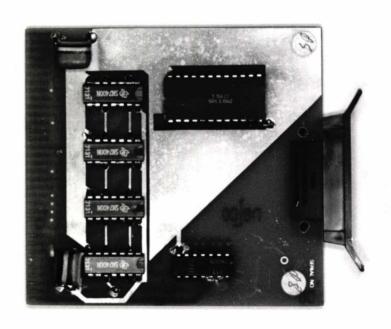

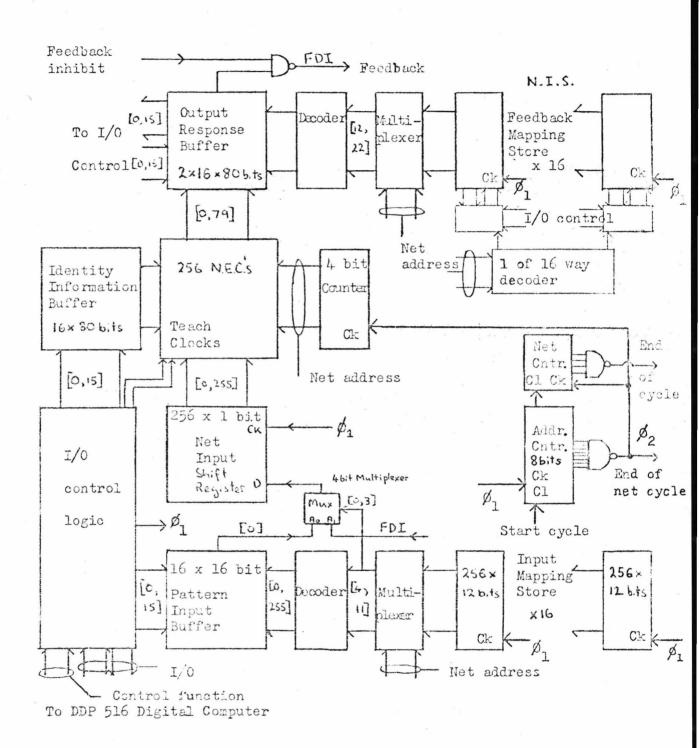

| 3.3   | The Netw   | ork Element Hardware                                          | 90   |

|       | 3.3.0      | The Use of S.L.A.M16 as a Network Element                     | 90   |

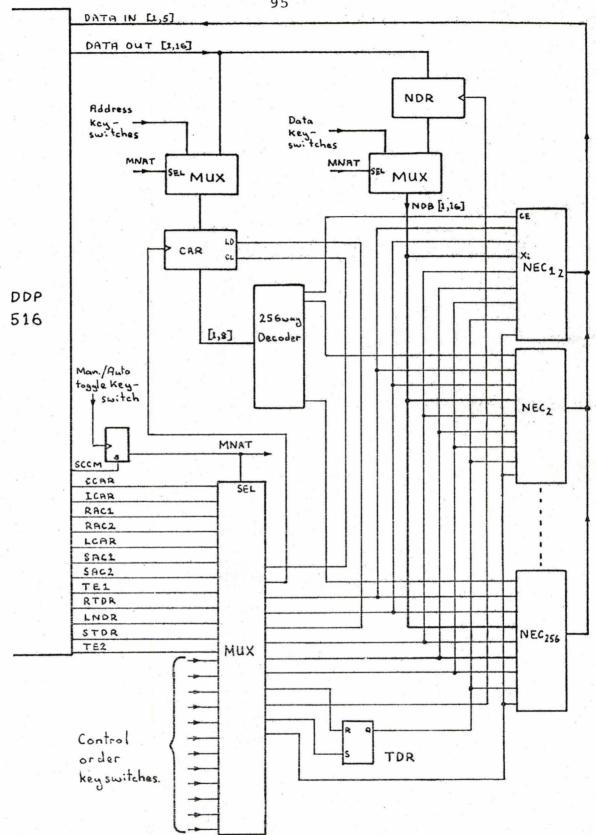

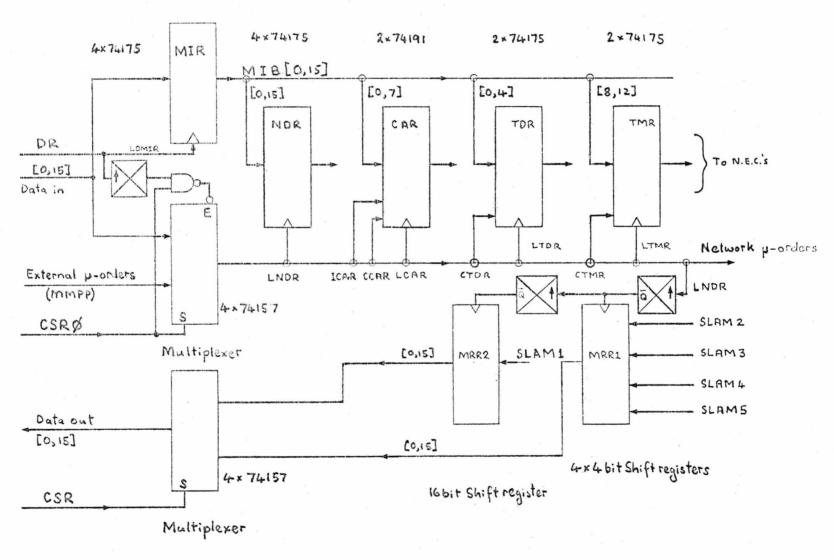

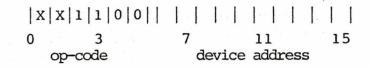

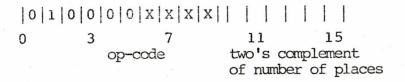

|       | 3.3.1      | Control Circuitry for the N.E.C.'s and the Computer Interface | 98   |

|       | 3.3.2      | The Operation of the Network Hardware                         | 99   |

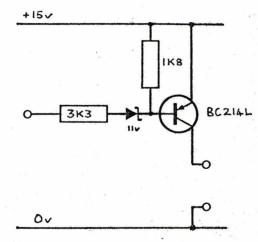

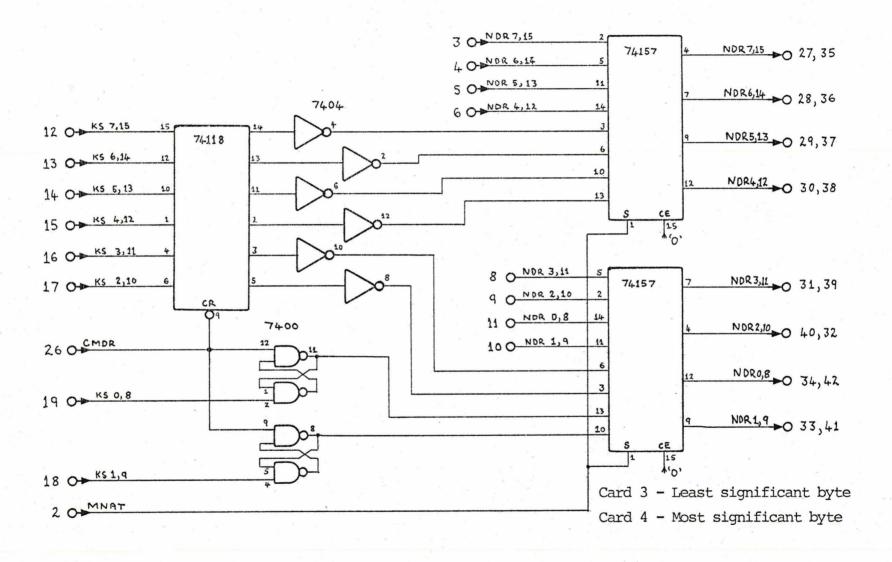

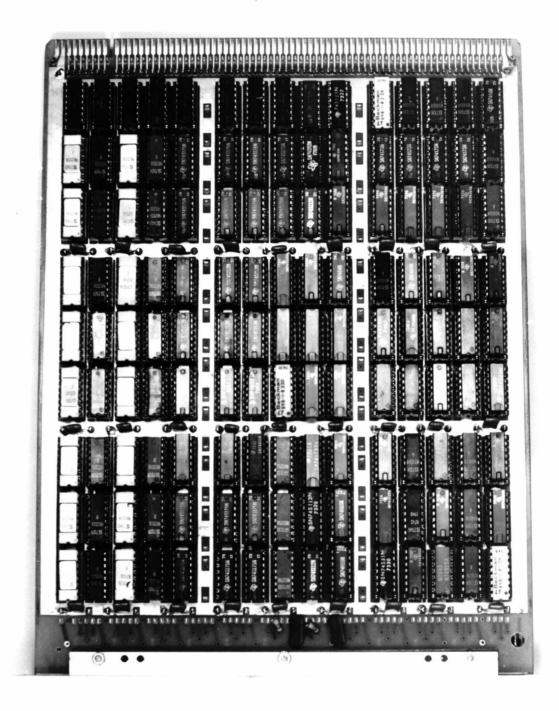

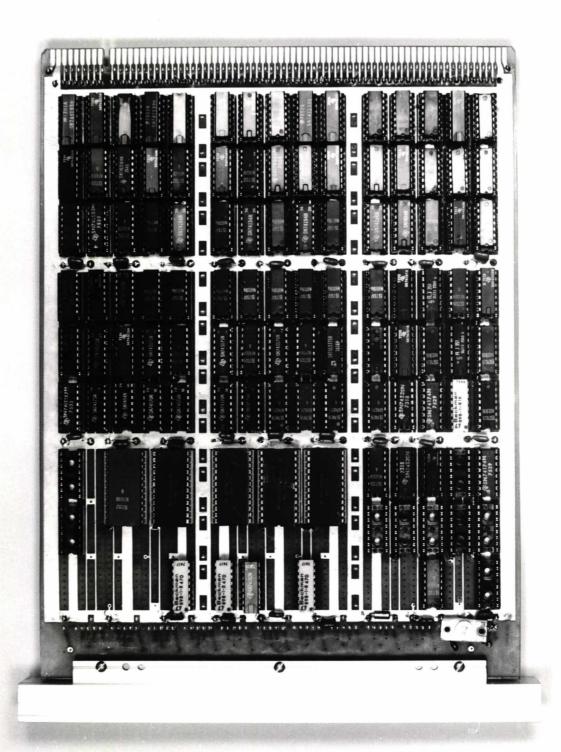

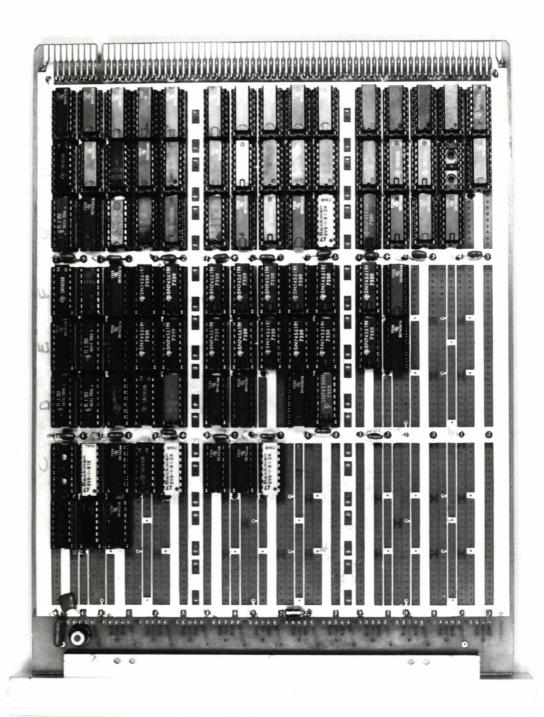

|       | 3.3.3      | Hardware Implementation of the Network Control<br>Circuitry   | 102  |

| 3.4   | Commissi   | oning the Network Element Hardware                            | 112  |

|       |            | Computerised Testing of the N.E.H.                            | 112  |

|       | 3.4.1      | Type of Error                                                 | 113  |

|       |            |                                                               |      |

Page

|       |                                                          | Page      |

|-------|----------------------------------------------------------|-----------|

| CHAPI | TER 4                                                    |           |

| Learn | ning Network Software                                    | 5.75 1.04 |

|       |                                                          |           |

| 4.0   | Introduction                                             | 115       |

| 4.1   | An Overview of Previous Network Software                 | 116       |

|       | 4.1.0 Assembly Language Simulation Systems               | 116       |

| 4.2   | The Development of a Pattern Handling Language           | 119       |

| 4.3   | Primitive Operators and Variables                        | 120       |

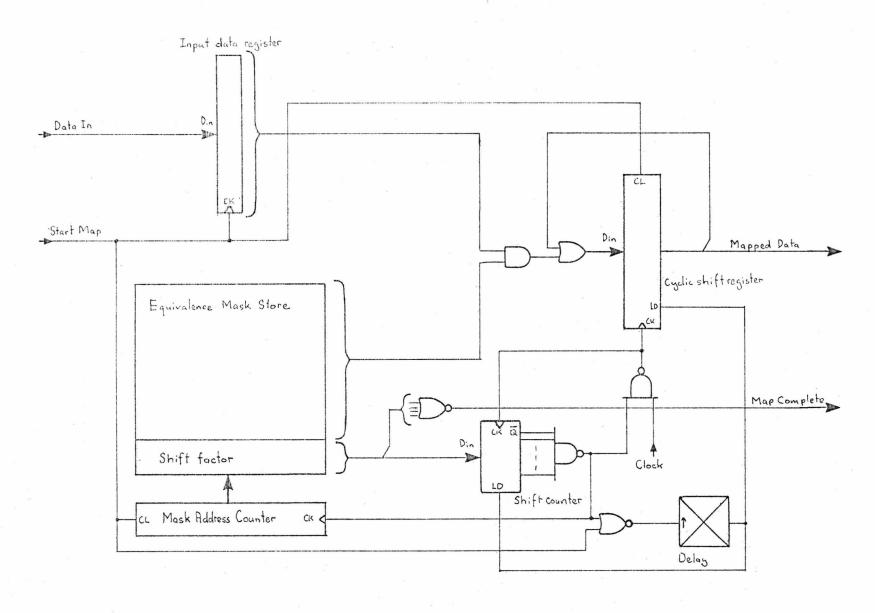

|       | 4.3.0 Mapping and Interconnections                       | 121       |

|       | 4.3.1 Network Variables and Hardware                     | 122       |

| 4.4   | Choosing a Syntactic Vehicle for the Language Primatives | 123_      |

| 5 % 5 | 4.4.0 The DDP 516 FORTRAN System                         | 124       |

|       | 4.4.1 PL 516: A "High-Level Assembler"                   | 125       |

| 4.5   | Formal Definition of MINIC                               | 126       |

| 4.6   | MINIC Statements                                         | 127       |

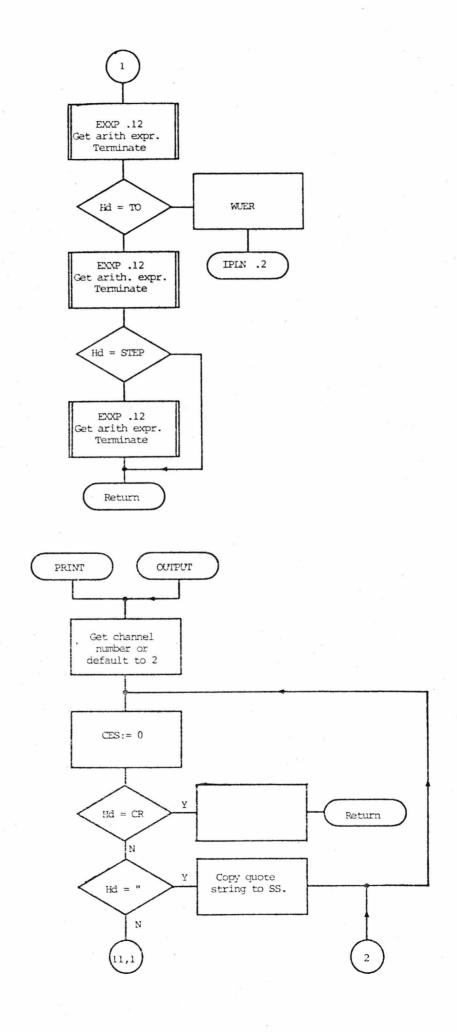

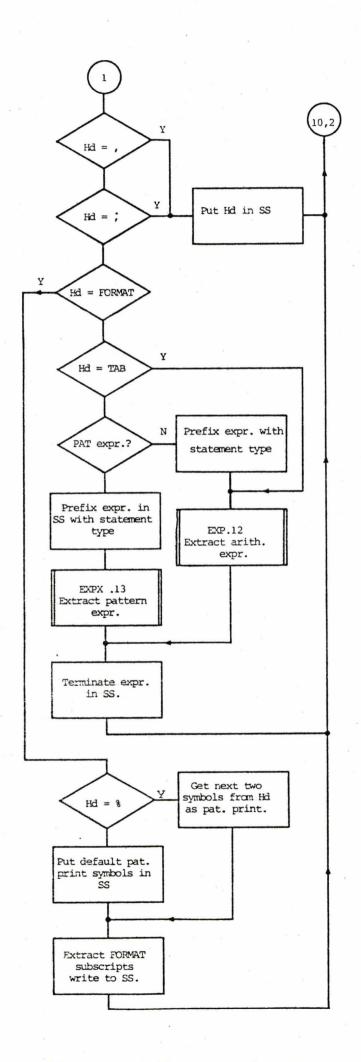

|       | 4.6.0.0 The OUTPUT Statement                             | 127       |

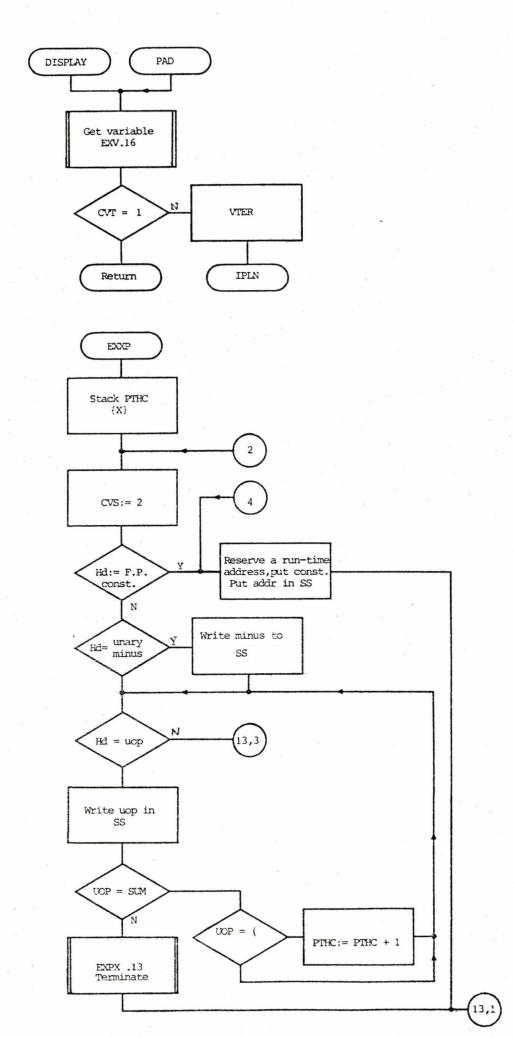

|       | 4.6.0.1 The DISPLAY Statement                            | 128       |

|       | 4.6.0.2 The PAD Statement                                | 128       |

|       | 4.6.1 MINIC Expressions                                  | 128       |

|       | 4.6.1.0 Precedence of Operators                          | 129       |

|       | 4.6.1.1 Use of Parenthesis                               | 130       |

|       | 4.6.1.2 Restrictions on the Universality of Variables    | 130       |

|       | 4.6.2 Other Differences between BASIC and MINIC          | 131       |

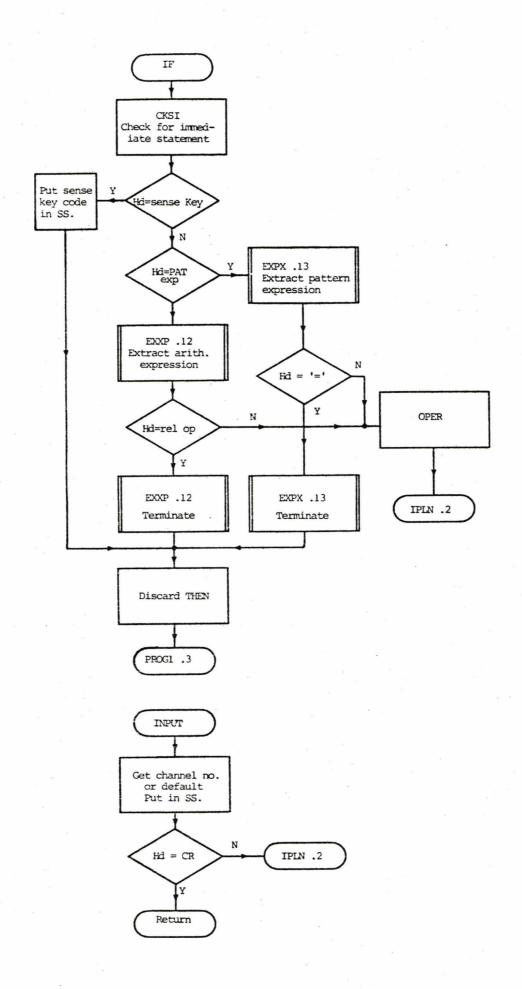

|       | 4.6.2.0 The IF Statement                                 | 131       |

|       | 4.6.2.1 PRINT Statement                                  | 131       |

| 4.7   | Some Examples of MINIC in Use                            | 132       |

|       | 4.7.0 A Ten Class n-tuple Discriminator                  | 132       |

|       | 4.7.1 A Feedback Network                                 | 135       |

|       | 4.7.2 Other Examples of MINIC in Use                     | 141       |

| 4.8   | MINIC and A.P.L.; Similarities and Differences           | 142       |

| 4.9   | Further Developments of the MINIC Language               | 146       |

| 4.10  | A Summary                                                | 149       |

|       |                                                          |           |

|       |                                                          |           |

| CHAPI | TER 5                                                    |           |

| The I | implementation of a Compiler for the MINIC Language      |           |

| 5.0   | Introduction                                             | 152       |

| 5.1  | Introduc                | tion to Compiling Techniques                               | 152 |

|------|-------------------------|------------------------------------------------------------|-----|

|      | 5.1.0                   | Types of Translator Systems                                | 153 |

| 5.2  | The Natu                | re of the Compiler Problem                                 | 154 |

|      | 5.2.0                   | Lexical Analysis                                           | 154 |

|      | 5.2.1                   | The Syntax Analyser                                        | 155 |

|      | 5.2.2                   | Target Code Generation                                     | 161 |

| 5.3  | The Hone                | ywell DDP 516 MINIC Compiler System                        | 164 |

|      | 5.3.0                   | Memory Allocation of the MINIC System .                    | 165 |

|      | 5.3.1                   | MINIC as a ADMOS Sub-System                                | 169 |

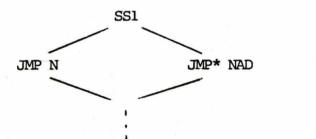

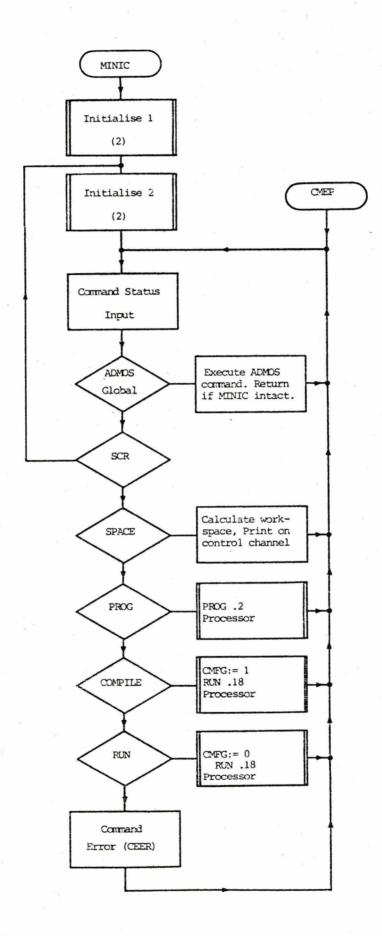

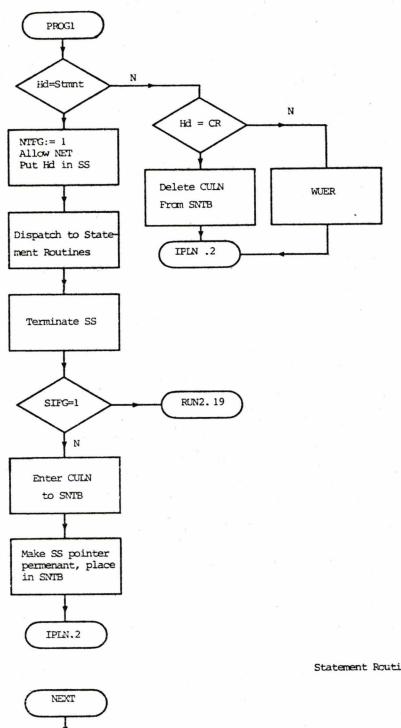

|      | 5.3.2                   | The MINIC Command Executive                                | 170 |

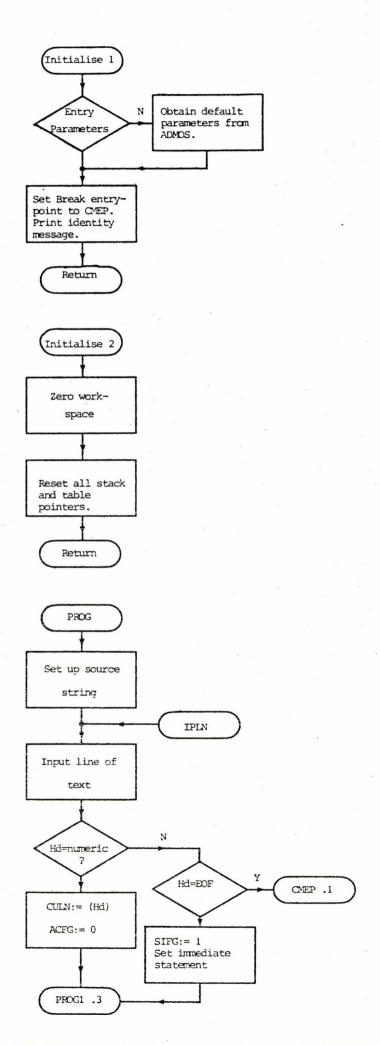

|      | 5.3.3                   | Program Input and Lexical Analysis                         | 172 |

|      | 5.3.4                   | The Symbol Table                                           | 173 |

|      | 5.3.5                   | The S-String                                               | 175 |

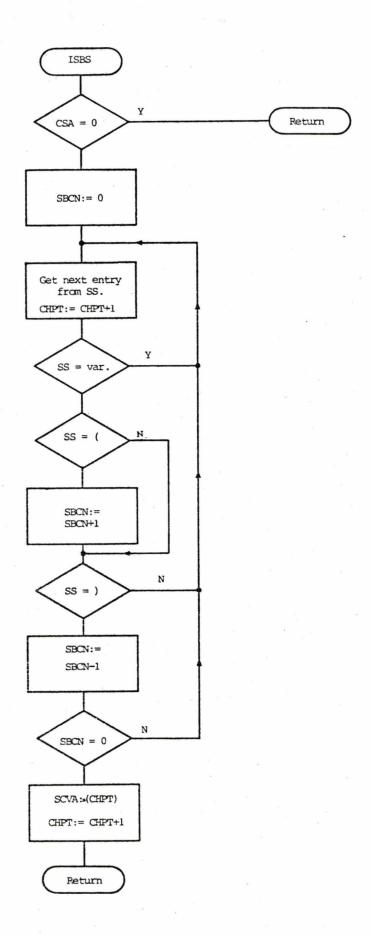

|      | 5.3.6                   | Recursive Lexical Routines                                 | 176 |

|      | 5.3.7                   | Systems Stack Organisation and Recursion                   | 178 |

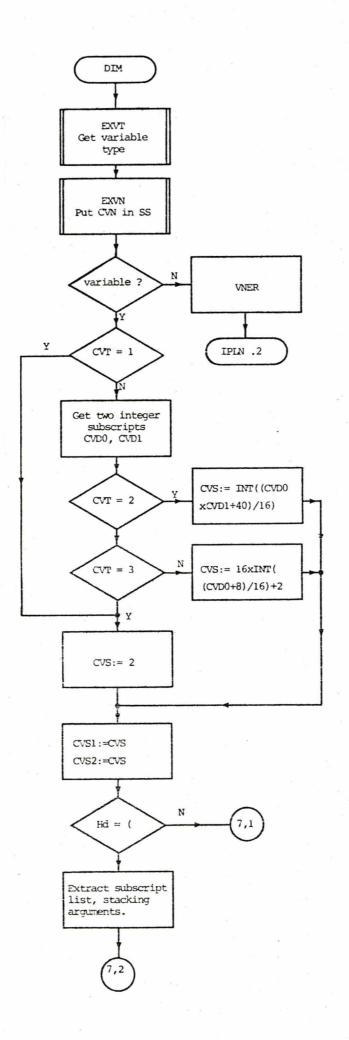

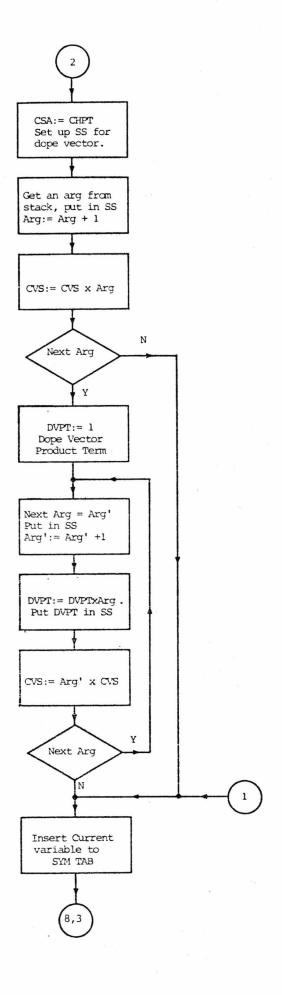

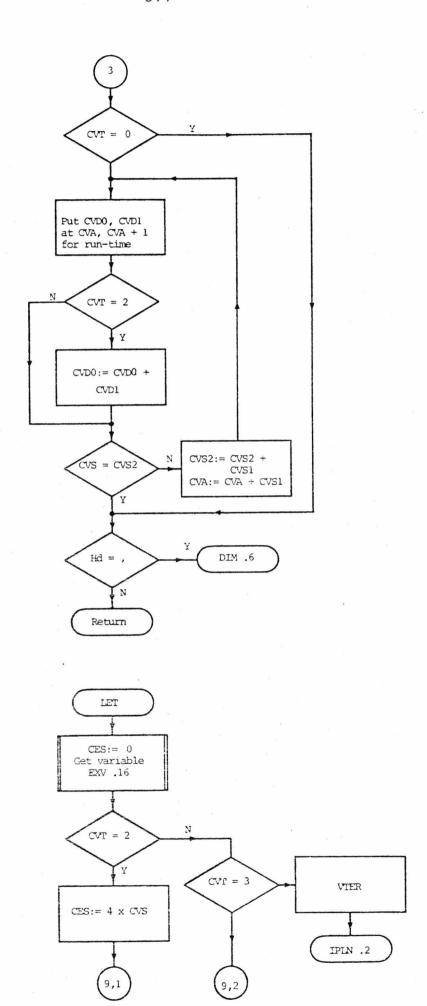

|      | 5.3.8                   | The DIM Statement and Internal Representation of Variables | 179 |

|      | 5.3.9                   | Errors During Program Input                                | 182 |

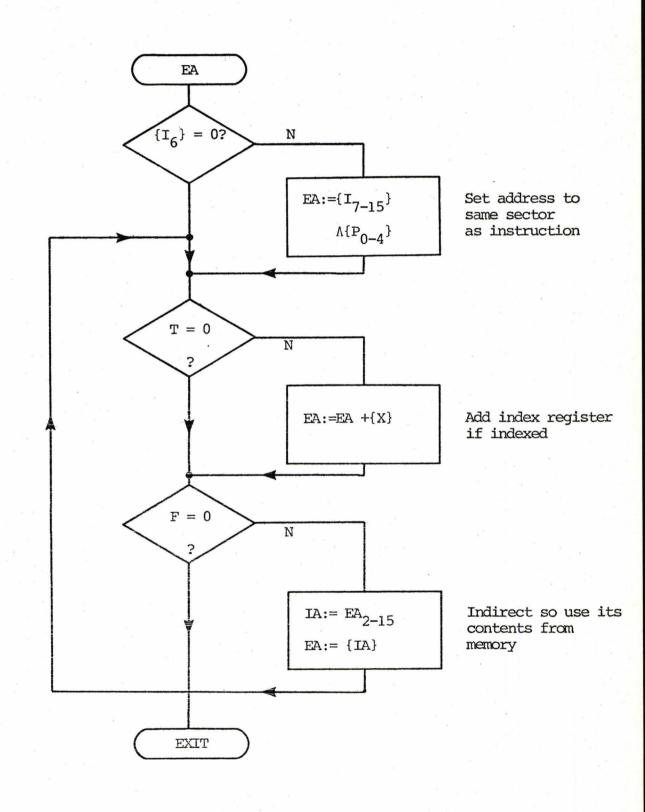

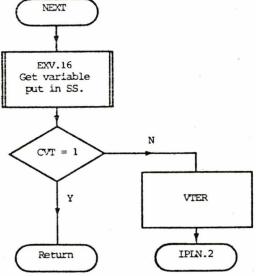

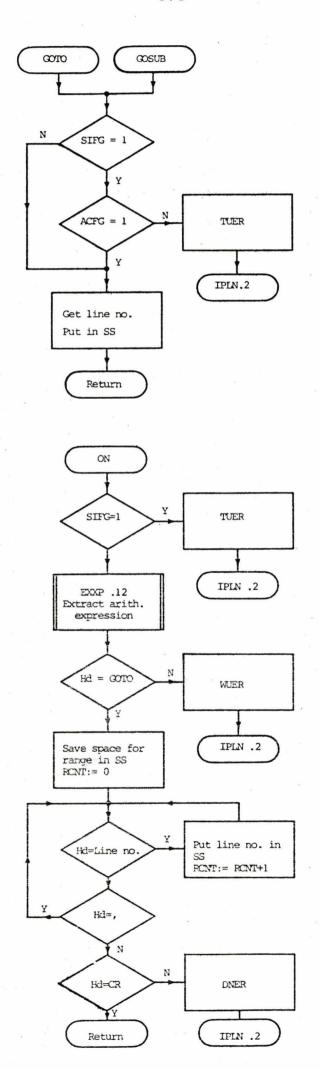

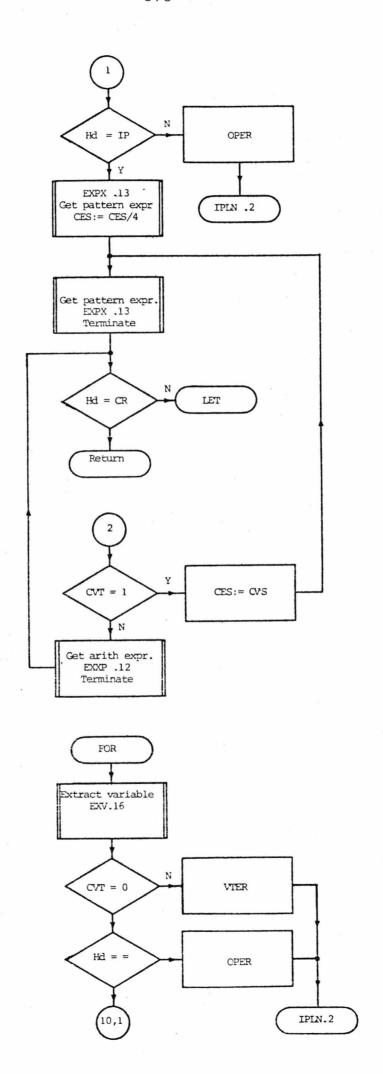

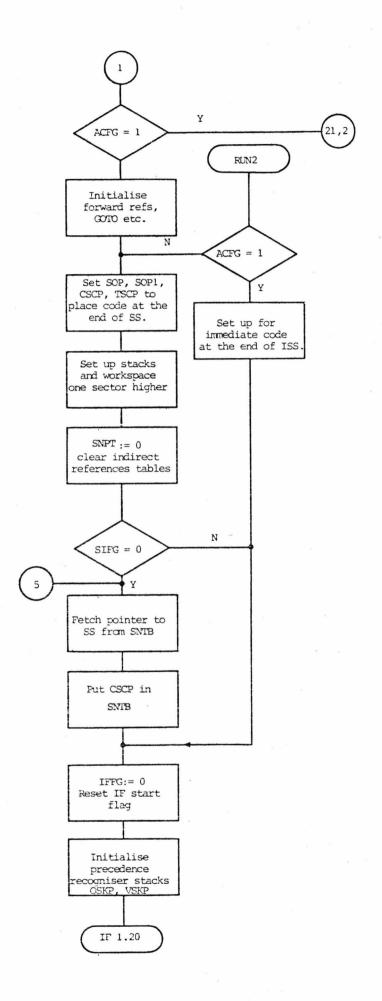

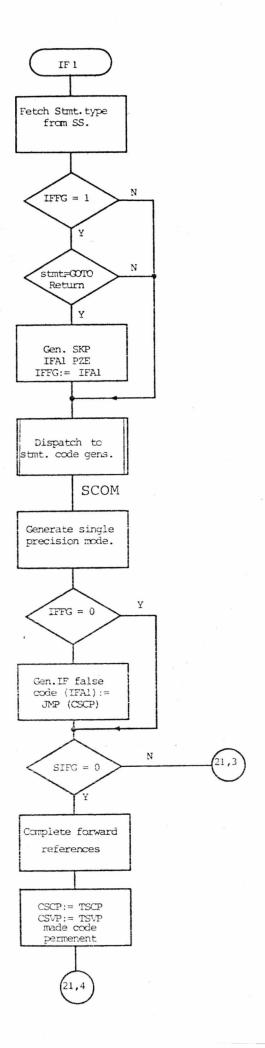

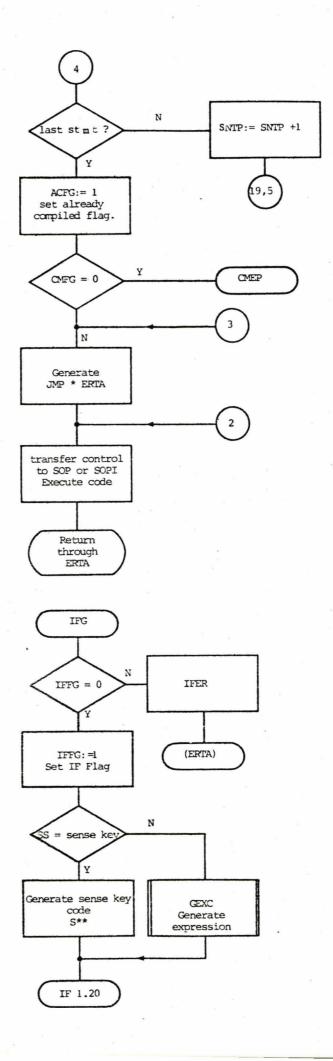

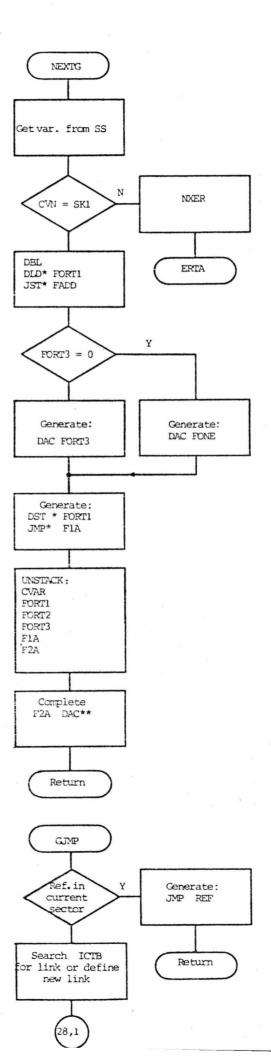

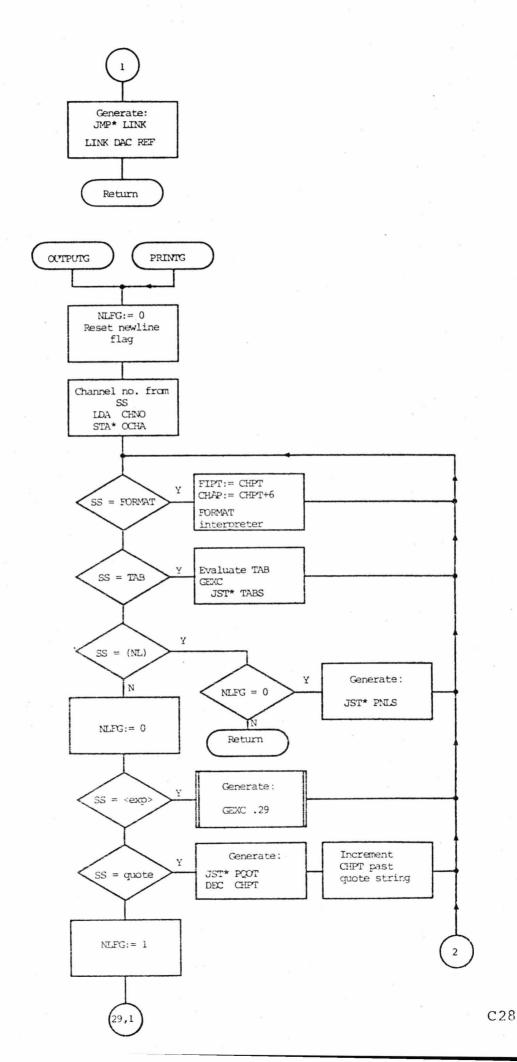

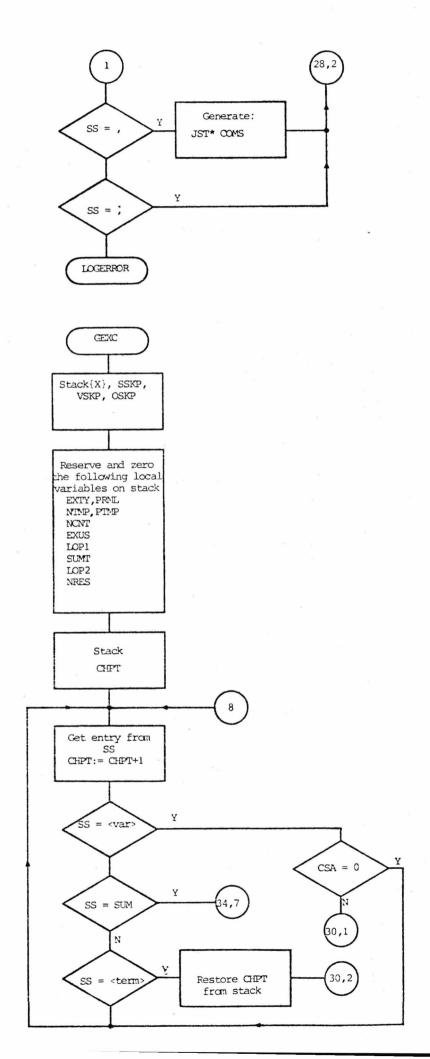

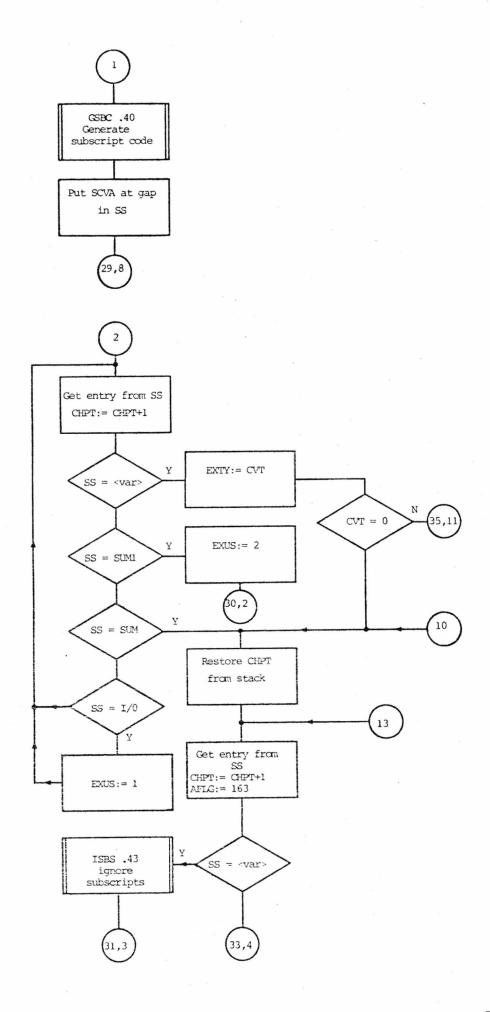

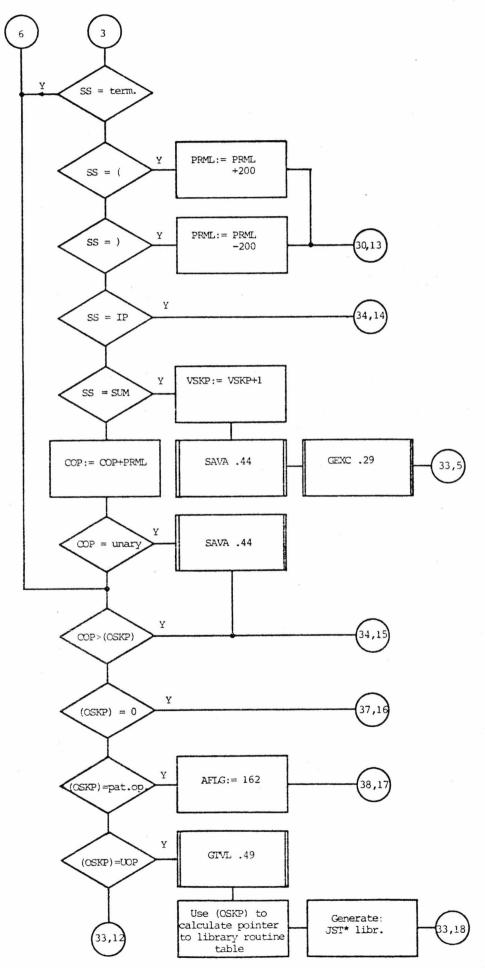

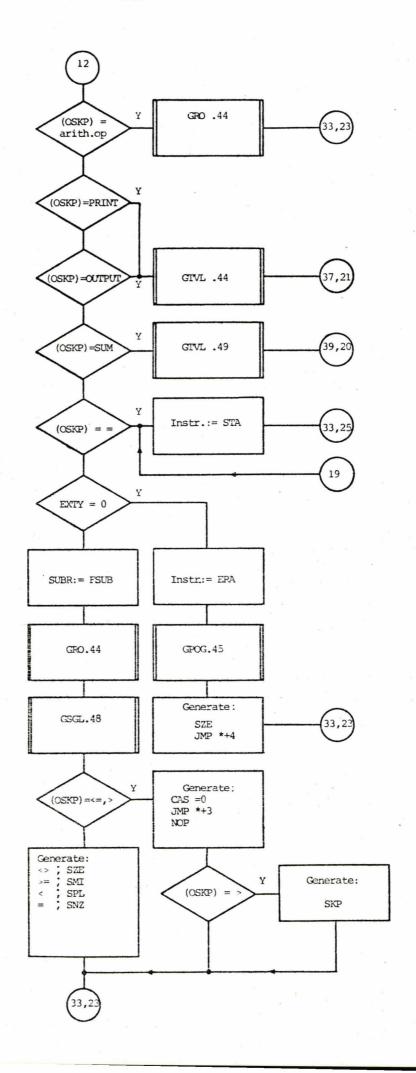

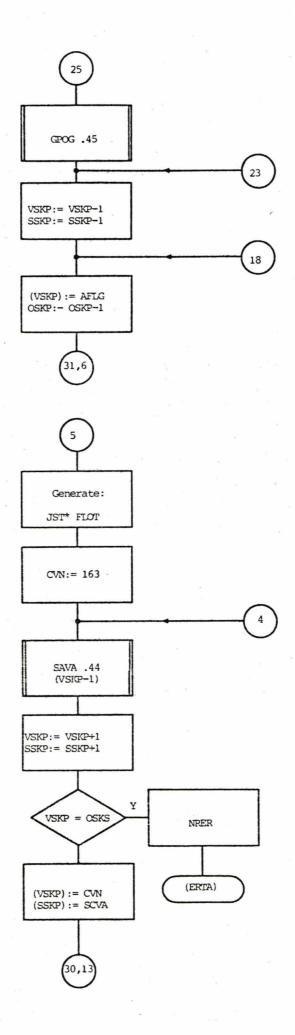

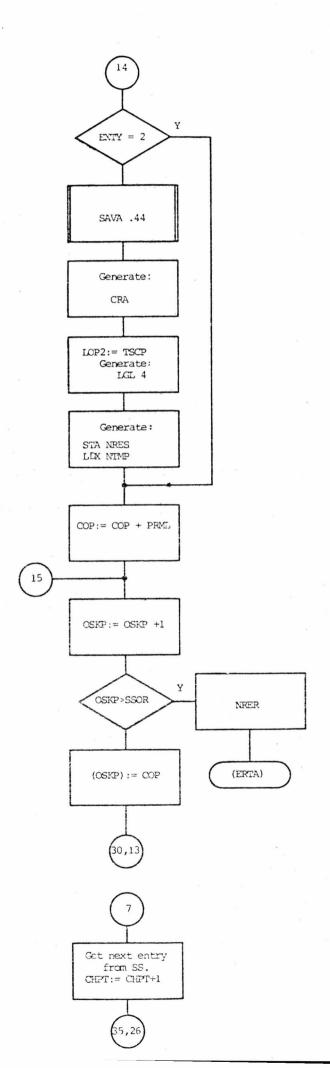

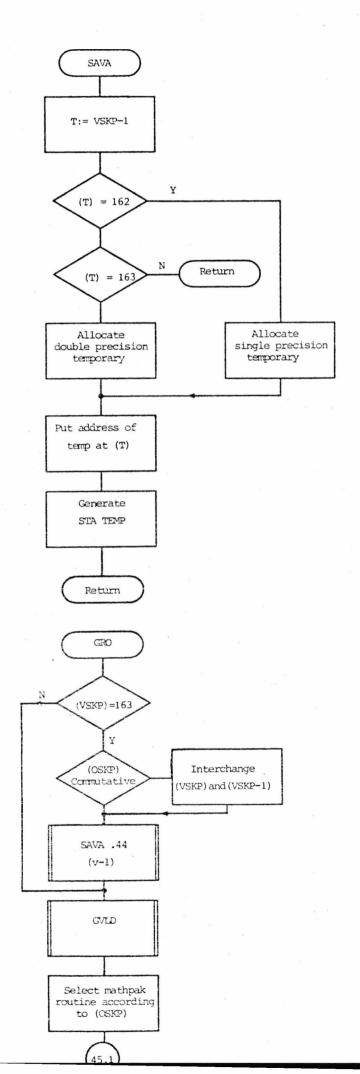

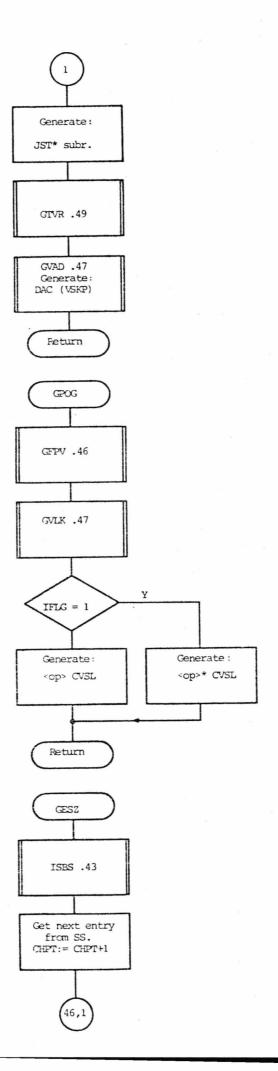

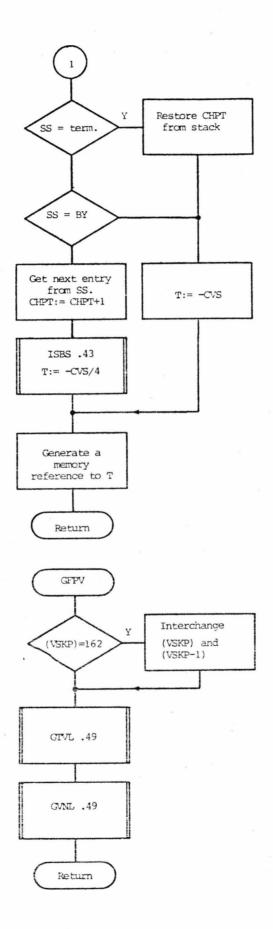

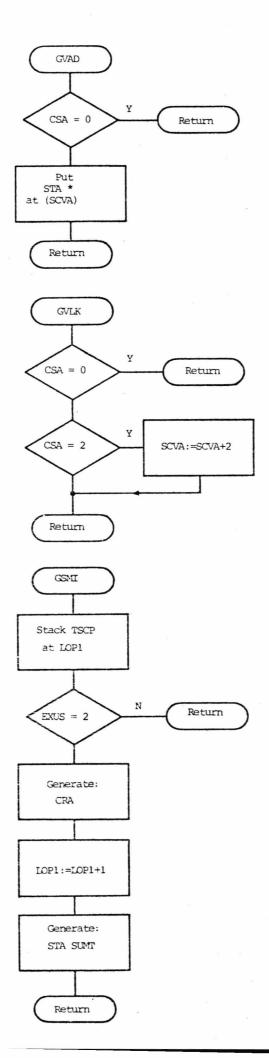

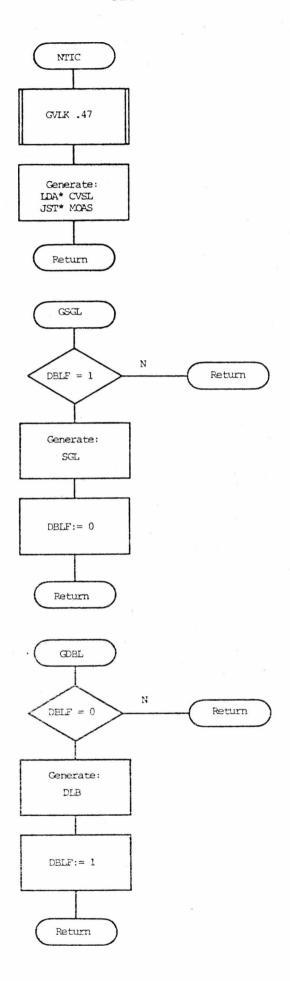

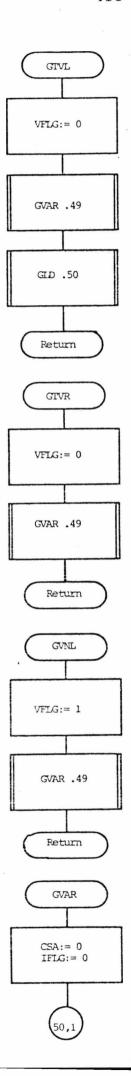

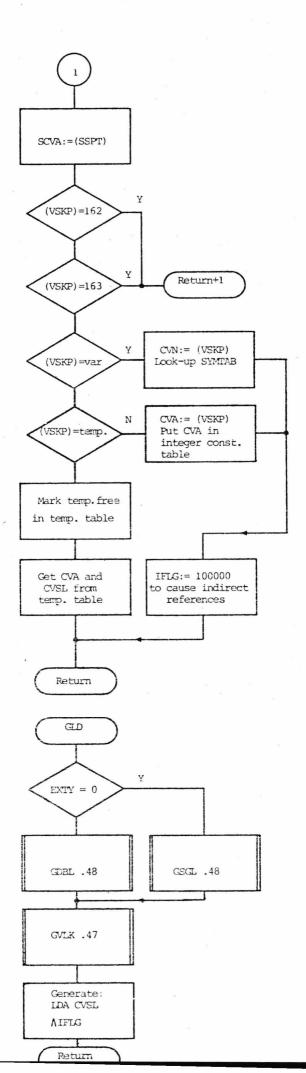

|      | 5.3.10                  | The Syntactic Routines and Target Code<br>Generation       | 184 |

|      | 5.3.11                  | Desectoring Target Code                                    | 185 |

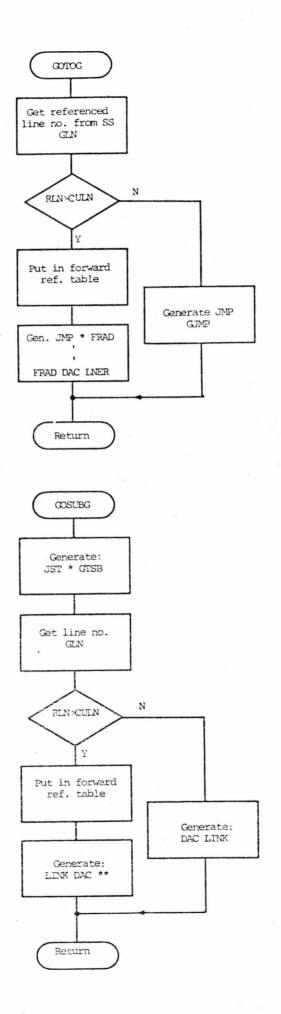

|      | 5.3.12                  | Forward Referenced Locations in the Target Code            | 187 |

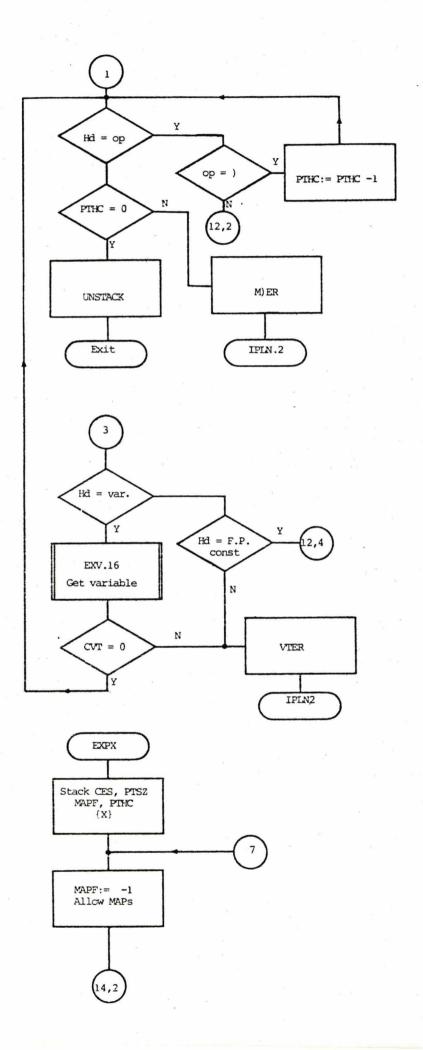

|      | 5.3.13                  | Target Code for Expressions                                | 188 |

|      | 5.3.14                  | Temporary Variables                                        | 200 |

| 5.4  | Execution               | n and Run-Time Routines                                    | 200 |

|      | 5.4.0                   | Run-Time Addressing of Variables                           | 201 |

|      | 5.4.1                   | Evaluation of Operators                                    | 201 |