# **Kent Academic Repository**

Alshammari, Ahmed (2017) *Digital Communication System with High Security and High Immunity.* Doctor of Philosophy (PhD) thesis, University of Kent,.

#### **Downloaded from**

https://kar.kent.ac.uk/69470/ The University of Kent's Academic Repository KAR

The version of record is available from

This document version UNSPECIFIED

**DOI** for this version

Licence for this version UNSPECIFIED

**Additional information**

#### Versions of research works

#### **Versions of Record**

If this version is the version of record, it is the same as the published version available on the publisher's web site. Cite as the published version.

#### **Author Accepted Manuscripts**

If this document is identified as the Author Accepted Manuscript it is the version after peer review but before type setting, copy editing or publisher branding. Cite as Surname, Initial. (Year) 'Title of article'. To be published in *Title of Journal*, Volume and issue numbers [peer-reviewed accepted version]. Available at: DOI or URL (Accessed: date).

#### **Enquiries**

If you have questions about this document contact <a href="ResearchSupport@kent.ac.uk">ResearchSupport@kent.ac.uk</a>. Please include the URL of the record in KAR. If you believe that your, or a third party's rights have been compromised through this document please see our <a href="Take Down policy">Take Down policy</a> (available from <a href="https://www.kent.ac.uk/guides/kar-the-kent-academic-repository#policies">https://www.kent.ac.uk/guides/kar-the-kent-academic-repository#policies</a>).

# Digital Communication System with High Security and High Immunity

# A Thesis Submitted to The University of Kent

For The Degree Of DOCTOR OF PHILOSOPHY

In ELECTRONICS ENGINEERING

By Ahmed S. Alshammari

August, 2017

## **Abstract**

Today, security issues are increased due to huge data transmissions over communication media such as mobile phones, TV cables, online games, Wi-Fi and satellite transmission etc. for uses such as medical, military or entertainment. This creates a challenge for government and commercial companies to keep these data transmissions secure. Traditional secure ciphers, either block ciphers such as Advanced Encryption Standard (AES) or stream ciphers, are not fast or completely secure. However, the unique properties of a chaotic system, such as structure complexity, deterministic dynamics, random output response and extreme sensitivity to the initial condition, make it motivating for researchers in the field of communication system security. These properties establish an increased relationship between chaos and cryptography that create strong and fast cipher compared to conventional algorithms, which are weak and slow ciphers. Additionally, chaotic synchronisation has sparked many studies on the application of chaos in communication security, for example, the chaotic synchronisation between two different systems in which the transmitter (master system) is driving the receiver (slave system) by its output signal.

For this reason, it is essential to design a secure communication system for data transmission in noisy environments that robust to different types of attacks (such as a brute force attack). In this thesis, a digital communication system with high immunity and security, based on a Lorenz stream cipher chaotic signal, has been perfectly applied.

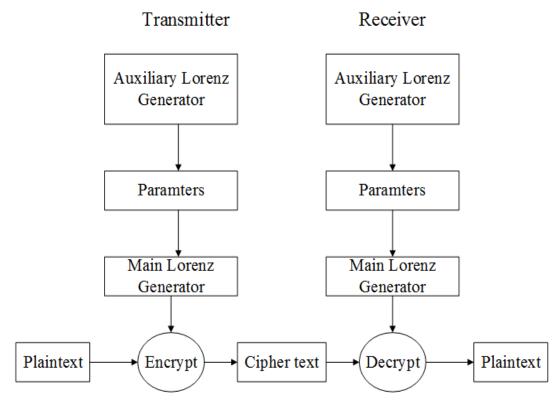

A new cryptosystem approach based on Lorenz chaotic systems was designed for secure data transmission. The system uses a stream cipher, in which the encryption key varies continuously in a chaotic manner. Furthermore, one or more of the parameters of the Lorenz generator is controlled by an auxiliary chaotic generator for increased security. In this thesis, the two Lorenz chaotic systems are called the Main Lorenz Generator and the Auxiliary Lorenz Generator. The system was designed using the SIMULINK tool. The system performance in the presence of noise was tested, and the simulation results are provided. Then, the clock-recovery technique is presented, with real-time results of the clock recovery. The receiver demonstrated its ability to recover and lock the clock successfully. Furthermore, the technique for

synchronisation between two separate FPGA boards (transmitter and receiver) is detailed, in which the master system transmits specific data to trigger a slave system in order to run synchronously. The real-time results are provided, which show the achieved synchronisation. The receiver was able to recover user data without error, and the real-time results are listed.

The randomness test (NIST) results of the Lorenz chaotic signals are also given. Finally, the security analysis determined the system to have a high degree of security compared to other communication systems.

# **Acknowledgments**

Firstly, I would like to express my sincere to my supervisor Prof. Mohamed Sobhy for the continuous support of my PhD study and related research and, for his patience and motivation. It has been a great honor to work with him and gained invaluable expert throughout this work. Furthermore, I would like to thank my second supervisor Dr. Peter Lee for his support and encouragement throughout this work.

Beside my supervisors, I would like to thank Dr. Mark Esdale for his support throughout this work.

I would like to express my special thanks to my mother, Rouf Saad Alshammari, for her spiritually support. Words cannot express how grateful I am to my wife, Suaad Suliman Alshammari, my kids, Saud, Fahad, Abdulmailk and my little daughter Haneen, for their support and patience through my ups downs, without them, I never would have been able to achieve my goals.

I would like to convey my special thanks to my father in low Mr. Suliman Namer Alshammari and Mrs. Juzaiah Alshammari for their continual support.

Last but not the least, thank you to everyone who support and encourage me. In particular, my brothers, Mamdouh Saud Alshammari, Fahad Kulaif Alenzi, Alhumadi Salamh Alshammari and Tuwallai Turki Alshammari.

# **Contents**

| Abstrac | t                                                           |      |

|---------|-------------------------------------------------------------|------|

| Acknow  | vledgments                                                  | iii  |

| Content | ts                                                          | iv   |

| List of | Figures                                                     | viii |

| Glossar | y of Abbreviations                                          | xiv  |

| List of | Гable                                                       | xvii |

| INTRO   | DUCTION                                                     | 1    |

| 1.1     | The Bases of Secure Communication                           | 1    |

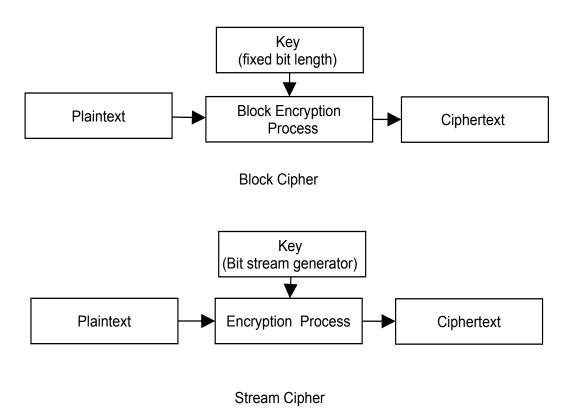

| 1.2     | Block Cipher and Stream Cipher                              | 2    |

| 1.3     | Properties of Chaos in Communication System Applications    | 3    |

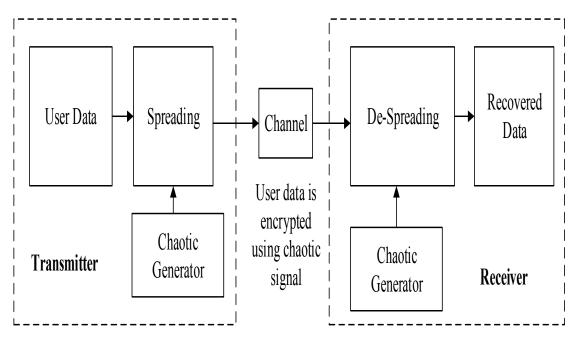

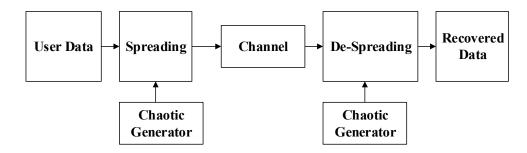

| 1.4     | Chaos for Spread-Spectrum Technology                        | 4    |

| 1.5     | Reception Types Used with Chaos-Based Communication Systems | 5    |

| 1.6     | Spreading and De-Spreading Methods for CMDA                 | 5    |

| 1.7     | Generation of Chaotic Signals for Encryption.               | 7    |

| 1.7     | .1 The Chua system                                          | 7    |

| 1.7     | .2 The Rössler System                                       | 10   |

| 1.7     | .3 The Lorenz system                                        | 12   |

| 1.8     | Communication Systems Overview                              | 14   |

| 1.9     | Proposed Communication System                               | 14   |

| 1.10    | Original Contributions                                      | 15   |

| 1.11    | List of Publications                                        | 16   |

| LITER   | ATURE REVIEW                                                | 18   |

| 2.1     | Introduction                                                | 18   |

| 2.2     | Coherent Chaos Modulation Schemes                           | 19   |

| 2.3     | Synchronization Methods                                     | 20   |

| 2.4     | Chaos-based Spread Spectrum                                 | 22   |

| 2.5     | Related Surveys based on Real Time Implementations          | 27   |

|         | AL COMMUNICATION SYSTEM WITH HIGH SECURITY AND H            |      |

| NOISE   | IMMUNITY: SECURITY ANALYSIS AND SIMULATION                  | 30   |

| 3 1     | The Bases of Security Analysis                              | 30   |

| 3.1.1 The key length                                                               | 32     |

|------------------------------------------------------------------------------------|--------|

| 3.1.2 The key space                                                                |        |

| 3.1.3 Confusion and diffusion                                                      |        |

| 3.1.4 Brute force attack                                                           | 33     |

| 3.1.5 Binary sequence randomness test of the encryption generator                  | 33     |

| 3.2 Communication system with High Security and High Noise Immun                   | nity34 |

| 3.2.1 Comparison of the chaotic system cryptosystem with other crypt systems       |        |

| 3.2.2 An encryption system                                                         | 37     |

| 3.2.3 Analogue to Digital Conversion                                               | 39     |

| 3.2.4 Randomness Test                                                              | 40     |

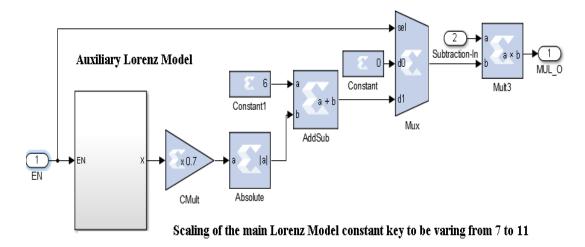

| 3.2.5 Scrambling scheme of Lorenz chaotic signal                                   | 41     |

| 3.2.6 High system parameter sensitivity                                            | 43     |

| 3.2.7 The key space of the proposed cryptosystem                                   | 44     |

| 3.3 System Overview                                                                | 44     |

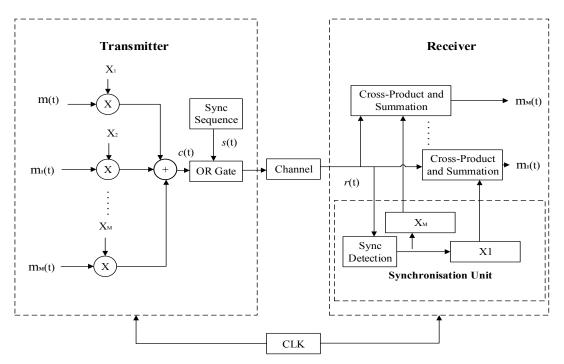

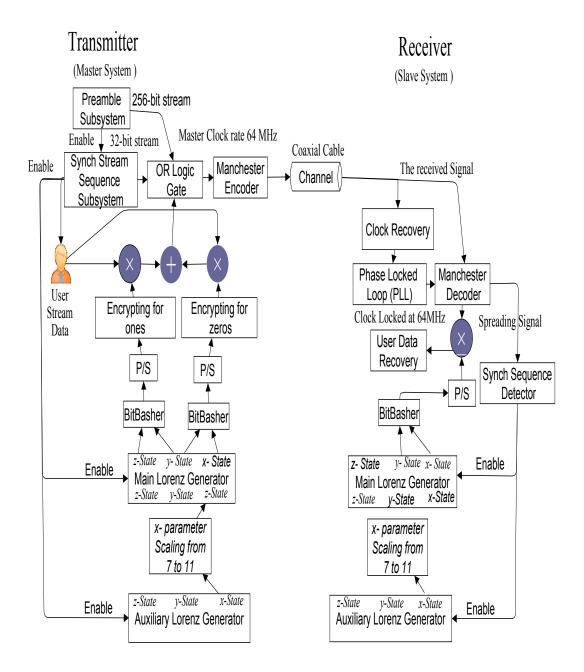

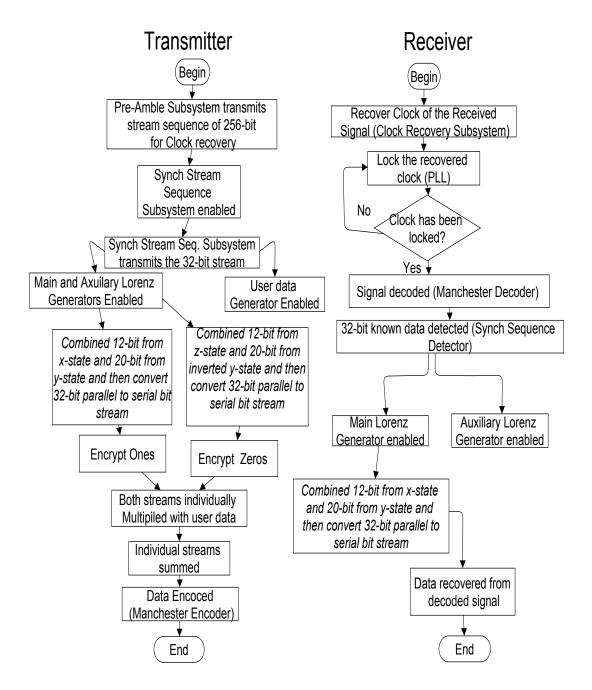

| 3.3.1 Transmitter system                                                           | 46     |

| 3.3.2 Receiver system                                                              | 49     |

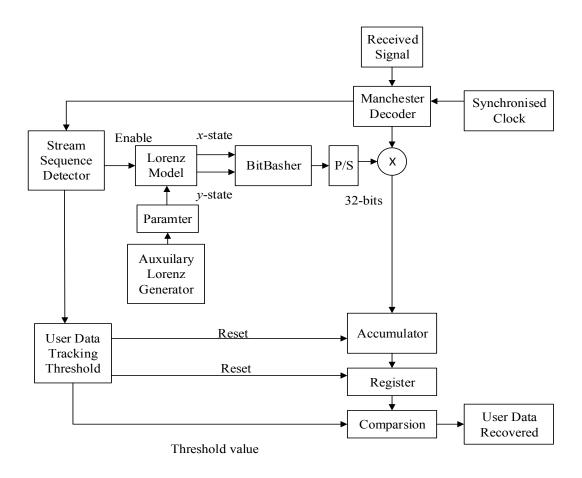

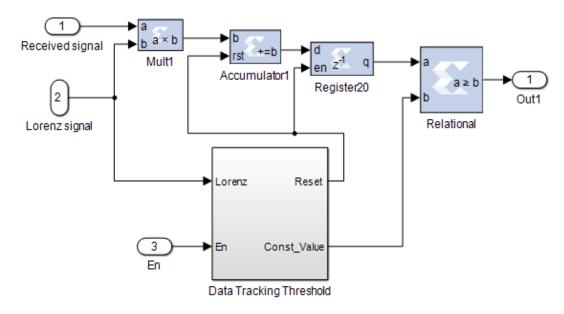

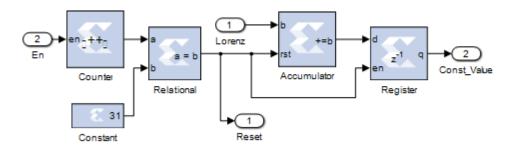

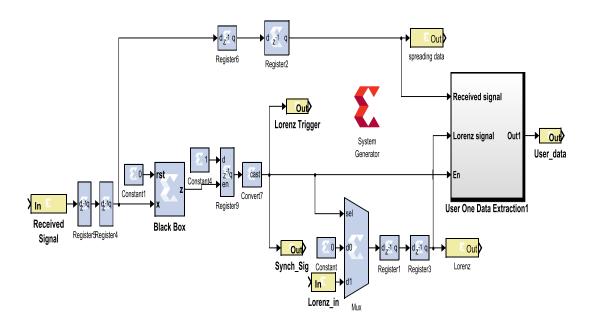

| 3.3.3 Data extraction                                                              | 59     |

| 3.4 Communication System with Added Noise                                          | 62     |

| 3.4.1 System performance                                                           | 65     |

| 3.5 Conclusion                                                                     | 67     |

| DESIGN METHODOLOGY, CLOCK AND DATA RECOVERY AND SYNCHRONISATION OF CHAOTIC SIGNALS | 69     |

| 4.1 FPGA Technology Features                                                       |        |

| 4.2 Design Methodology                                                             |        |

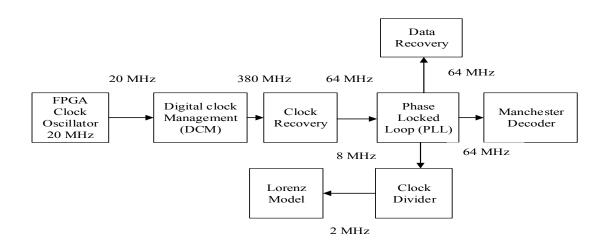

| 4.3 Clock and Data Recovery (CDR)                                                  |        |

| 4.4 Real time implementation of the clock recovery                                 |        |

| 4.5 Data recovery                                                                  |        |

| 4.6 Synchronisation of Chaotic Signals                                             |        |

| 4.7 FPGA Implementation Results                                                    |        |

| 4.8 Conclusion                                                                     | 102    |

| FPGA IMPLEMENTATION OF COMMUNICATION SYSTEMS USING                   |        |

|----------------------------------------------------------------------|--------|

| CHAOTIC BLOCK CIPHER                                                 |        |

| 5.1 Introduction                                                     |        |

| 5.2 Block Spreading Communication System                             |        |

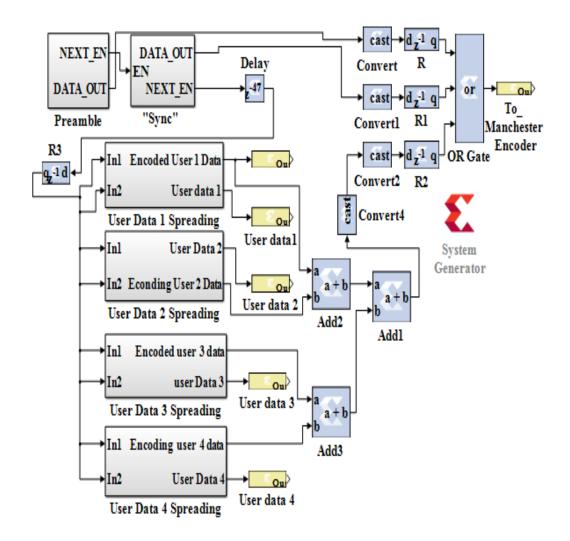

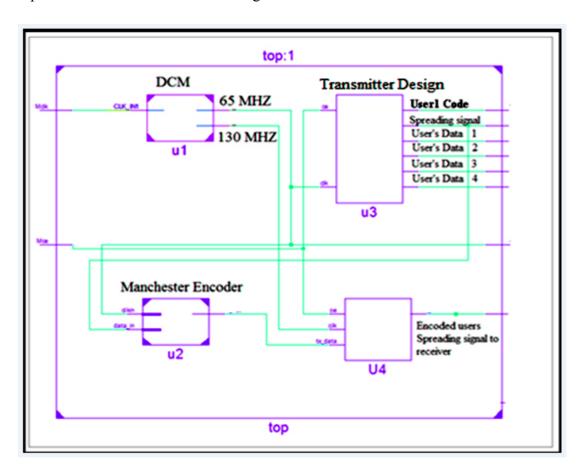

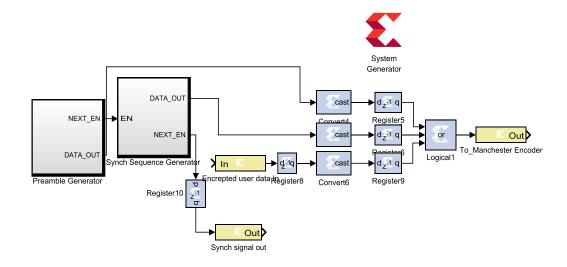

| 5.3 Transmitter System                                               |        |

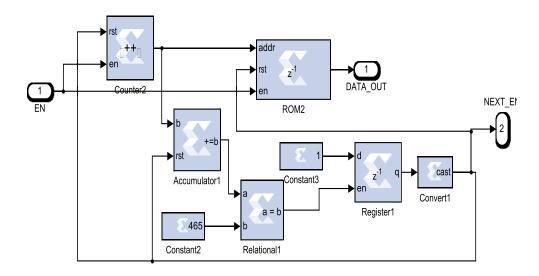

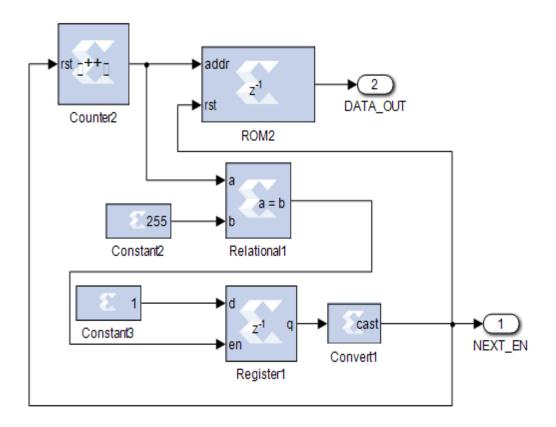

| 5.3.1 Preamble subsystem                                             |        |

| 5.3.2 User data generator                                            |        |

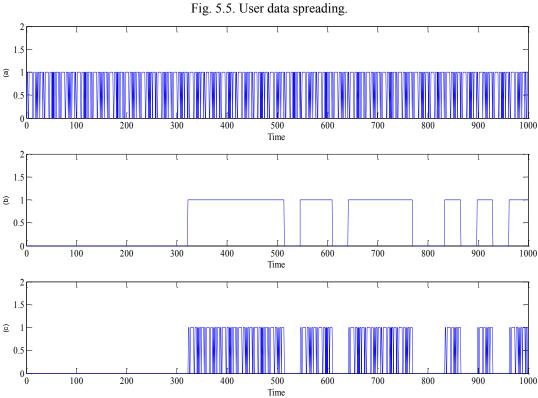

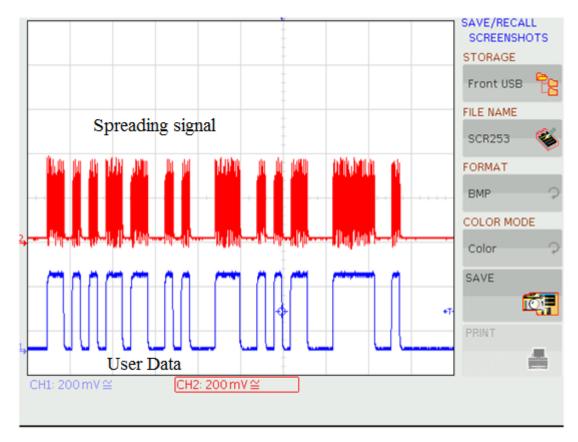

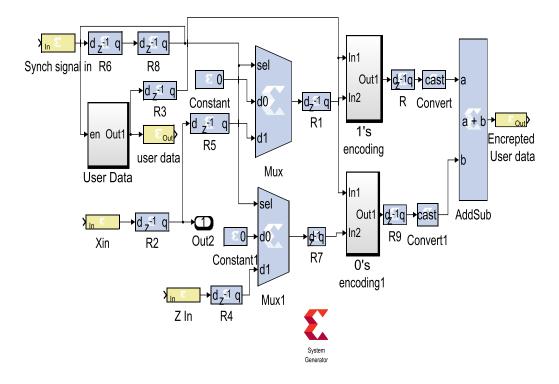

| 5.3.3 User data spreading                                            |        |

| 5.3.4 Adder                                                          | 111    |

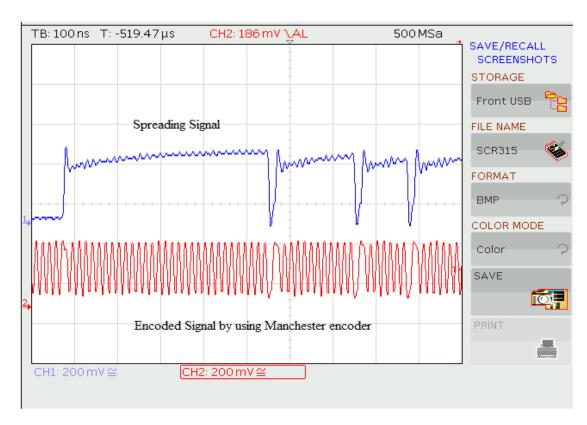

| 5.3.5 Manchester encoder                                             | 113    |

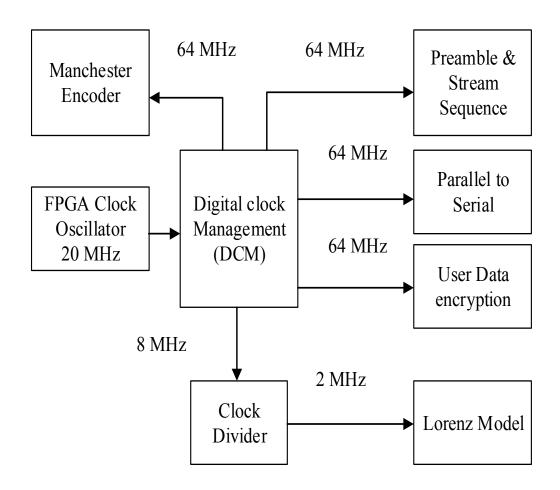

| 5.3.6 System clock rates                                             | 113    |

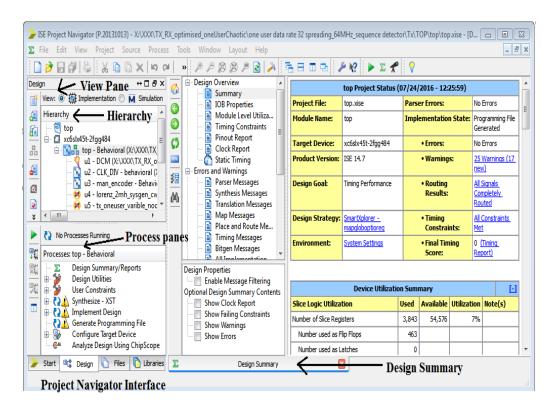

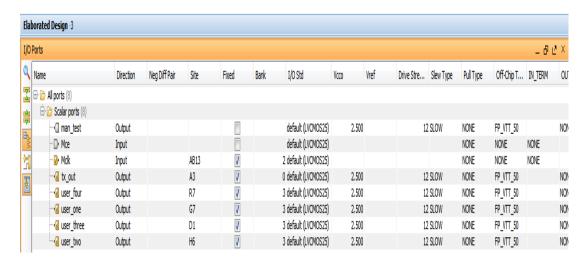

| 5.3.7 Integrated Synthesis Environment (Xilinx® ISE)                 | 114    |

| 5.3.8 Device Utilisation Summary                                     | 115    |

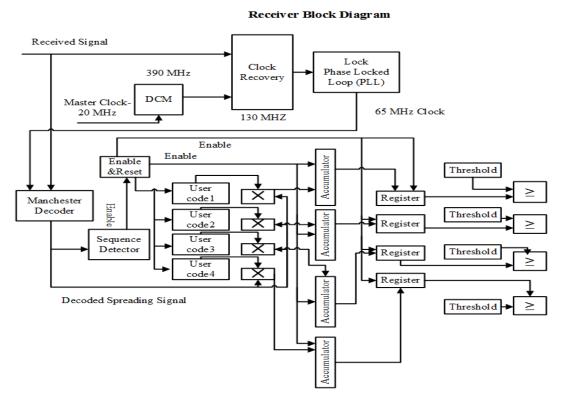

| 5.4 Receiver System                                                  | 116    |

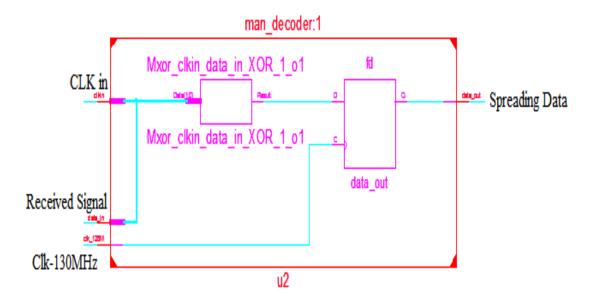

| 5.4.1 Manchester decoder                                             | 117    |

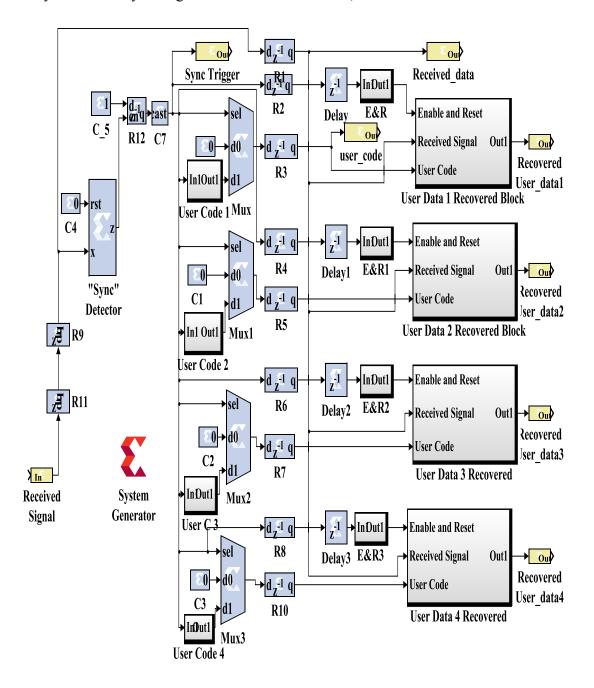

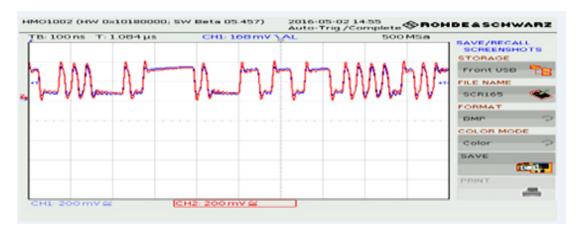

| 5.4.2 Block spreading synchronisation                                | 118    |

| 5.4.3 Data recovery                                                  | 119    |

| 5.4.4 Integrated synthesis environment (Xilinx® ISE)                 | 122    |

| 5.4.5 Device utilisation summary                                     | 123    |

| 5.5 Conclusion                                                       | 124    |

| FPGA IMPLEMENTATION OF COMMUNICATION SYSTEMS USING                   |        |

| CHAOTIC STREAM CIPHER                                                | 125    |

| 6.1 Introduction                                                     | 125    |

| 6.2 The Cryptosystem                                                 | 126    |

| 6.3 Cryptosystem Implementation Overview                             | 127    |

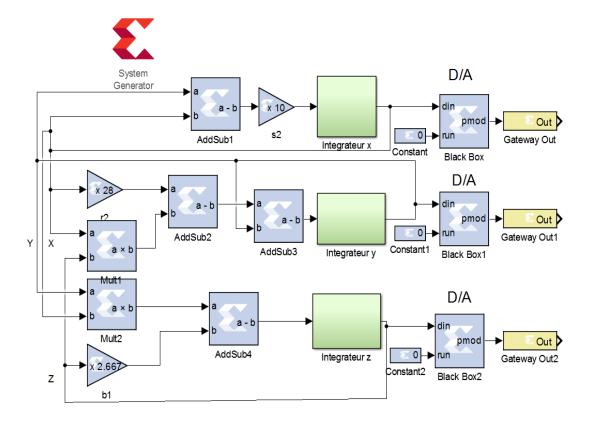

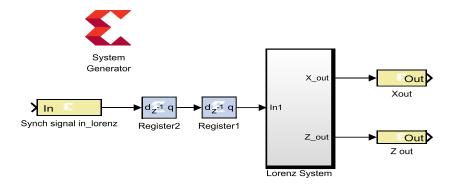

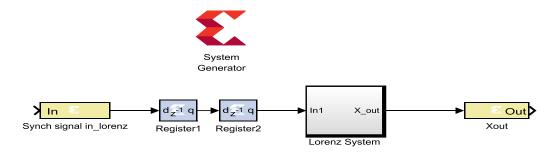

| 6.4 Implementation of the Lorenz Model                               | 129    |

| 6.5 Implementation of the Transmitter                                | 133    |

| 6.5.1 User data spreading                                            | 137    |

| 6.5.2 A stream cipher where the encryption key is continuously chang | ing140 |

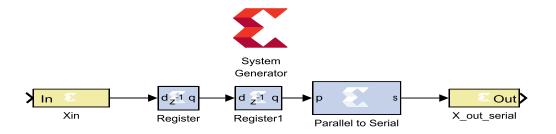

| 6.5.3 Parallel to serial                                             | 140    |

| 6.5.4 Manchester encoder                                             | 141    |

| 6.5.5 System clock rates                                             | 141    |

| 6.6 Integrated Synthesis Environment (Xilinx ISE) of the transmitter | 142 |

|----------------------------------------------------------------------|-----|

| 6.6.1 Device utilisation summary                                     | 142 |

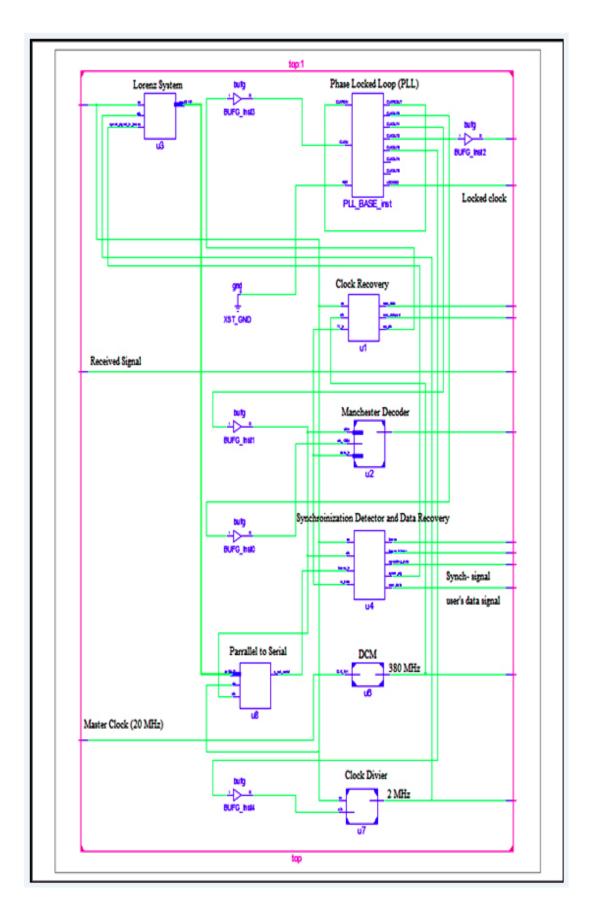

| 6.7 Implementation of the Receiver                                   | 143 |

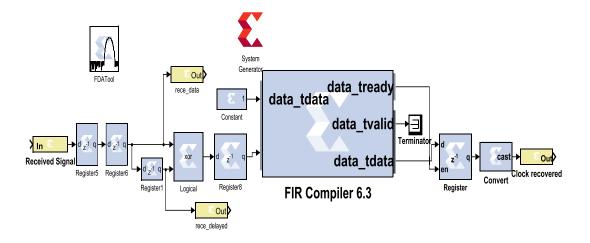

| 6.7.1 Clock recovery                                                 | 145 |

| 6.7.2 System clock rates                                             | 145 |

| 6.7.3 Manchester decoder                                             | 146 |

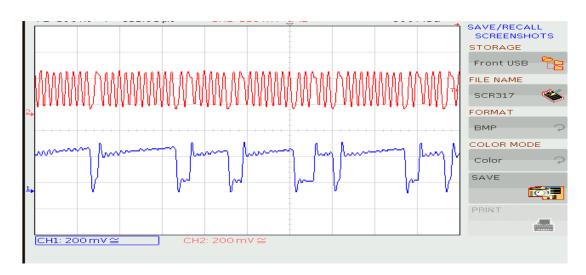

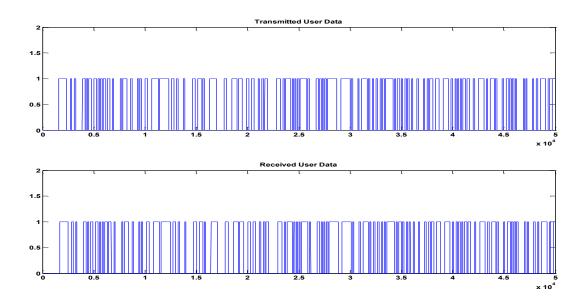

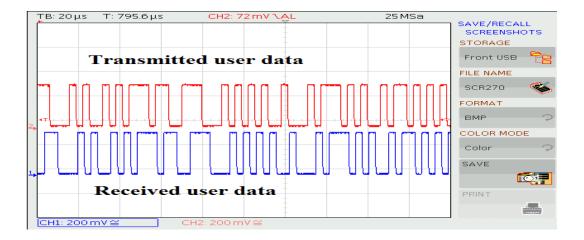

| 6.7.4 User data recovery results                                     | 147 |

| 6.8 Integrated Synthesis Environment (Xilinx ISE) of the receiver    | 149 |

| 6.8.1 Device utilisation summary                                     | 151 |

| 6.9 Cryptanalysis of the Stream cipher                               | 151 |

| 6.9.1 Randomness test of the Lorenz stream cipher                    | 151 |

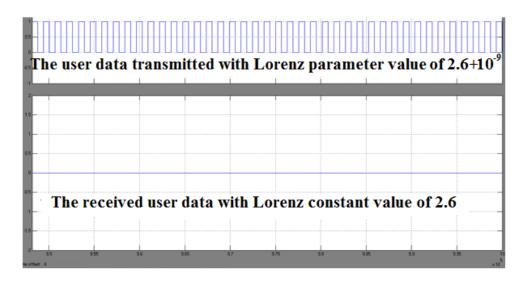

| 6.9.2 Sensitivity of mismatched key.                                 | 152 |

| 6.10 Conclusion                                                      | 153 |

| Conclusion and future work                                           | 154 |

| Reference                                                            | 158 |

# **List of Figures**

| Fig. 1.1. Basic Diagrams of Block and Stream Ciphers                                        | 2   |

|---------------------------------------------------------------------------------------------|-----|

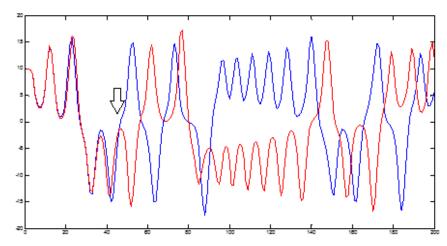

| Fig. 1.2. Responses of Two Lorenz Systems with Different Initial Conditions                 | 4   |

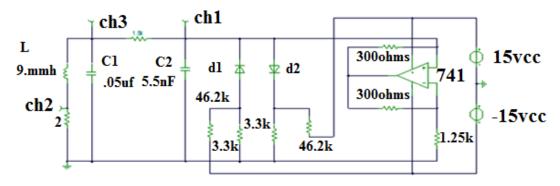

| Fig. 1.3. The Chua Circuit                                                                  | 7   |

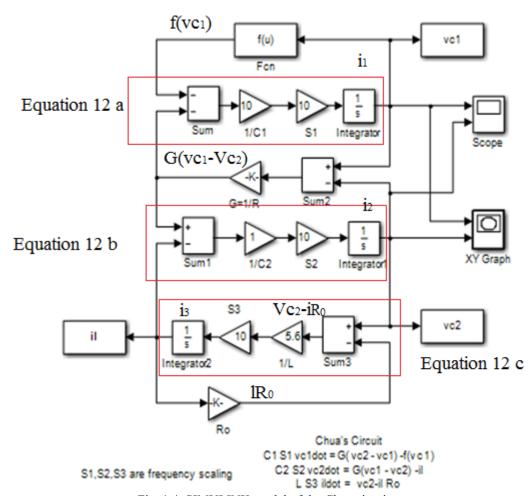

| Fig. 1.4. SIMULINK model of the Chua circuit.                                               | 8   |

| Fig. 1.5. Simulated signals of the Chua circuit. (a) vC1 Signal and (b) vC2 signal.         | 9   |

| Fig. 1.6. The vC1-vC2 attractor.                                                            | 9   |

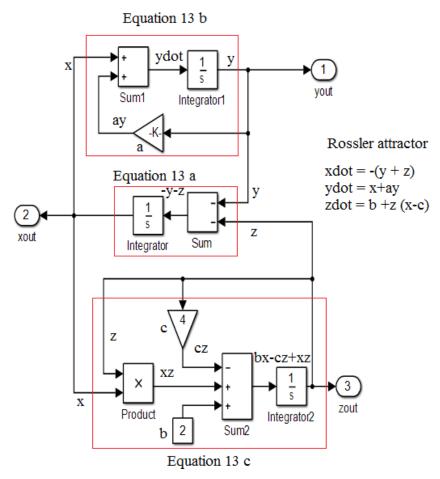

| Fig. 1.7. SIMULINK model of The Rössler.                                                    | .10 |

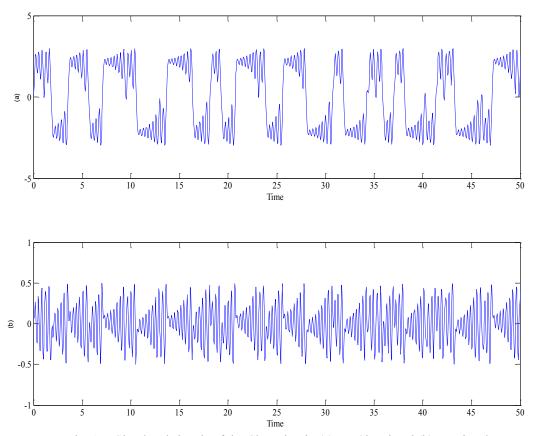

| Fig. 1.8. The Rössler system, (a) The x signal and (b) The y signal                         | .11 |

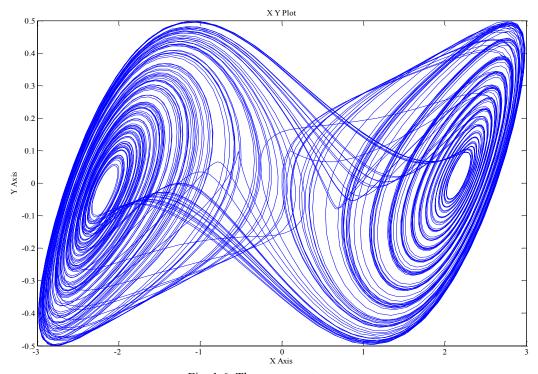

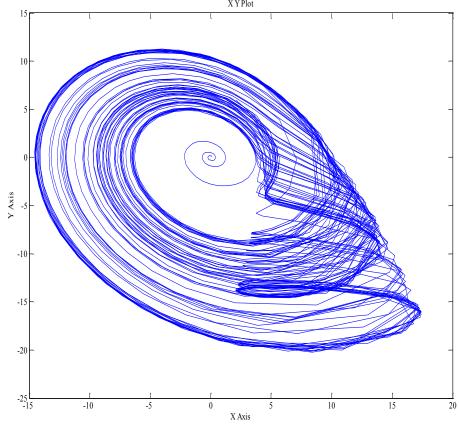

| Fig. 1.9. The <i>x-y</i> attractor of the Rössler system.                                   | .11 |

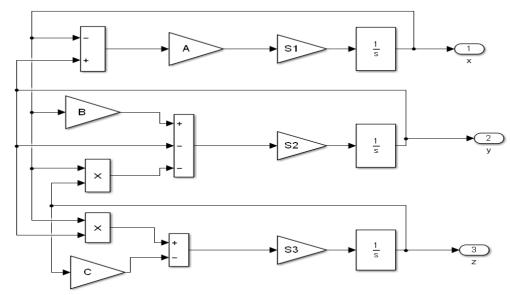

| Fig. 1.10. SIMULINK model of The Lorenz system.                                             | .12 |

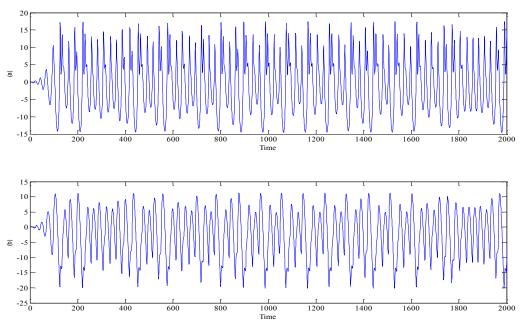

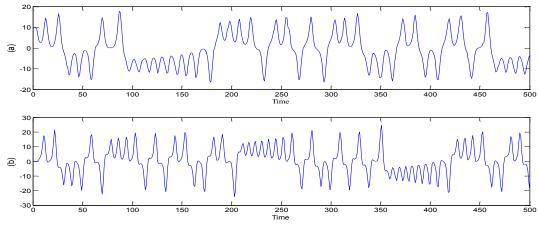

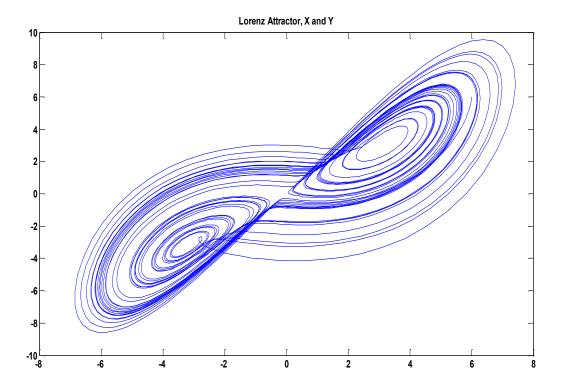

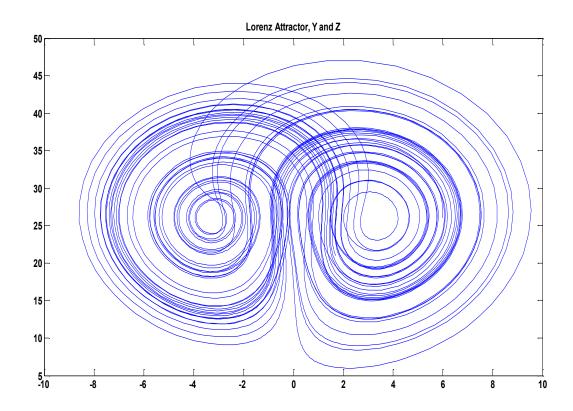

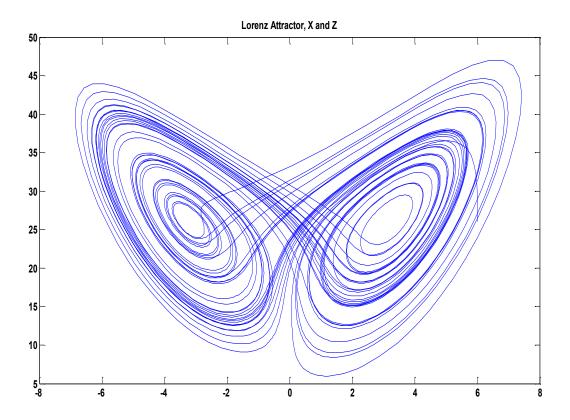

| Fig. 1.11. The simulated signals of the Lorenz System. (a) x signal and (b) y signal        |     |

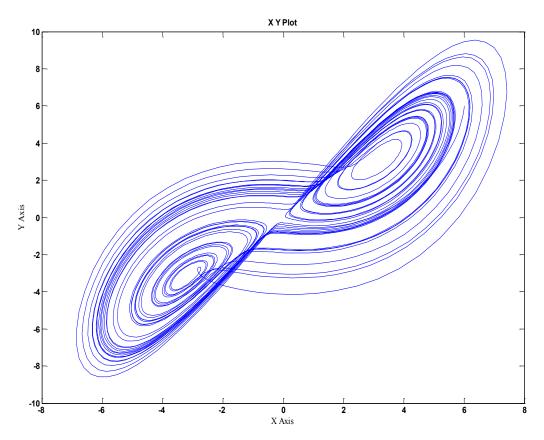

| Fig. 1.12. The <i>x-y</i> attractor of the Lorenz system.                                   |     |

| Fig. 1.13. Block Diagram of the Baseband System.                                            |     |

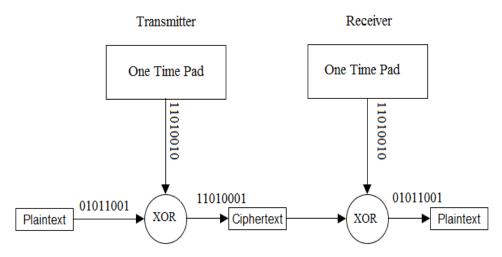

| Fig. 3.1 Block diagram of the one-time pad scheme. 35                                       |     |

| Fig. 3.2. Block diagram of cryptosystem.                                                    | .37 |

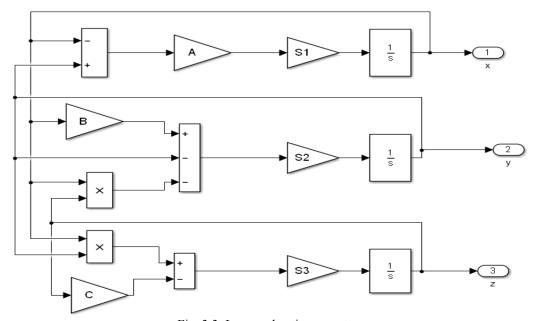

| Fig. 3.3. Lorenz chaotic generator.                                                         | .38 |

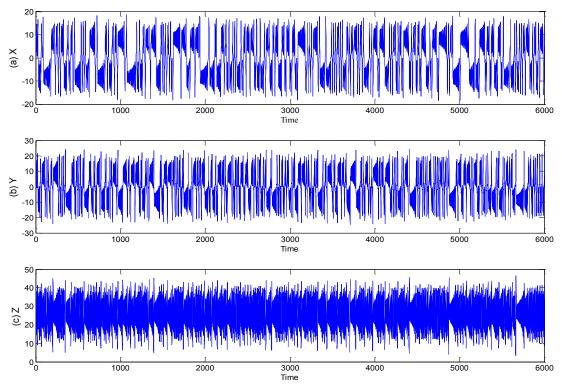

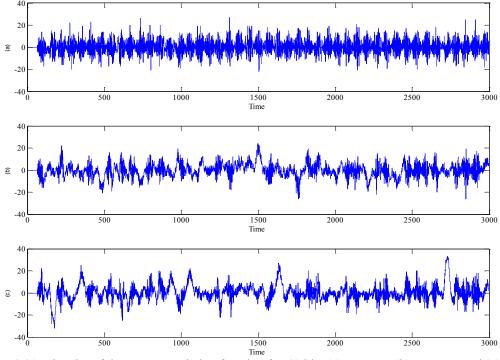

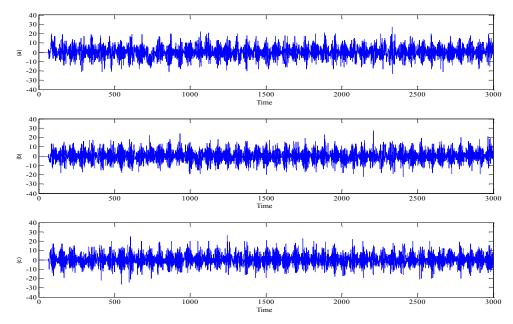

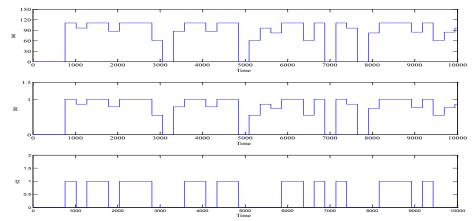

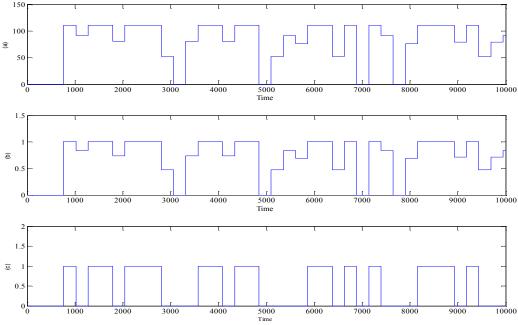

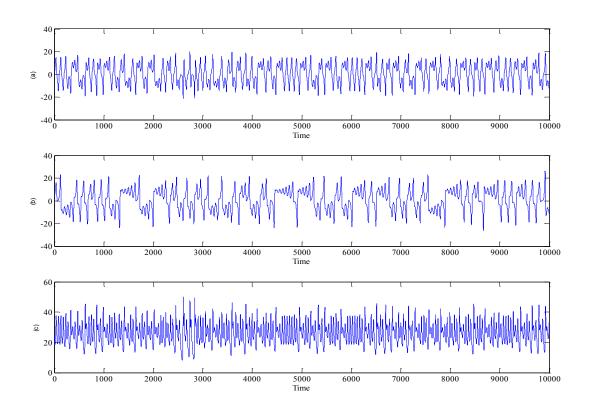

| Fig. 3.4. Lorenz state variables. (a) x-state variable, (b) y-state variable and (c) z-     |     |

| state variable                                                                              | .39 |

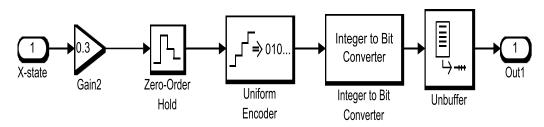

| Fig. 3.5. Analogue-to-digital signal convertor.                                             | .39 |

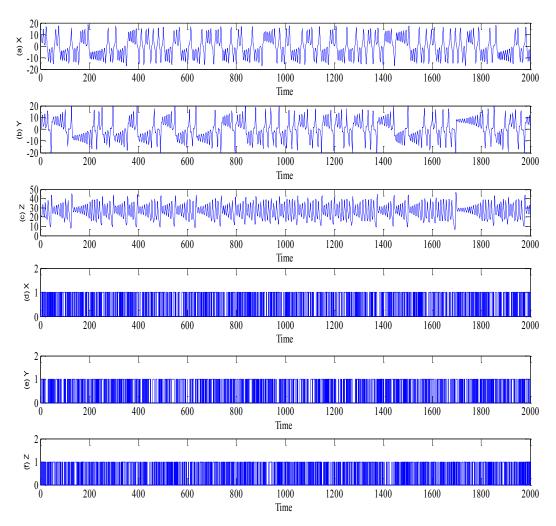

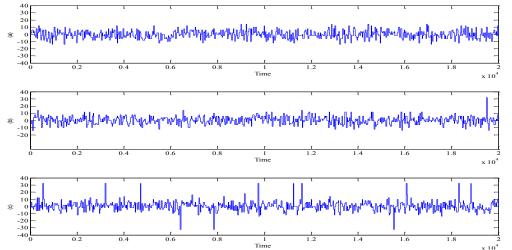

| Fig. 3.6. Analogue chaotic signal converted to digital signal. (a) Analogue signal of       | of  |

| x-state variable, (b) Analogue signal of y-state variable, (c) Analogue signal of z-        |     |

| state variable, (d) Digital signal x-state variable, (e) Digital signal of y-state variable | ole |

| and (f) Digital signal of z-state variable.                                                 | .40 |

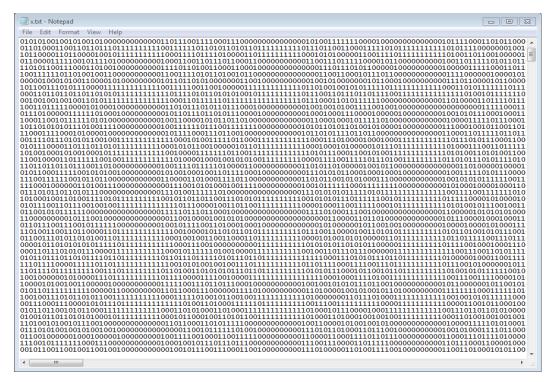

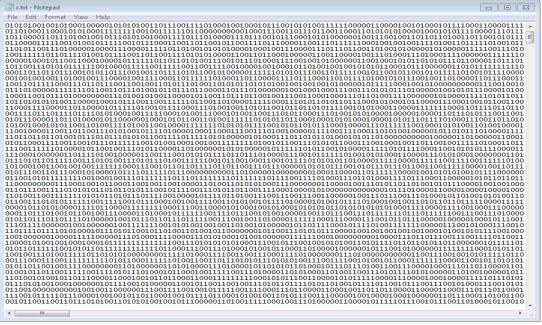

| Fig. 3.7. x-state bit stream before scrambling which shows long repetition of ones          |     |

| and zeros                                                                                   | .41 |

| Fig. 3.8. Scrambling scheme of the Lorenz signals.                                          |     |

| Fig. 3.9. The bit stream after scrambling.                                                  | .42 |

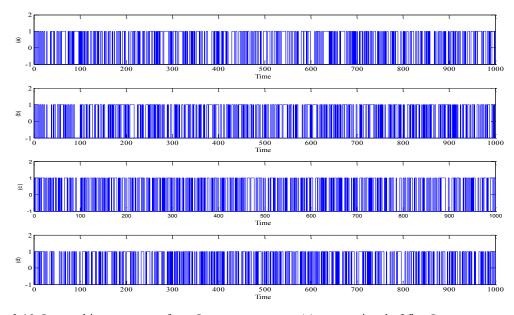

| Fig. 3.10. Lorenz binary stream of two Lorenz generators. (a) x-state signal of first       | t   |

| Lorenz generator, (b) x-state signal of second Lorenz generator, (c) z-state signal of      | of  |

| first Lorenz generator and (d) z-state signal of second Lorenz generator                    | .43 |

| Fig. 3.11. The plot of the cross-correlation function for 32-bits (a) x xcorr y (b) x       |     |

| xcorr z and (c) y xcorr z.                                                                  | .44 |

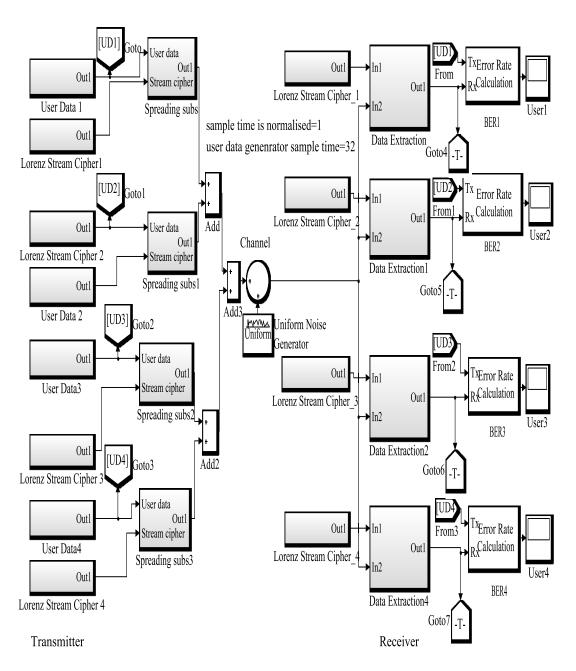

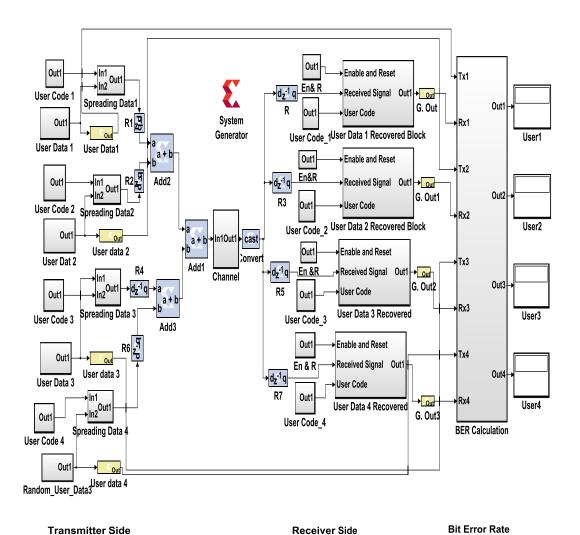

| Fig. 3.12. A four-user digital communication system based on a Lorenz stream                |     |

| cipher                                                                                      |     |

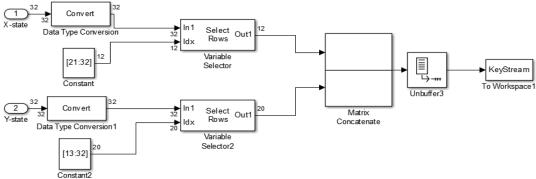

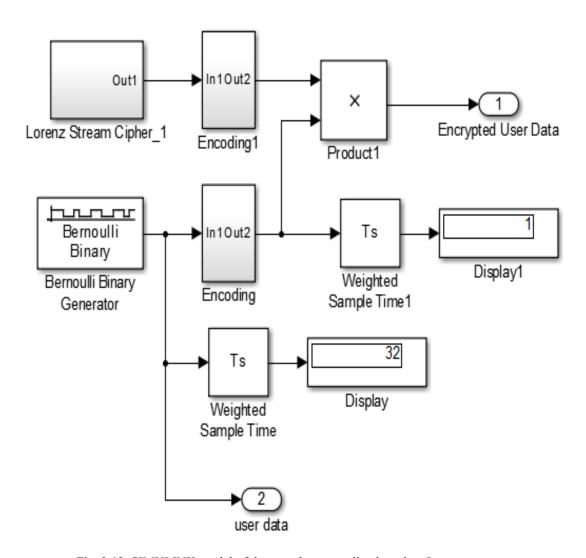

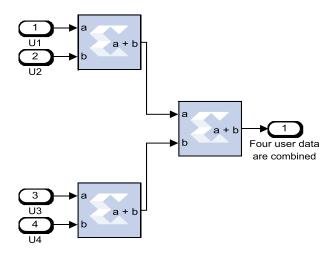

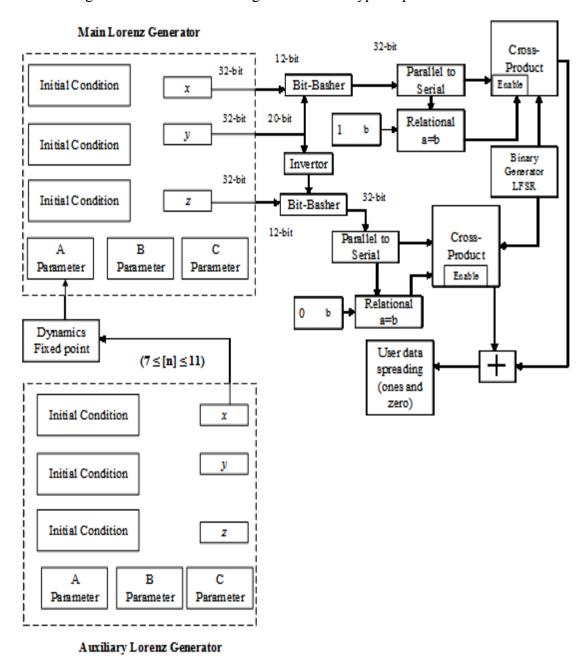

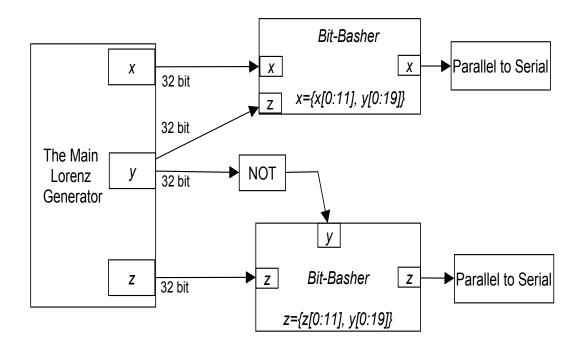

| Fig. 3.13. SIMULINK model of the user data spreading based on Lorenz system                 | .46 |

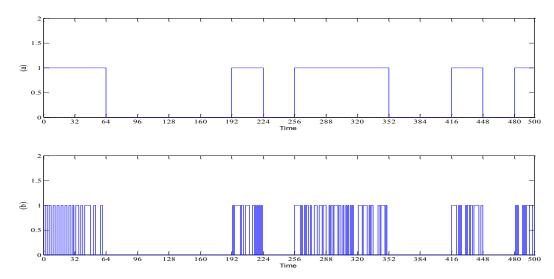

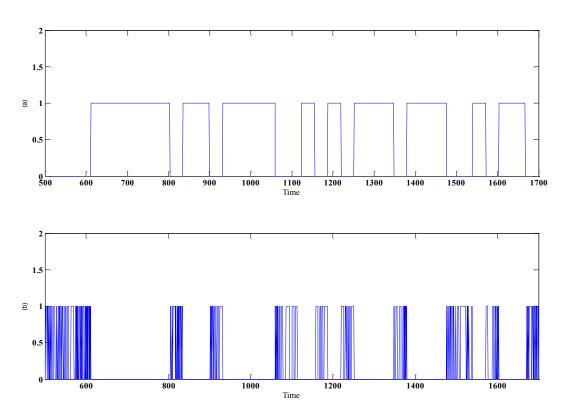

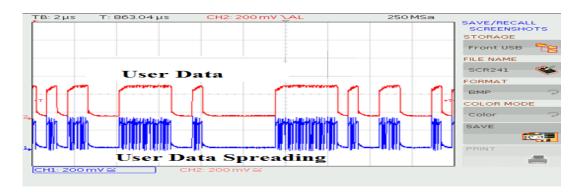

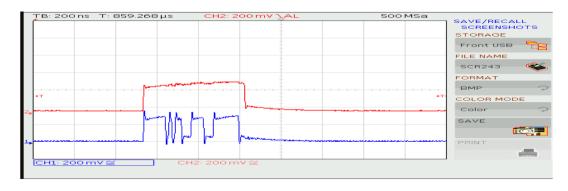

| Fig. 3.14. Simulation results of user data spreading. (a) Information signal, and (b)       | )   |

| Spreading the information signal using 32-bits length.                                      | .47 |

| Fig. 3.15. The bipolar encoding scheme.                                                     | .47 |

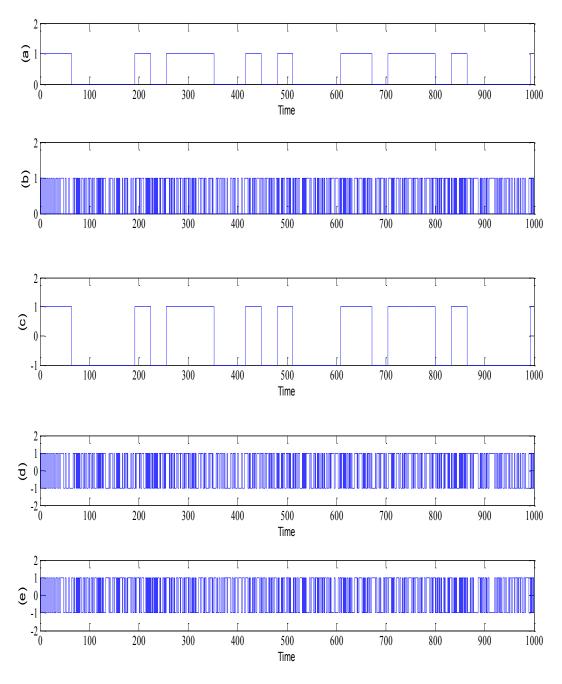

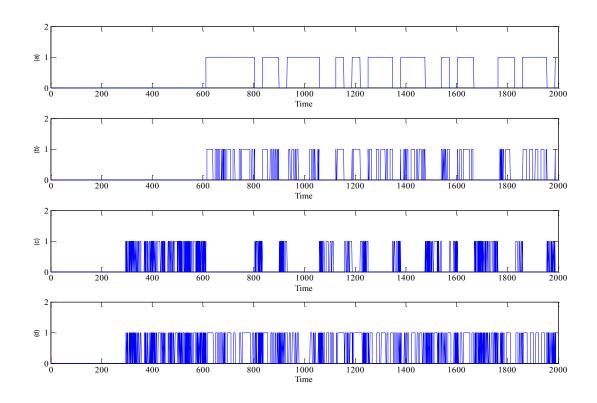

| Fig. 3.16. SIMULINK results of the user data encryption process. (a) Information             |

|----------------------------------------------------------------------------------------------|

| signal, (b) Lorenz binary stream, (c) Information signal is encoded to bipolar, (d)          |

| Lorenz binary stream is encoded to bipolar and (e) Encrypted information signal48            |

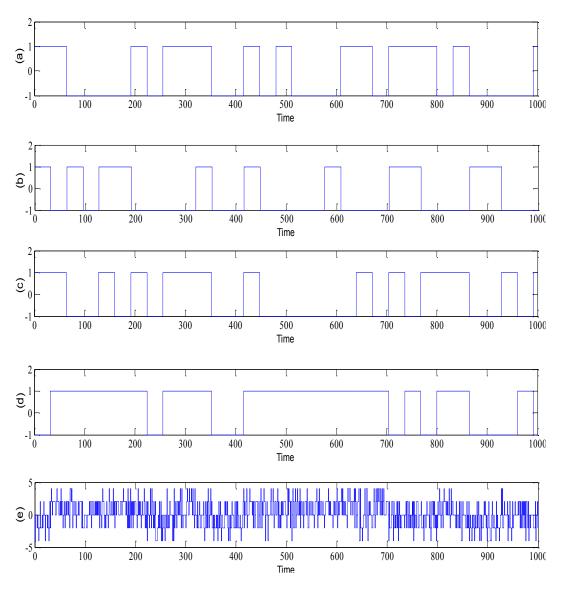

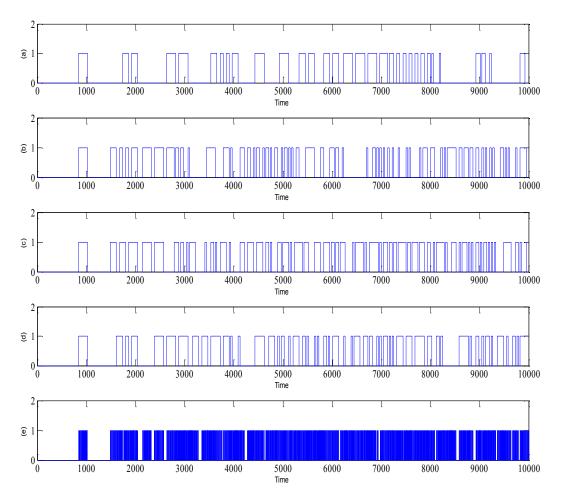

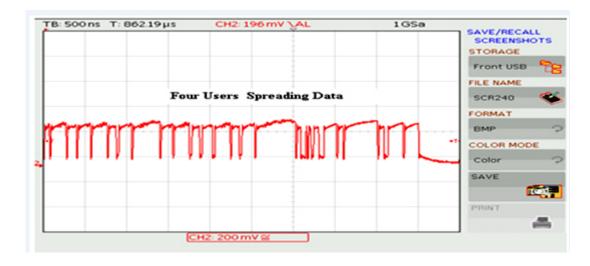

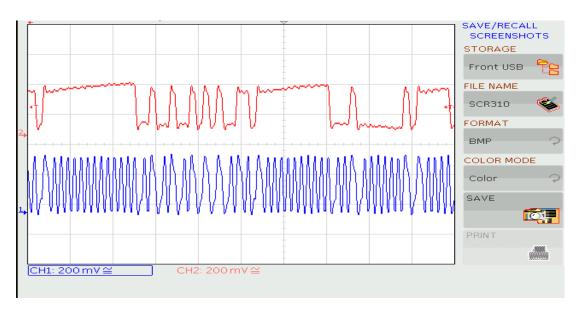

| Fig. 3.17. SIMULINK results for combined four user data. (a) User data 1, (b) User           |

| data 2, (c) User data 3, (d) User data 4, and (e) All four user data are combined49          |

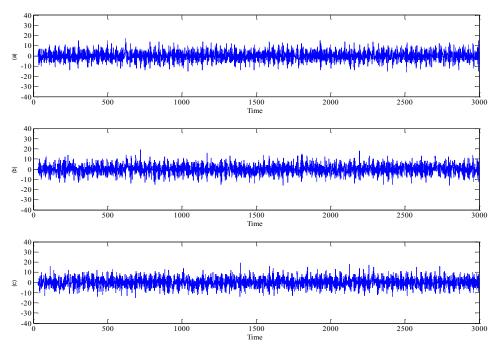

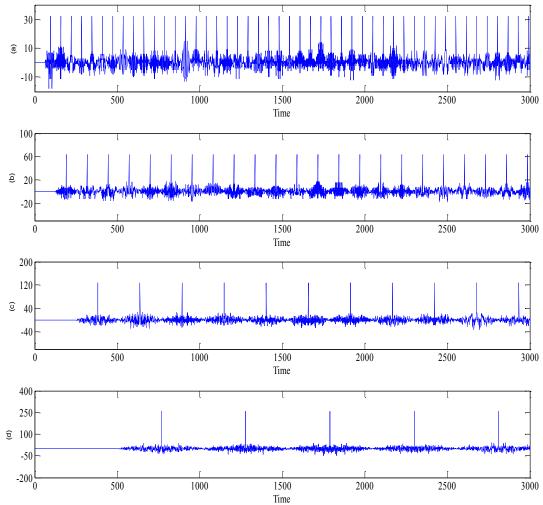

| Fig. 3.18. The plot of the auto-correlation function. (a) Auto-correlation function of       |

| 32-bits long, (b) Auto-correlation function of 64-bits long, (c) Auto-correlation            |

| function of 128-bits long and (d) Auto-correlation function of 256 bit-long50                |

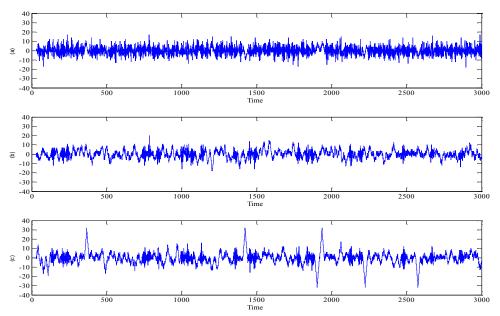

| Fig. 3.19. The plot of the cross-correlation function for 32-bits (a) x xcorr y (b) x        |

| xcorr z and (c) y xcorr z                                                                    |

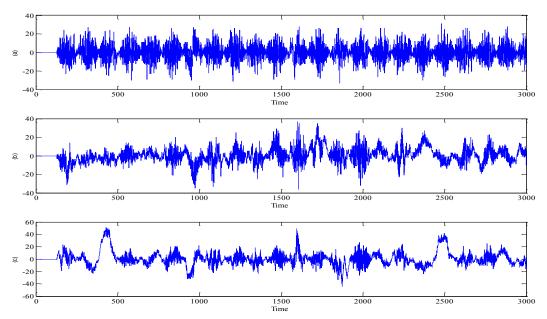

| Fig. 3.20. The plot of the cross-correlation function for 64-bits (a) x xcorr y (b) x        |

| xcorr z and (c) y xcorr z                                                                    |

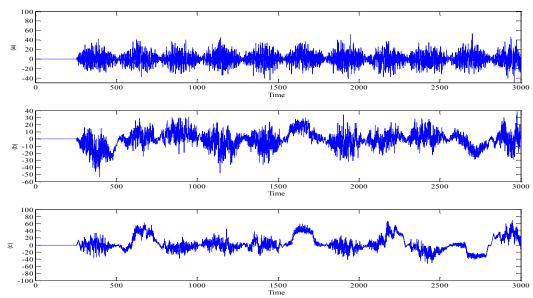

| Fig. 3.21. The plot of the cross-correlation function for 128-bits (a) x xcorr y (b) x       |

| xcorr z and (c) y xcorr z                                                                    |

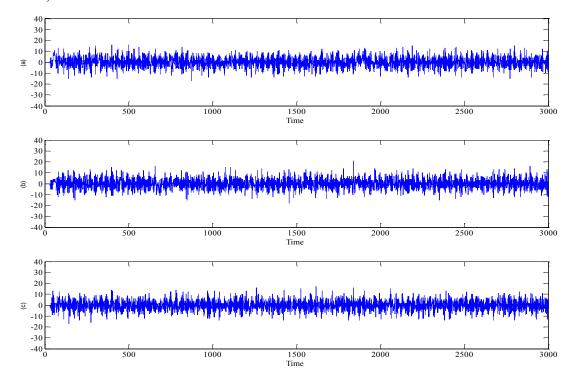

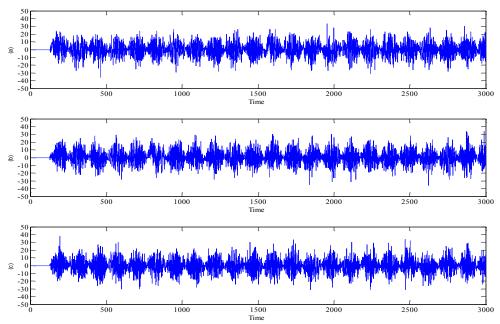

| Fig. 3.22. The plot of the cross-correlation function for 256-bits (a) x xcorr y (b) x       |

| xcorr z and (c) y xcorr z                                                                    |

| Fig. 3.23. The plot of the cross-correlation function for 32-bits (a) x xcorr y (b) x        |

| xcorr z and (c) y xcorr z                                                                    |

| Fig. 3.24. The plot of the cross-correlation function for 64-bits (a) x xcorr y (b) x        |

| xcorr z and (c) y xcorr z                                                                    |

| Fig. 3.25. The plot of the cross-correlation function for 128-bits (a) x xcorr y (b) x       |

| xcorr z and (c) y xcorr z                                                                    |

| Fig. 3.26. The plot of the cross-correlation function for 128-bits (a) x xcorr y (b) x       |

| xcorr z and (c) y xcorr z. 55                                                                |

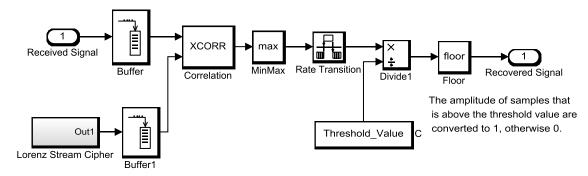

| Fig. 3.27. De-spreading using cross-correlation block                                        |

| Fig. 3.28. De-spreading process. (a) Signal after dot-product. (b) Signal after division     |

| block and (c) Signal after floor                                                             |

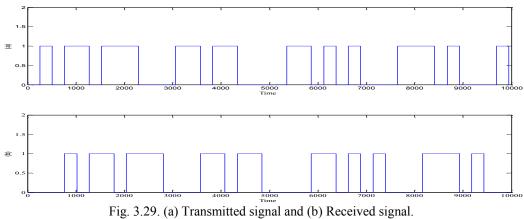

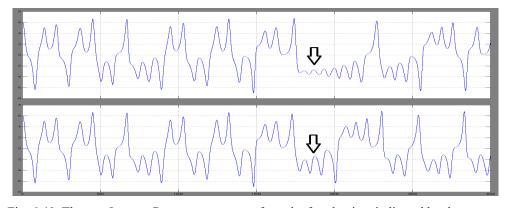

| Fig. 3.29. (a) Transmitted signal and (b) Received signal                                    |

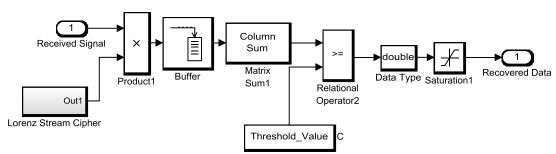

| Fig. 3.30. De-spreading using cross product and summation                                    |

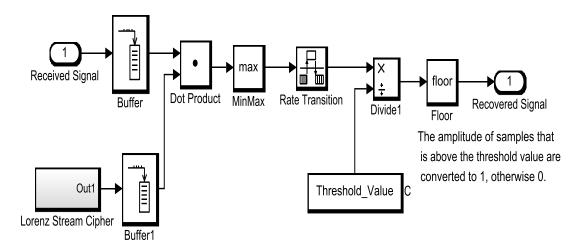

| Fig. 3.31. De-spreading based on dot product                                                 |

| Fig. 3.32. De-spreading process. (a) Signal after dot-product. (b) Signal after division     |

| block and (c) signal after floor                                                             |

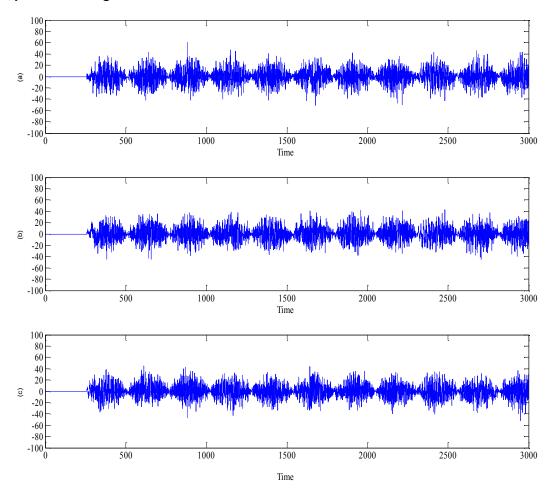

| Fig. 3.33. Simulation results of product and summation for 32-bits. (a) $x$ and $y$ ,(b) $x$ |

| and z and (c) y and z                                                                        |

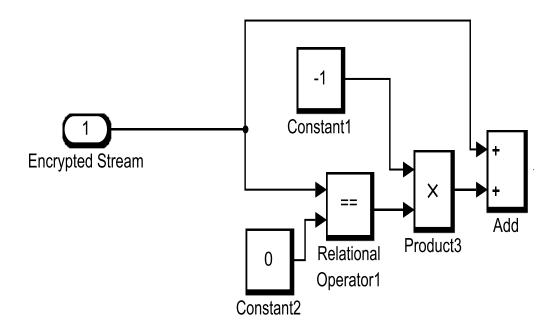

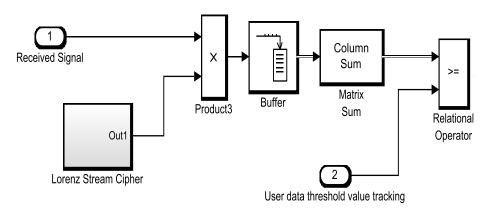

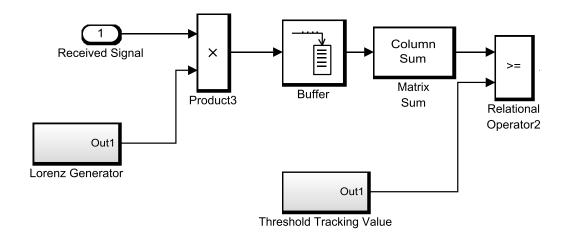

| Fig. 3.34. SIMULINK block diagram of the data extraction process                             |

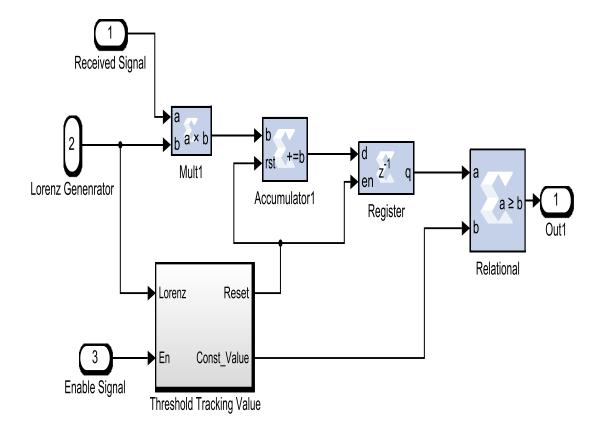

| Fig. 3.35. SIMULINK block diagram of the user data threshold tracking value60                |

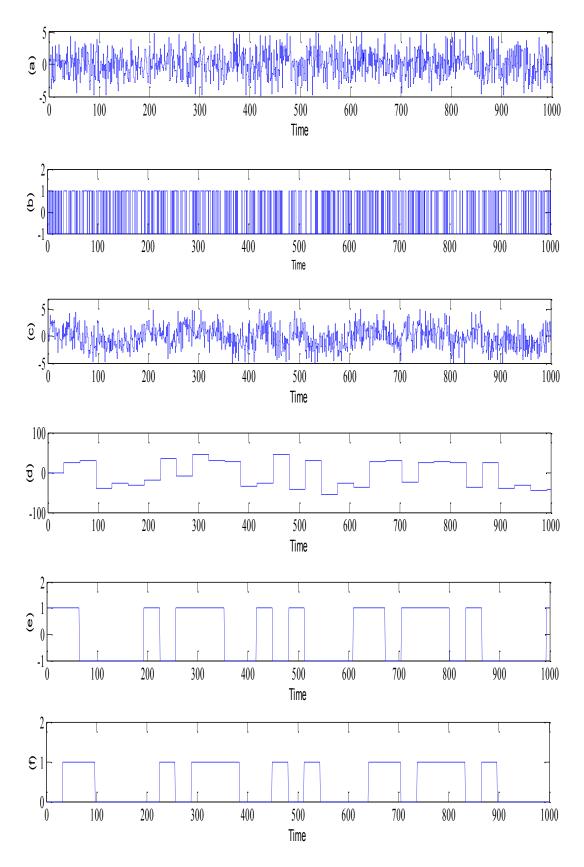

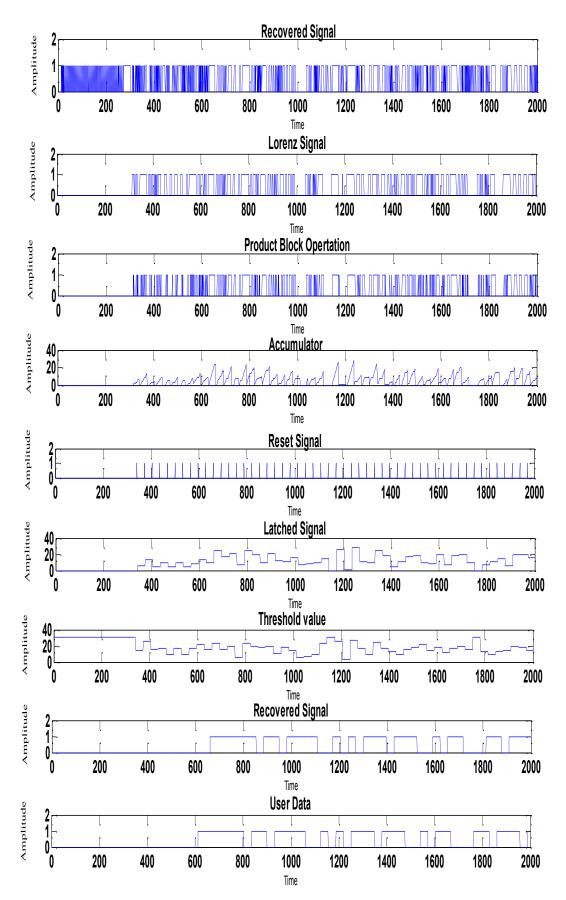

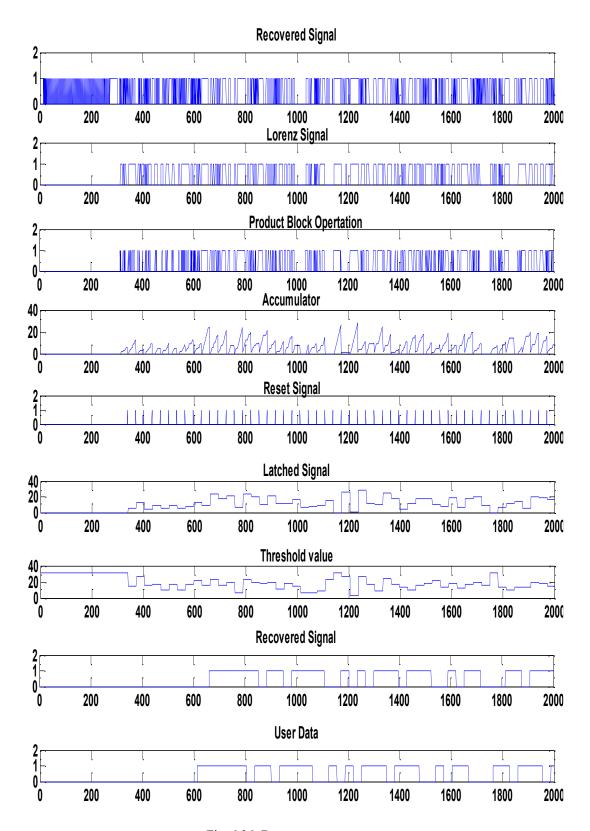

| Fig. 3.36. User data extraction process.(a) Lorenz chaotic signal, (b) Multiplication        |

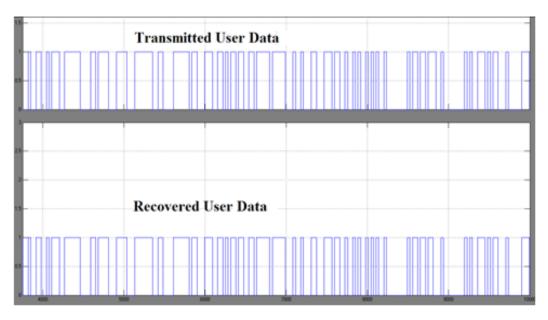

| process, (c) accumulator, (e) User data transmitted and (f) Recovered data61                 |

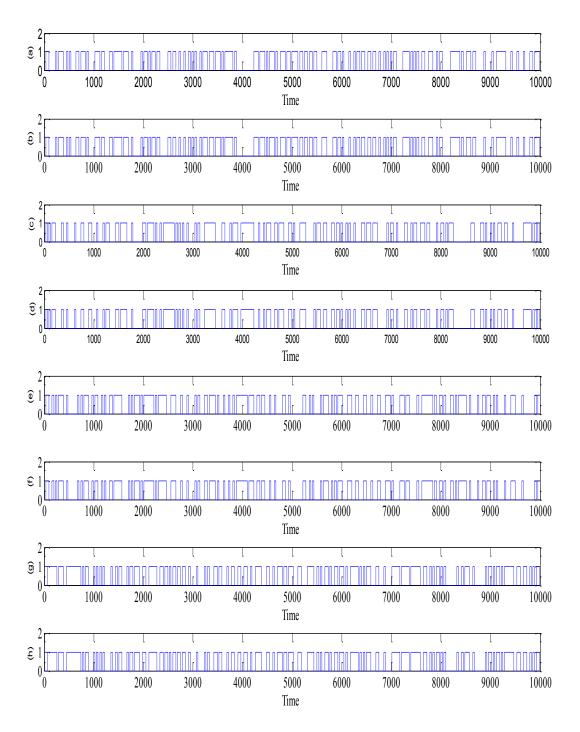

| Fig. 3.37. Four user data transmitted and recovered. (a) User data 1, (b) user data 1        |

| recovered, (c) user data 2, (d) user data 2 recovered, (e) user data 3, (f) user data 4      |

| recovered. (g) user data 4, and (h) user data 4 recovered.                                   |

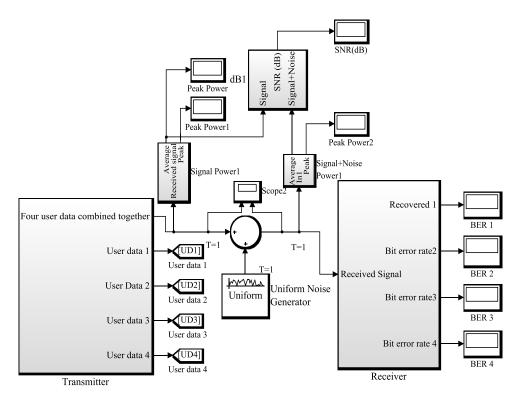

| Fig. 3.38. The Lorenz stream cipher for four users with added noise, viewed in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| SIMULINK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63           |

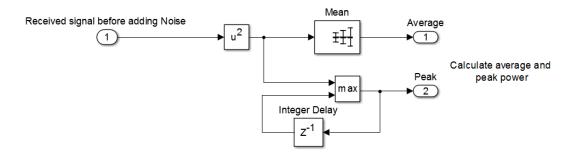

| Fig. 3.39. SIMULINK block diagram of the average and peak power subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64           |

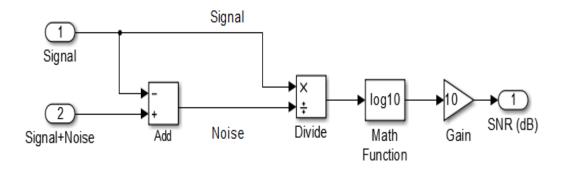

| Fig. 3.40. SIMULINK block diagram of SNR calculation subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64           |

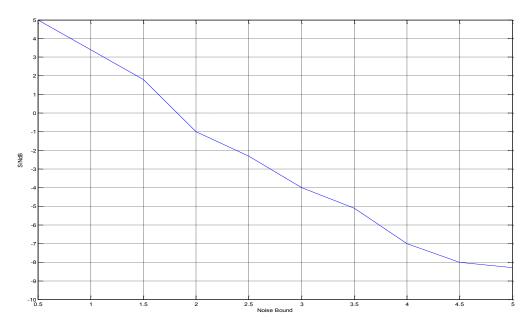

| Fig. 3.41. Upper noise bound vs. S/N (dB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65           |

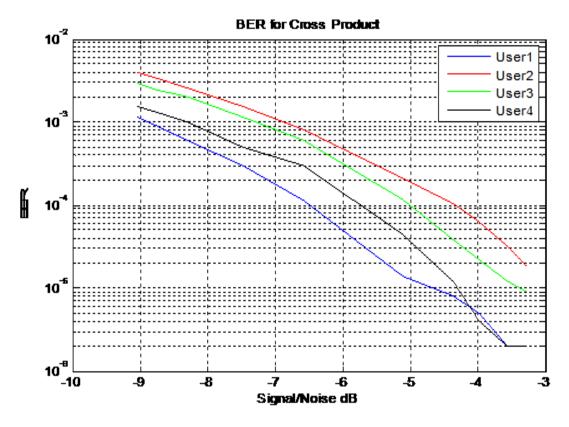

| Fig. 3.42. BER vs. signal-to-noise ratio.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66           |

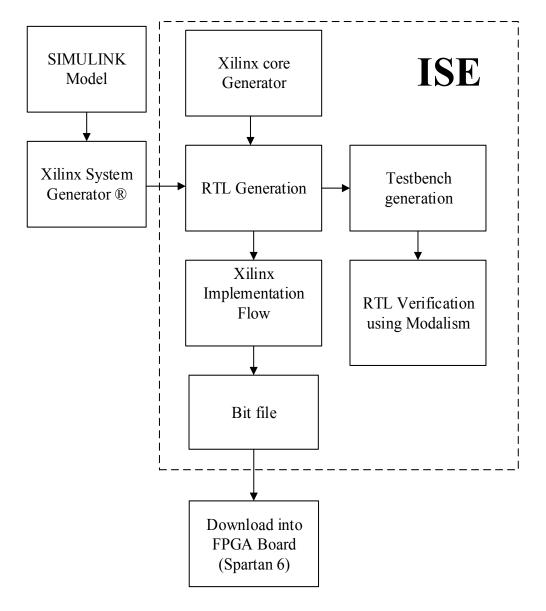

| Fig. 4.1. Basic block diagram of the design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71           |

| Fig. 4.2. SIMULINK blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| Fig. 4.3. Xilinx blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| Fig. 4.4. ISE project.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

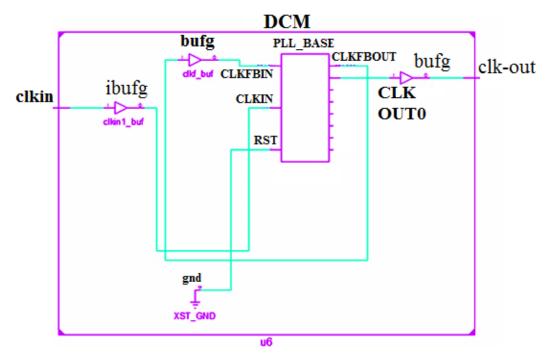

| Fig. 4.5. An example of the RTL schematic for the PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

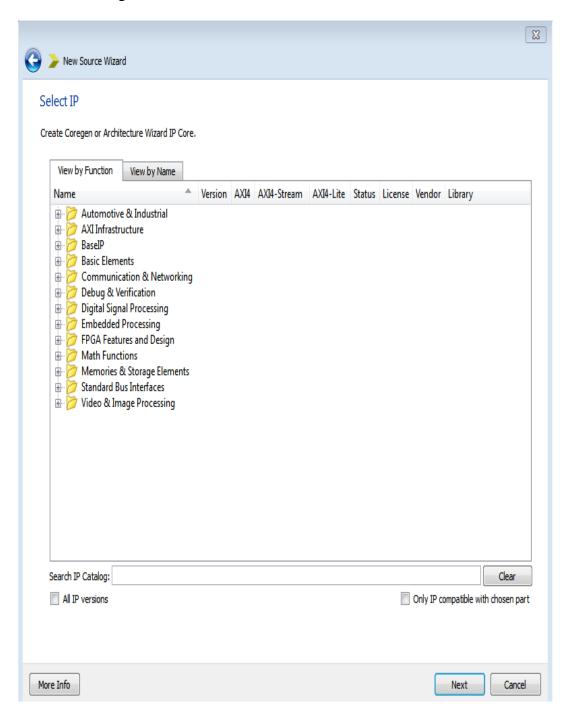

| Fig. 4.6. Xilinx core generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

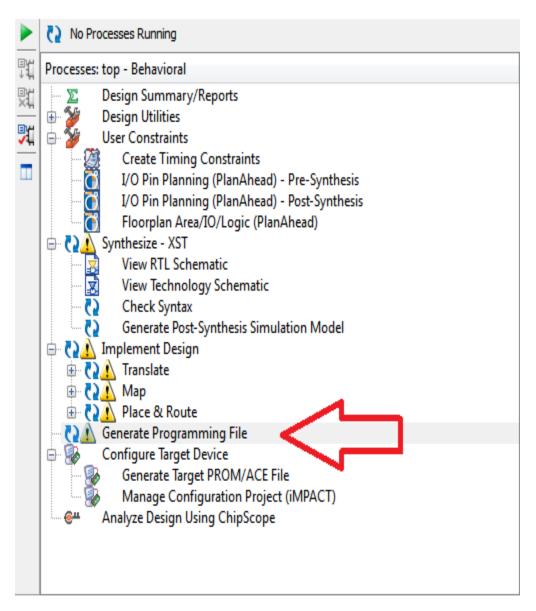

| Fig. 4.7. Generates Programing file (bit file).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

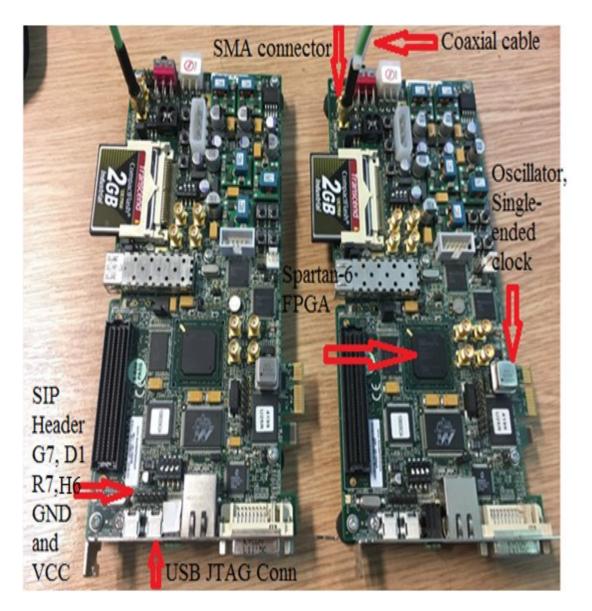

| Fig. 4.8. SP605 boards, transmitter and receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

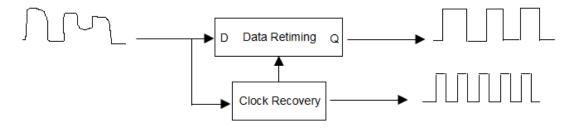

| Fig. 4.9. Clock recovery and data retiming for a CDR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

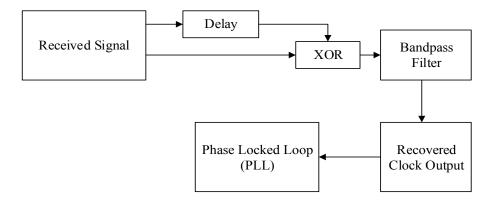

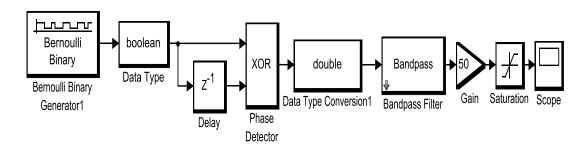

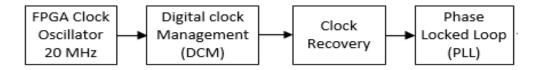

| Fig. 4.10. The basic blocks diagram of the clock recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

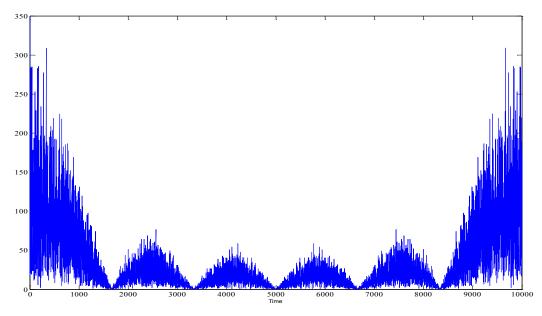

| Fig. 4.11. FFT of the random signal (Bernoulli binary generator).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

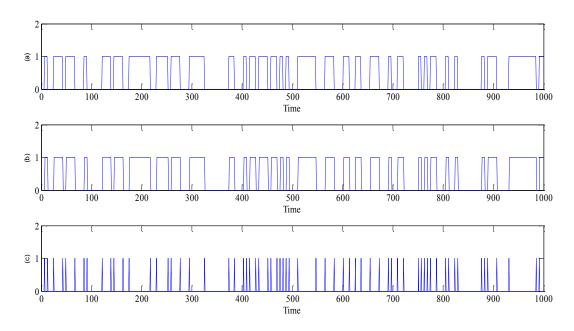

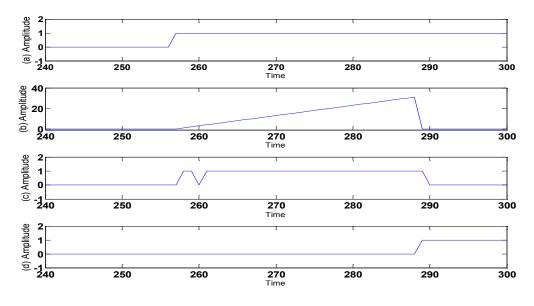

| Fig. 4.12. Simulated test, (a) Binary random generator (Bernoulli), (b) Delayed dates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| by one sample, (c) Rising and falling edge detections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| Fig. 4.13. FFT after delay multiply techniques are applied on the Bernoulli genera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| 11g. 4.15. 111 arter delay multiply techniques are applied on the Bernoulli genera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

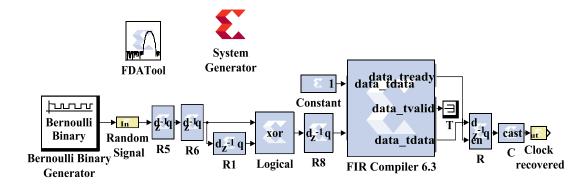

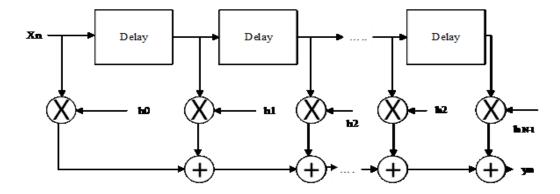

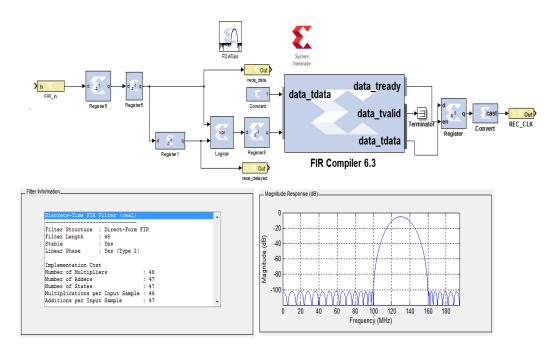

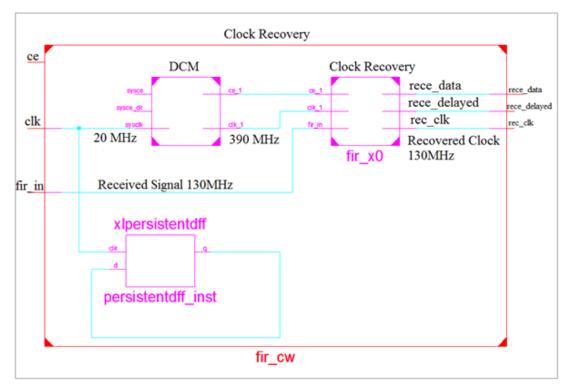

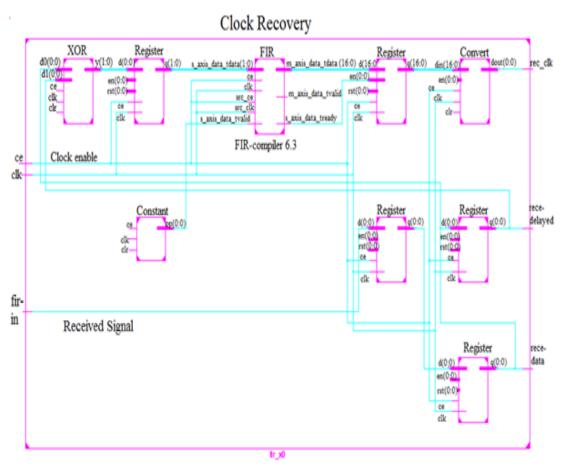

| Fig. 4.14. Clock recovery as viewed in the SIMULINK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

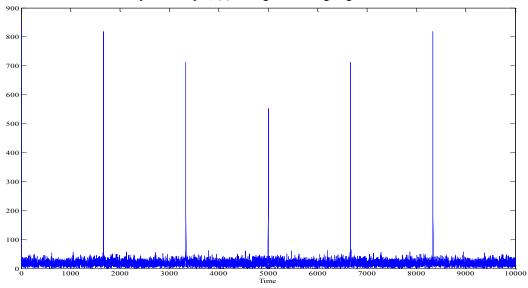

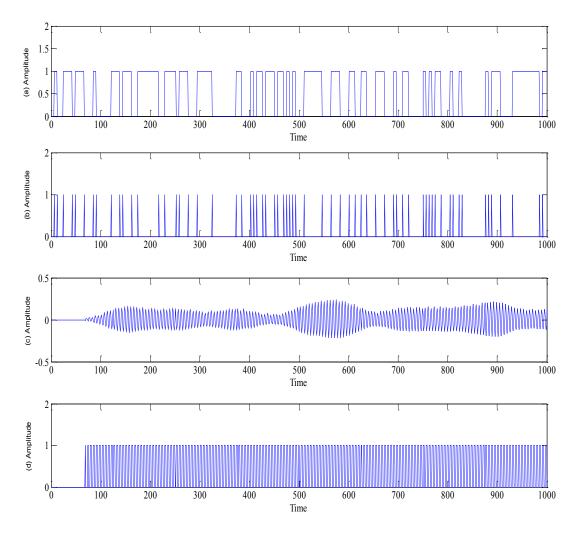

| Fig. 4.15. Simulated test of clock recovery based on SIMULINK, (a) Binary random simulated test of clock recovery based on SIMULINK, (b) Binary random simulated test of clock recovery based on SIMULINK, (a) Binary random simulated test of clock recovery based on SIMULINK, (b) Binary random simulated test of clock recovery based on SIMULINK, (b) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK, (c) Binary random simulated test of clock recovery based on SIMULINK sim |              |

| generator (Bernoulli), (b) Rising and falling edges detectors, (c) Bandpass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <i>J</i> 111 |

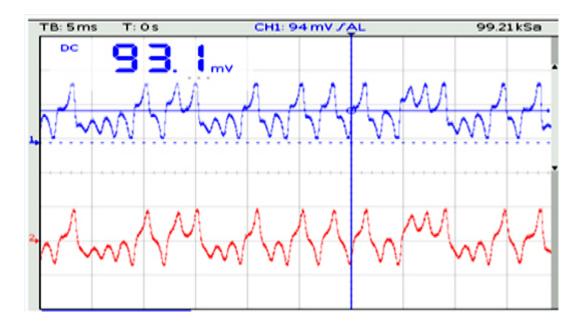

| response and (d) recovered clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 84           |

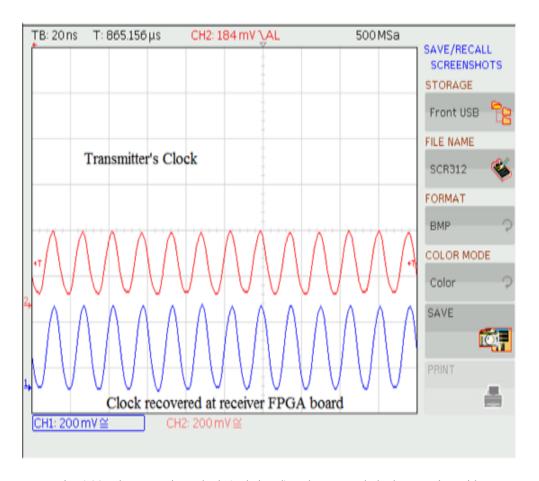

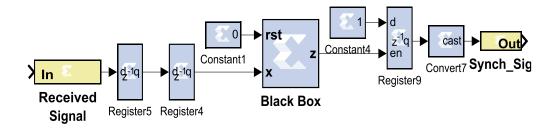

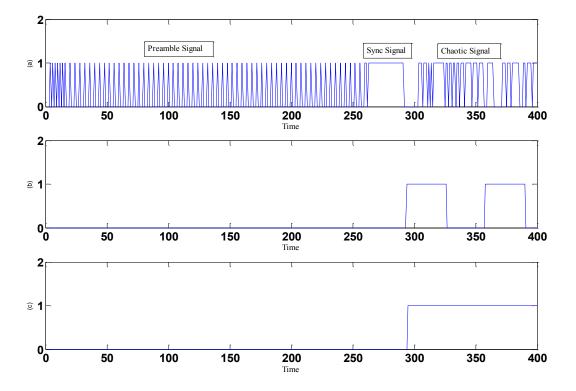

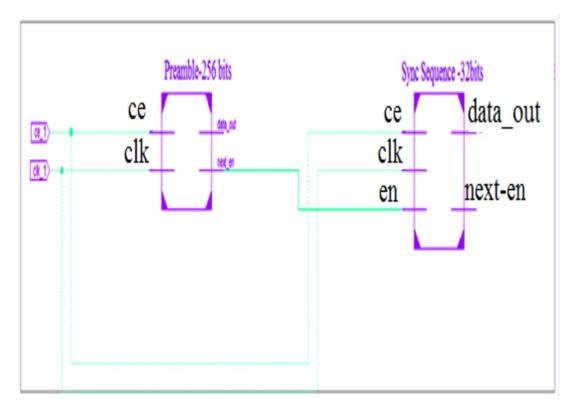

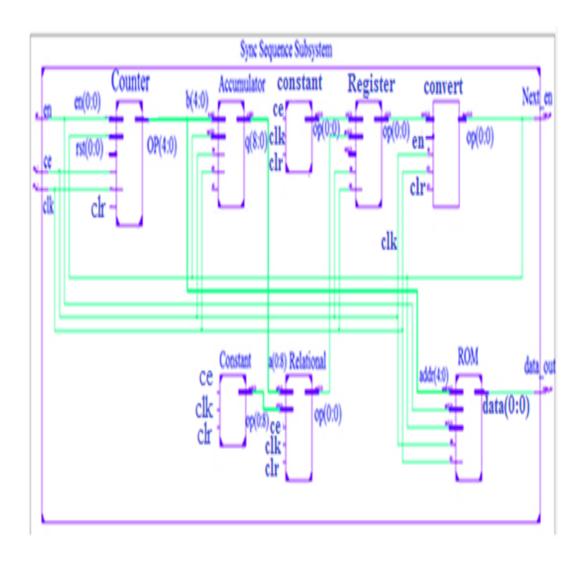

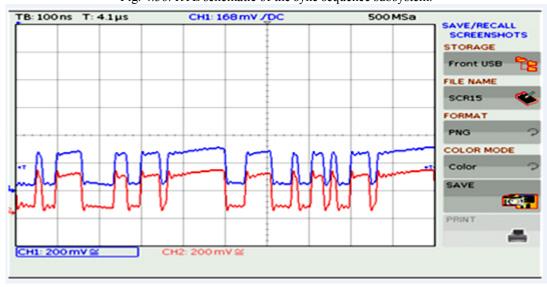

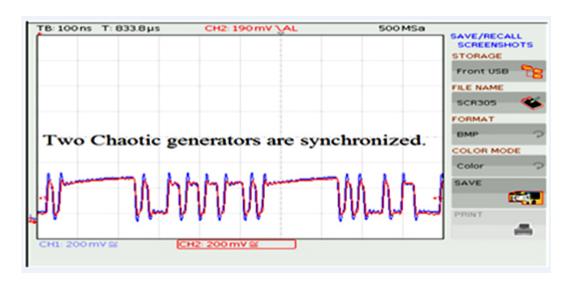

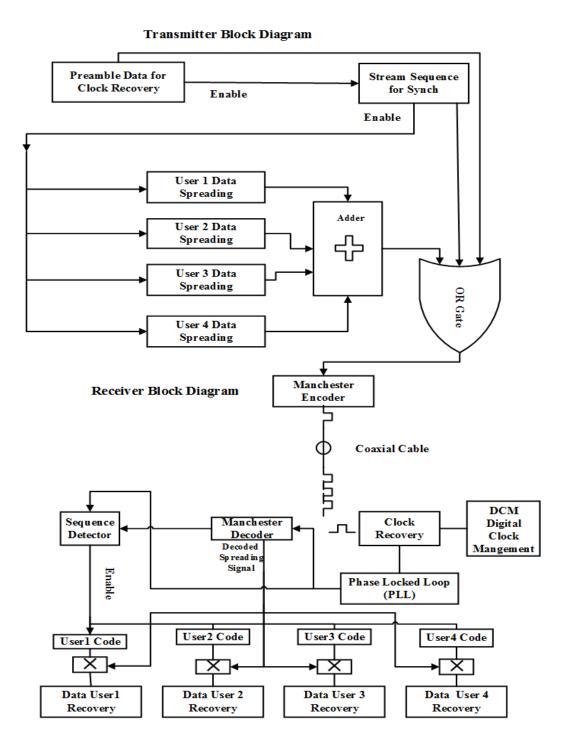

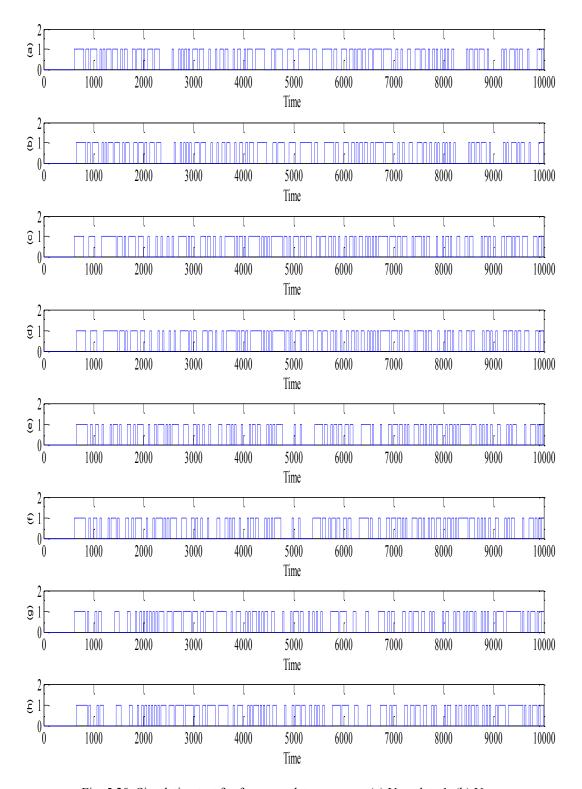

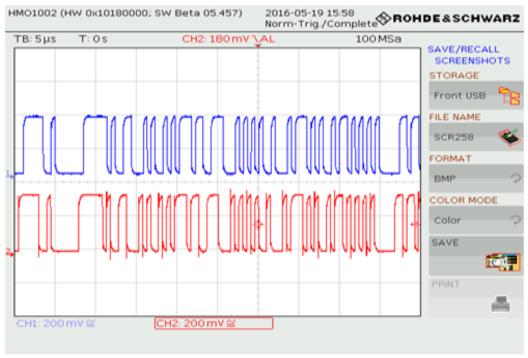

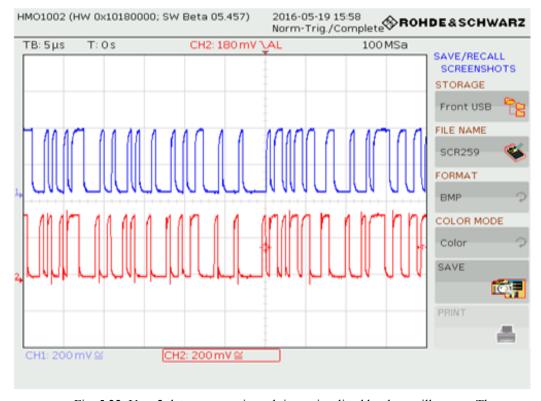

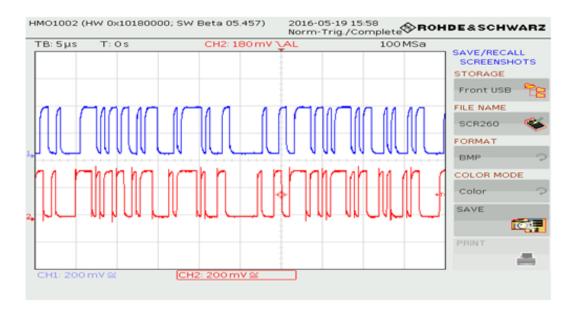

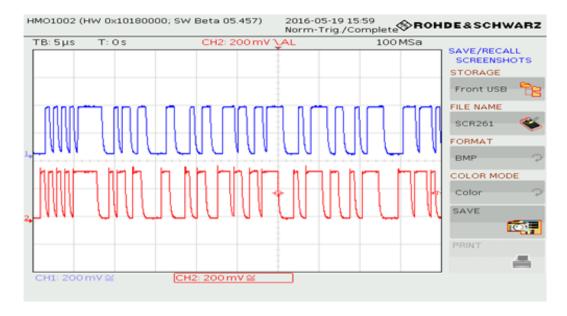

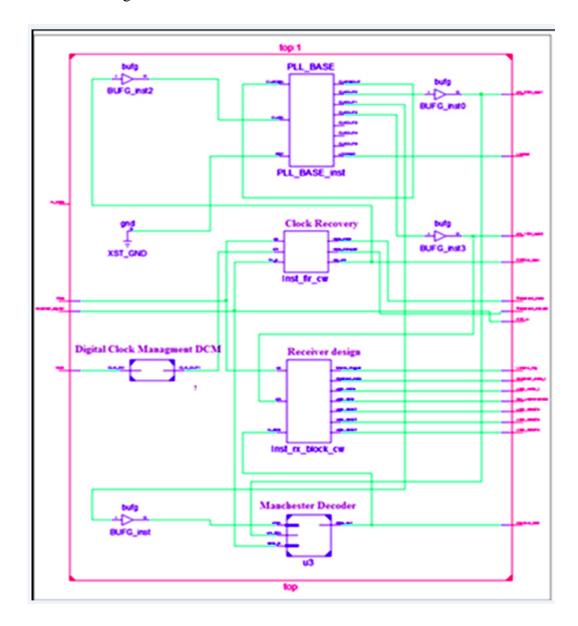

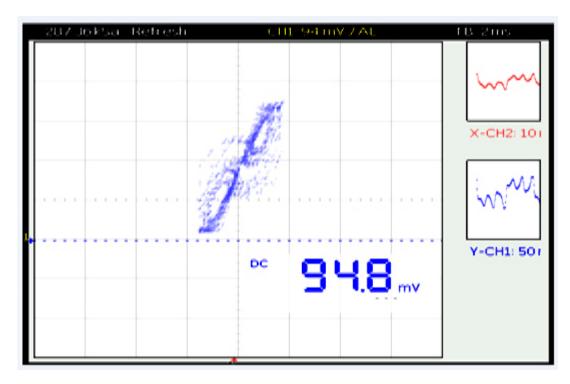

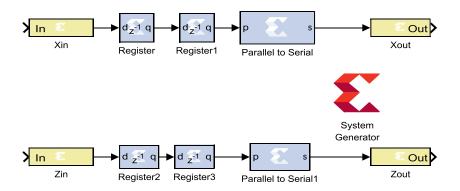

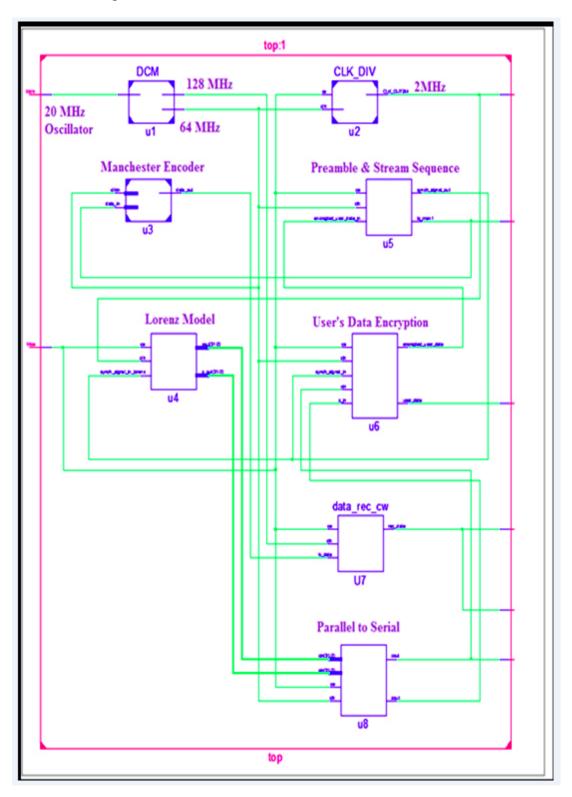

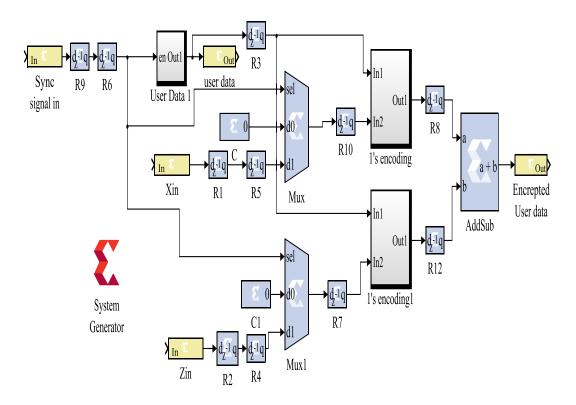

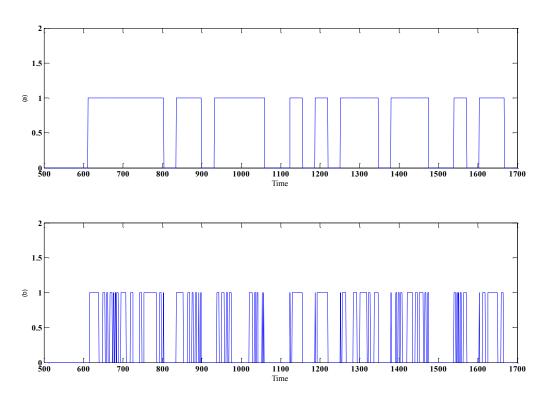

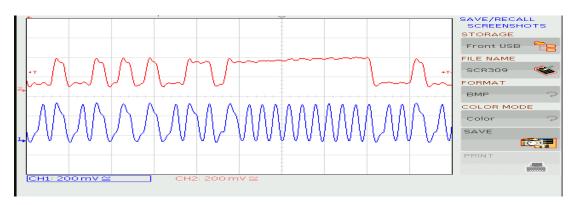

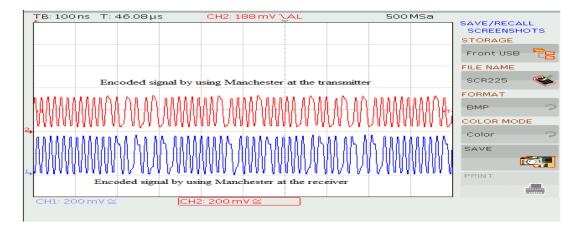

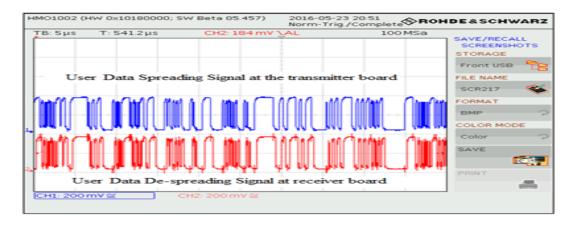

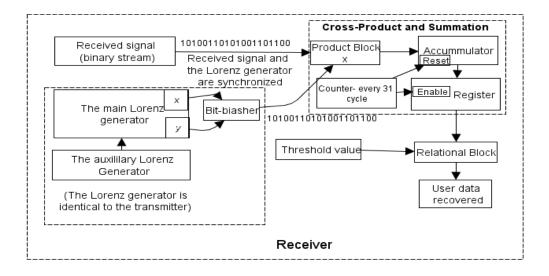

| Fig. 4.16. Clock recovery technique as viewed in the Xilinx System Generator®.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |