## **Kent Academic Repository**

# Rocha, Valdemar C. (1976) *Versatile Error-Control Coding Systems*. Doctor of Philosophy (PhD) thesis, University of Kent.

**Downloaded from** <u>https://kar.kent.ac.uk/94613/</u> The University of Kent's Academic Repository KAR

The version of record is available from https://doi.org/10.22024/UniKent/01.02.94613

This document version UNSPECIFIED

**DOI for this version**

## Licence for this version

CC BY-NC-ND (Attribution-NonCommercial-NoDerivatives)

## **Additional information**

This thesis has been digitised by EThOS, the British Library digitisation service, for purposes of preservation and dissemination. It was uploaded to KAR on 25 April 2022 in order to hold its content and record within University of Kent systems. It is available Open Access using a Creative Commons Attribution, Non-commercial, No Derivatives (https://creativecommons.org/licenses/by-nc-nd/4.0/) licence so that the thesis and its author, can benefit from opportunities for increased readership and citation. This was done in line with University of Kent policies (https://www.kent.ac.uk/is/strategy/docs/Kent%20Open%20Access%20policy.pdf). If you ...

## Versions of research works

### **Versions of Record**

If this version is the version of record, it is the same as the published version available on the publisher's web site. Cite as the published version.

### **Author Accepted Manuscripts**

If this document is identified as the Author Accepted Manuscript it is the version after peer review but before type setting, copy editing or publisher branding. Cite as Surname, Initial. (Year) 'Title of article'. To be published in *Title of Journal*, Volume and issue numbers [peer-reviewed accepted version]. Available at: DOI or URL (Accessed: date).

## **Enquiries**

If you have questions about this document contact <u>ResearchSupport@kent.ac.uk</u>. Please include the URL of the record in KAR. If you believe that your, or a third party's rights have been compromised through this document please see our <u>Take Down policy</u> (available from <u>https://www.kent.ac.uk/guides/kar-the-kent-academic-repository#policies</u>).

## VERSATILE ERROR-CONTROL CODING SYSTEMS

by

## VALDEMAR C. ROCHA, Jr.

A Dissertation submitted for the Degree of Doctor of Philosophy in the Faculty of Natural Sciences at the University of Kent at Canterbury

Electronics Laboratories

15268

May, 1976

## F75268

BLC Microfilm No: D19629 (7)

To my wife,

Ursula

#### Acknowledgements

I would like to give my most grateful thanks to the Brazilian research coordinating institution, CAPES, for the financial support which made this research possible; to Professor R.C. Jennison for providing research facilities; to the Staff of the Electronics Laboratories for friendly assistance; to my colleagues in both the Communications Laboratory and the Computers & Cybernetics Laboratory for useful advice, discussion of relevant matters and sharing experimental equipment; to Miss Denise Paine for her efforts in the typing of this thesis; to Dr. P.G. Farrell for his helpful supervision, guidance, encouragement and the constant interest demonstrated during the course of this research; to my family, friends and especially to my wife for encouragement, patience and understanding.

#### ABSTRACT

The research reported in this thesis is in the field of error-correcting codes, which has evolved as a very important branch of information theory. The main use of error-correcting codes is to increase the reliability of digital data transmitted through a noisy environment. There are, sometimes, alternative ways of increasing the reliability of data transmission, but coding methods are now competitive in cost and complexity in many cases because of recent advances in technology.

The first two chapters of this thesis introduce the subject of error-correcting codes, review some of the published literature in this field and discuss the advantages of various coding techniques. After presenting linear block codes attention is from then on concentrated on cyclic codes, which is the subject of Chapter 3.

The first part of Chapter 3 presents the mathematical background necessary for the study of cyclic codes and examines existing methods of encoding and their practical implementation. In the second part of Chapter 3 various ways of decoding cyclic codes are studied and from these considerations, a general decoder for cyclic codes is devised and is presented in Chapter 4. Also, a review of the principal classes of cyclic codes is presented.

Chapter 4 describes an experimental system constructed for measuring the performance of cyclic codes initially

ii

perturbed by random errors and then by bursts of errors. Simulated channels are used both for random and burst errors. A computer simulation of the whole system was made in order to verify the accuracy of the experimental results obtained.

Chapter 5 presents the various results obtained with the experimental system and by computer simulation, which allow a comparison of the efficiency of various cyclic codes to be made. Finally, Chapter 6 summarises and discusses the main results of the research and suggests interesting points for future investigation in the area.

The main objective of this research is to contribute towards the solution of a fairly wide range of problems arising in the design of efficient coding schemes for practical applications; i.e. a study of coding from an engineering point of view.

iii

## CONTENTS

|                                      |     | . ' | Page |

|--------------------------------------|-----|-----|------|

|                                      |     |     |      |

| Acknowledgements                     |     |     | i    |

| Abstract                             |     |     | ii   |

| Contents                             |     |     | iv   |

| Symbols and Abbreviations            |     |     | viii |

|                                      |     |     |      |

| CHAPTER 1 : Introduction             |     |     | 1    |

|                                      |     |     |      |

| CHAPTER 2 : Survey of Coding         |     |     | 7    |

| 2.1 Introduction                     |     |     | 7    |

| 2.2 Block and Convolutional Codes    |     |     | 7    |

| 2.3 Linear Block Codes               |     |     | 8    |

| 2.4 Generator Matrix                 |     |     | 9    |

| 2.5 Parity Check Matrix              |     |     | 11   |

| 2.6 Error Syndrome and Decoding      |     |     | 12   |

| 2.7 The Standard Array               |     |     | 16   |

| 2.8 Maximum Likelihood Decoding      |     |     | 18   |

| 2.9 Systematic Search Decoding       |     |     | 19   |

| 2.10 Single Parity Check (S.P.C.) Co | des |     | 20   |

| 2.11 Hamming Codes                   |     |     | 23   |

| 2.12 Product Codes                   |     |     | 27   |

| 2.13 Constant Weight Codes           |     |     | 28   |

iv

|      |        |                                             | Page |

|------|--------|---------------------------------------------|------|

| CH   | APTER  | <u>3</u> : Cyclic Codes                     | 29   |

|      | 3.1    | Introduction                                | 29   |

|      | 3.2    | Basic Definitions                           | 29   |

|      | 3.3    | Matrix Representation of Cyclic Codes       | 32   |

|      | 3.4    | Encoding with an (n-k)-Stage Shift-Register | 33   |

|      | 3.5    | Encoding with a k-Stage Shift-Register      | 35   |

|      | 3.6    | Syndrome Calculation                        | 38   |

|      | 3.7    | Shortened Cyclic Codes                      | 41   |

|      | 3.8    | Pseudo-Cyclic Codes                         | 42   |

| <br> | 3.9    | Decoding Cyclic Random Error Correcting     | 43   |

|      |        | Codes                                       |      |

|      | 3.9.1  | Meggitt Decoder                             | 43   |

| ·    | 3.9.2  | Error Trapping Decoding                     | 48   |

|      | 3.9.3  | Permutation Decoding                        | 52   |

|      | 3.9.4  | Majority Logic Decoding                     | 53   |

|      | 3.10   | Bose-Chaudhuri-Hocquenghem (B.C.H.) Codes   | 63   |

|      | 3.10.1 | Basic Properties of B.C.H. Codes            | 64   |

|      | 3.10.2 | Decoding of the B.C.H. Codes                | 66   |

|      | 3.11   | Burst Error Correction                      | 70   |

|      | 3.12   | Decoding of Burst-Correcting Cyclic Codes   | 72   |

|      | 3.12.1 | Burst Trapping Decoder                      | 72   |

|      | 3.12.2 | Gallager Optimum Burst Decoder              | 73   |

|      | 3.12.3 | High-Speed Burst Decoder                    | 74   |

|      | 3.13   | Important Classes of Cyclic Codes           | 75   |

|      | 3.13.1 | Hamming Codes                               | 75   |

|      | 3.12.2 | Maximum Length Sequence Codes               | 76   |

|      | 3.13.3 | Reed-Solomon Codes                          | 76   |

v

|         |                                      | Page |

|---------|--------------------------------------|------|

| 3.13.4  | Codes Based on Finite Geometries     | 77   |

| 3.13.5  | Quadratic Residue Codes              | 78   |

| 3.13.6  | Fire Codes                           | 79   |

| CHAPTER | 4 : Experimental System and Computer |      |

|         | Simulation                           | 81   |

| 4.1     | Introduction                         | 81   |

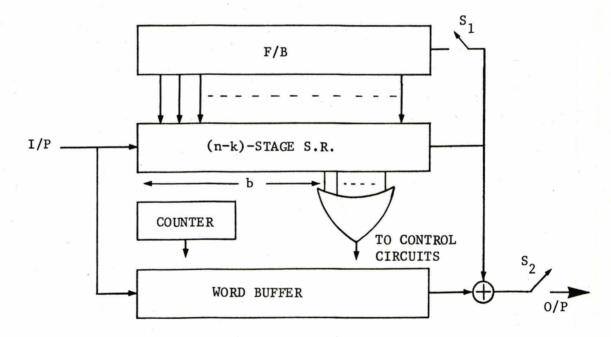

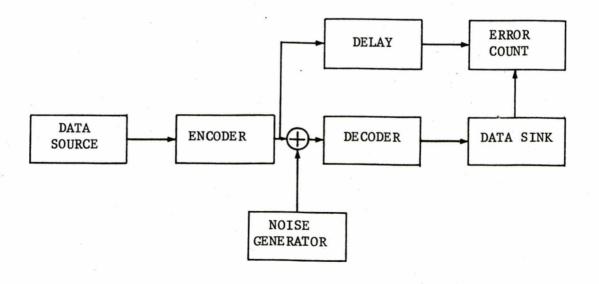

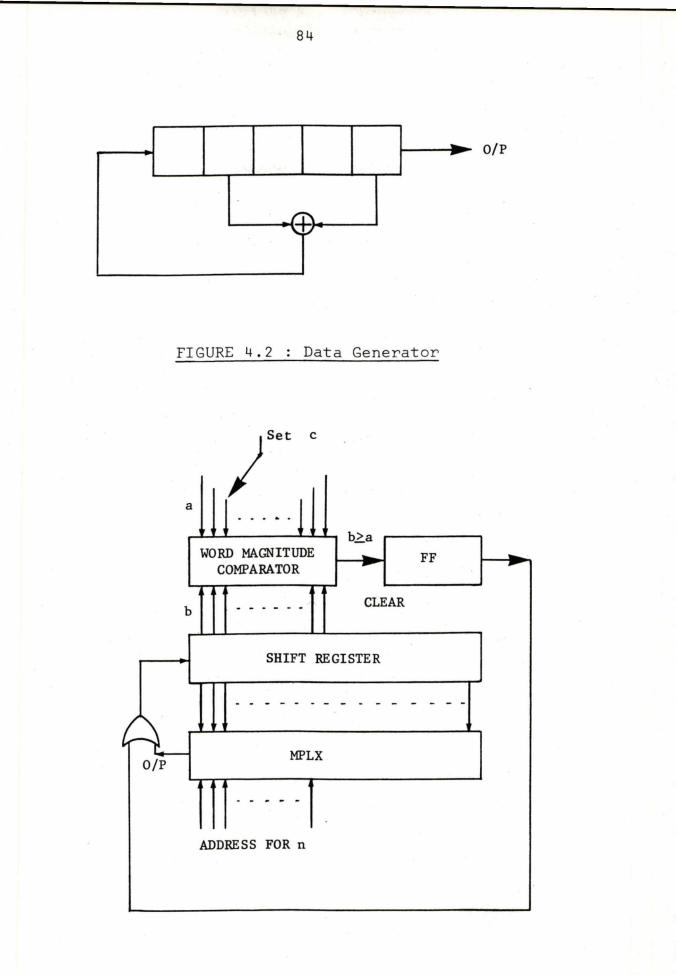

| 4.2     | Data Source                          | 82   |

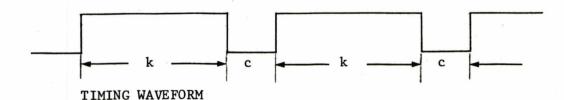

| 4.3     | Clock and Timing Waveforms           | 83   |

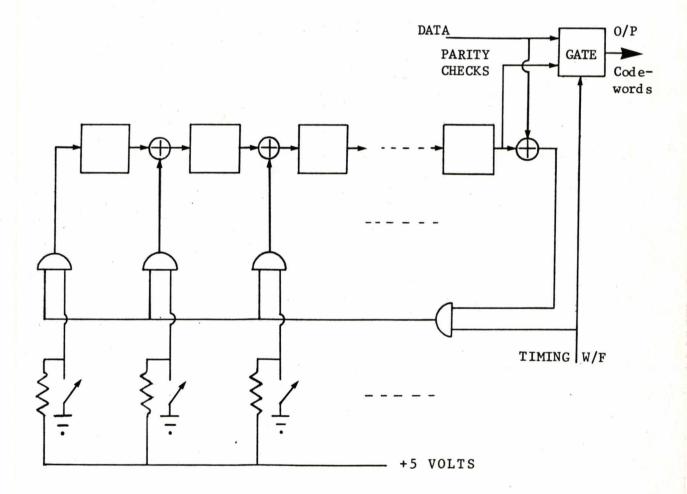

| 4.4     | Encoder                              | 85   |

| 4.5     | Error Generator                      | 86   |

| 4.5.1   | Random Errors                        | 86   |

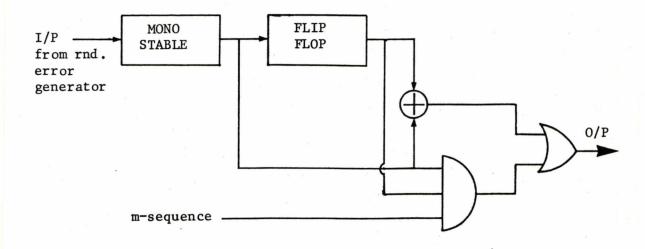

| 4.5.2   | Generation of Bursts                 | 91   |

| 4.6     | Random Error Correction              | 92   |

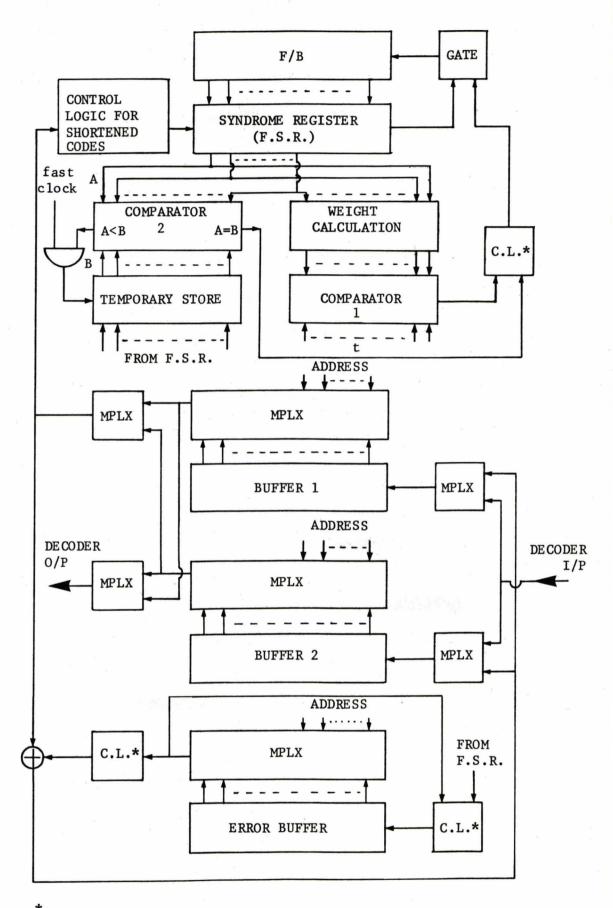

| 4.6.1   | Decoder                              | 93   |

| 4.6.2   | Error Trapping                       | 94   |

| 4.6.3   | Systematic Search                    | 96   |

| 4.6.4   | Shortened Cyclic Codes               | 97   |

| 4.7     | Burst Error Correction               | 98   |

| 4.7.1   | Encoder                              | 98   |

| 4.7.2   | Decoder                              | 98   |

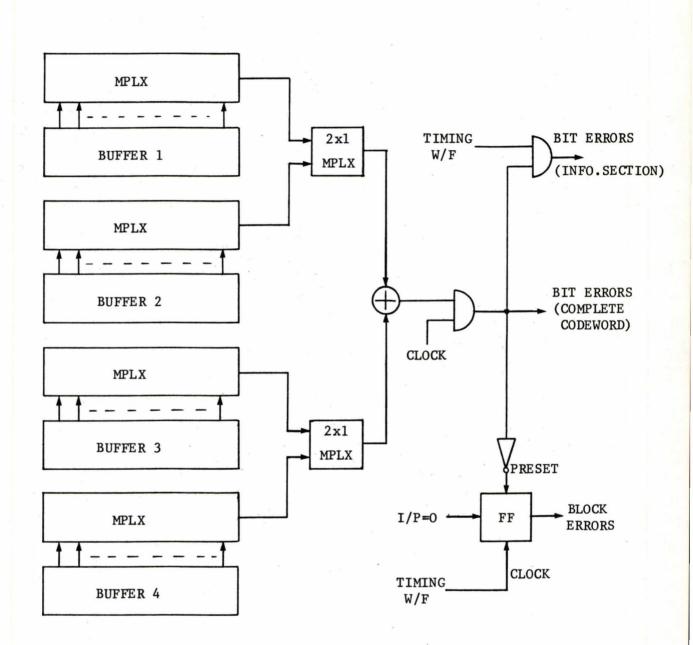

| 4.8     | Counting Errors                      | 100  |

| 4.9     | Computer Simulation                  | 102  |

|                                                 | Page |

|-------------------------------------------------|------|

| CHAPTER 5 : Experimental and Computer Simulated |      |

| Results                                         | 104  |

| 5.1 Introduction                                | 104  |

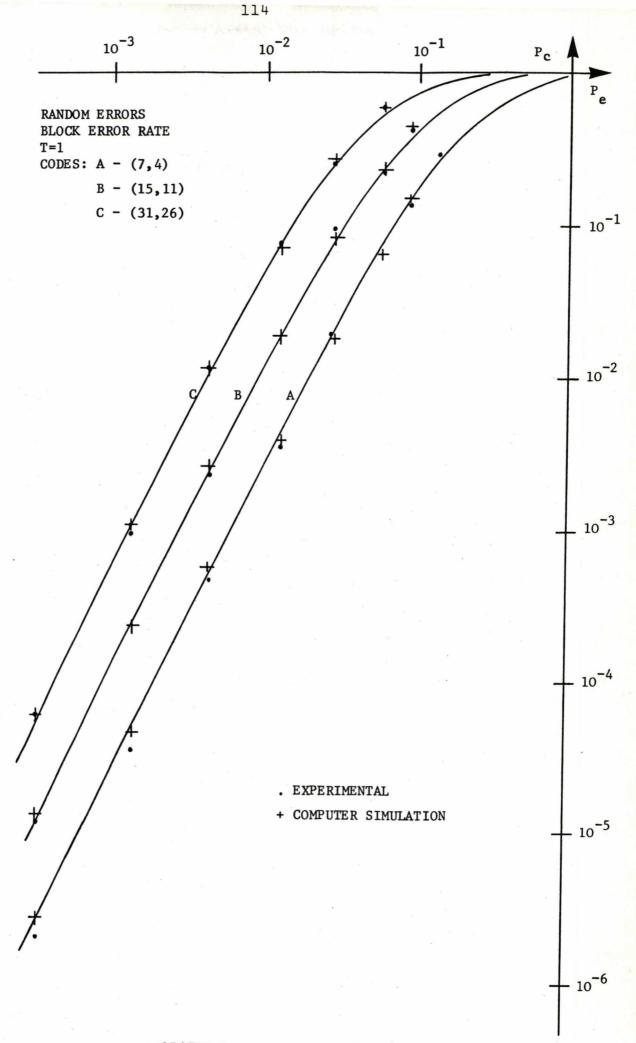

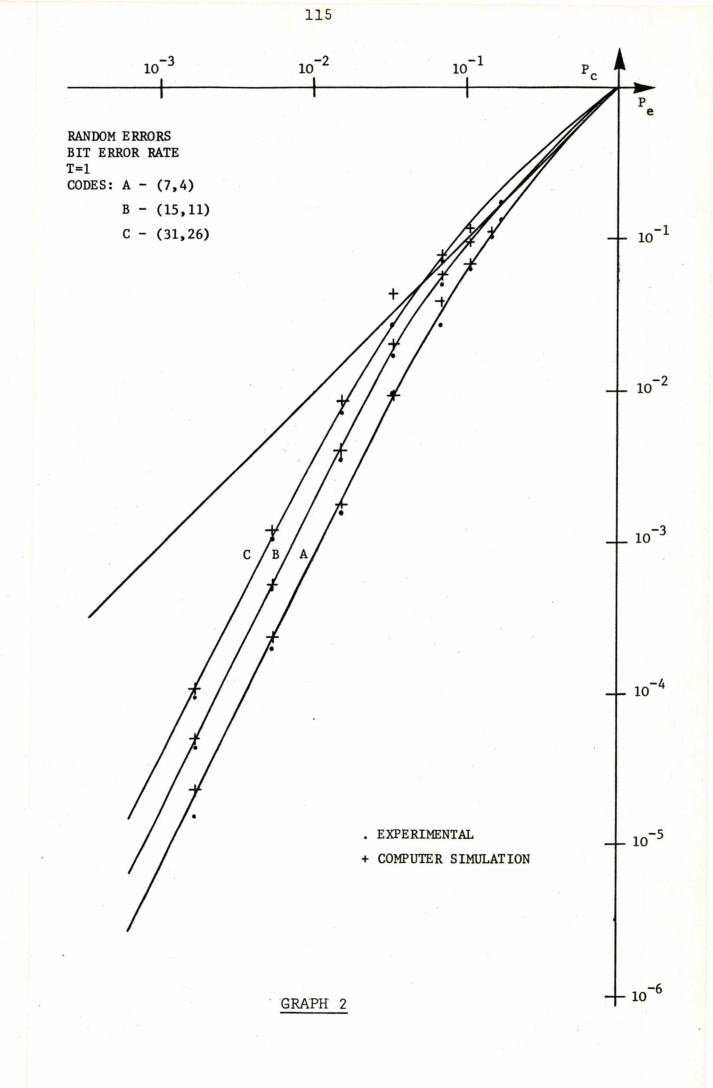

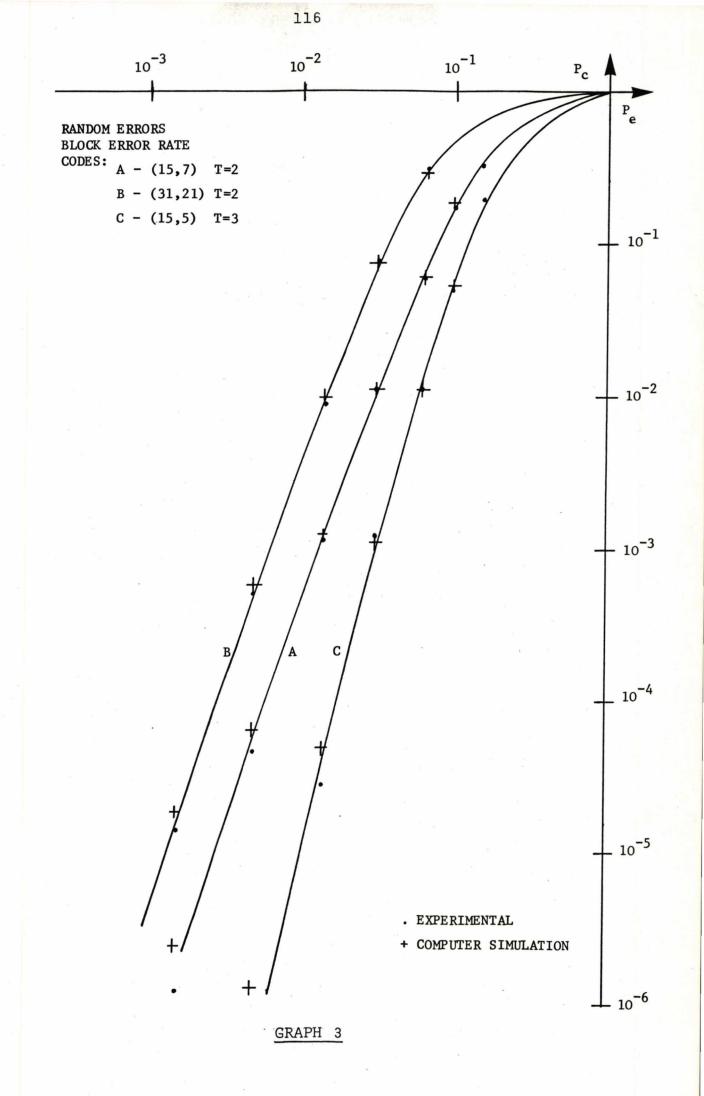

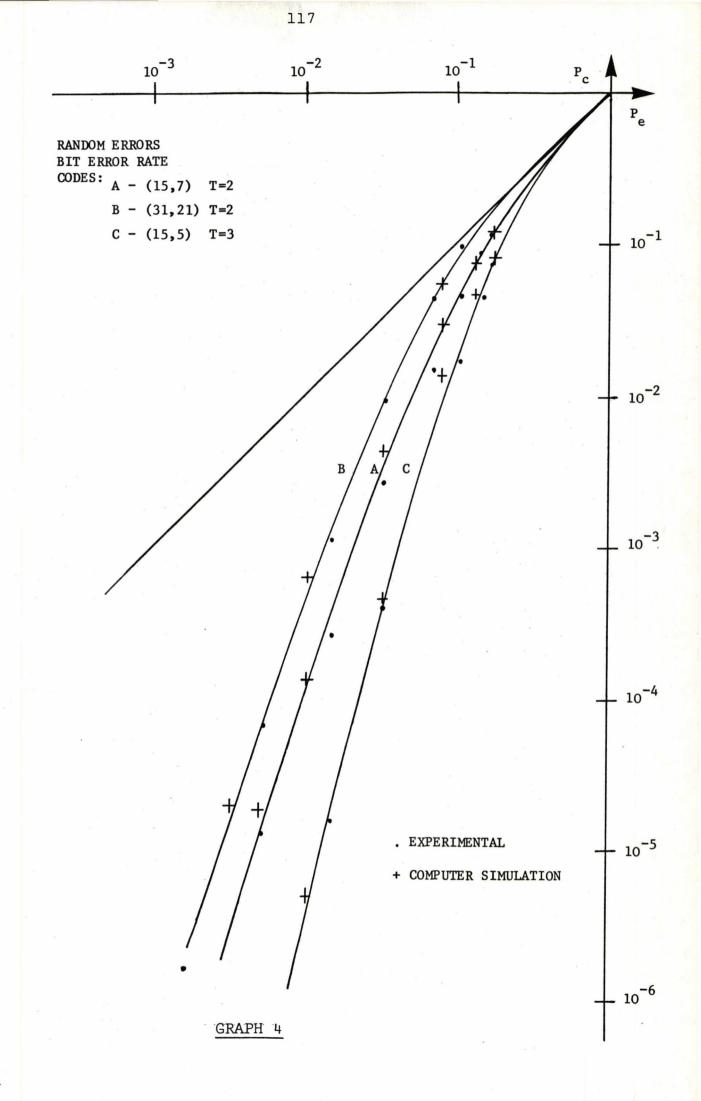

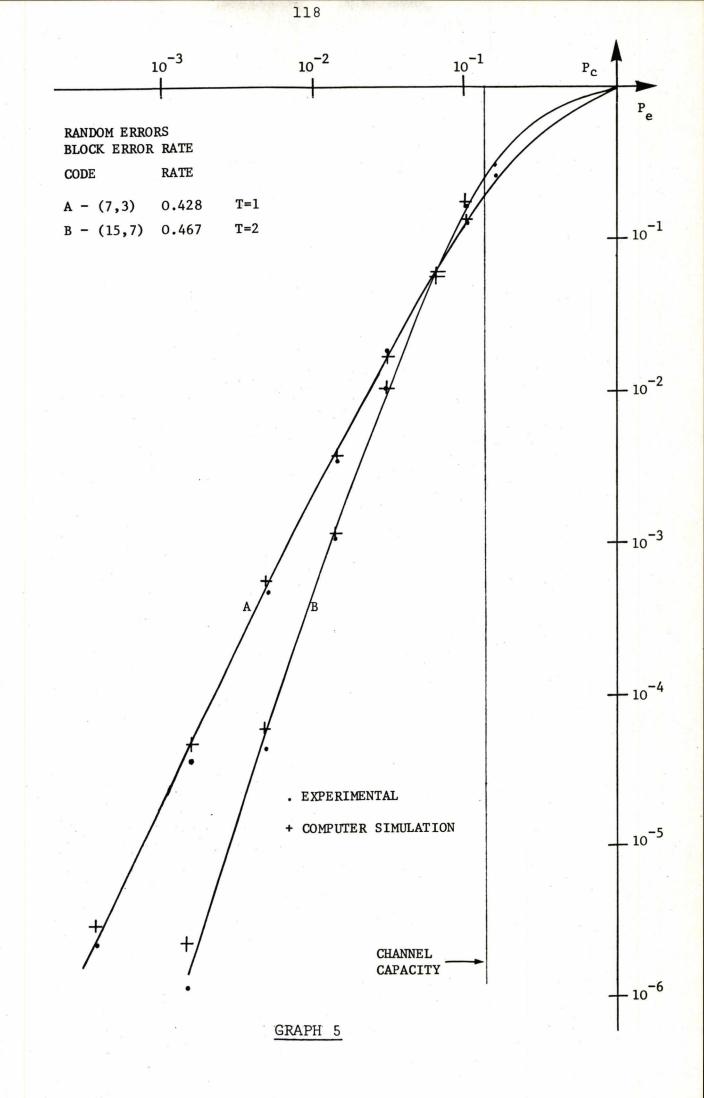

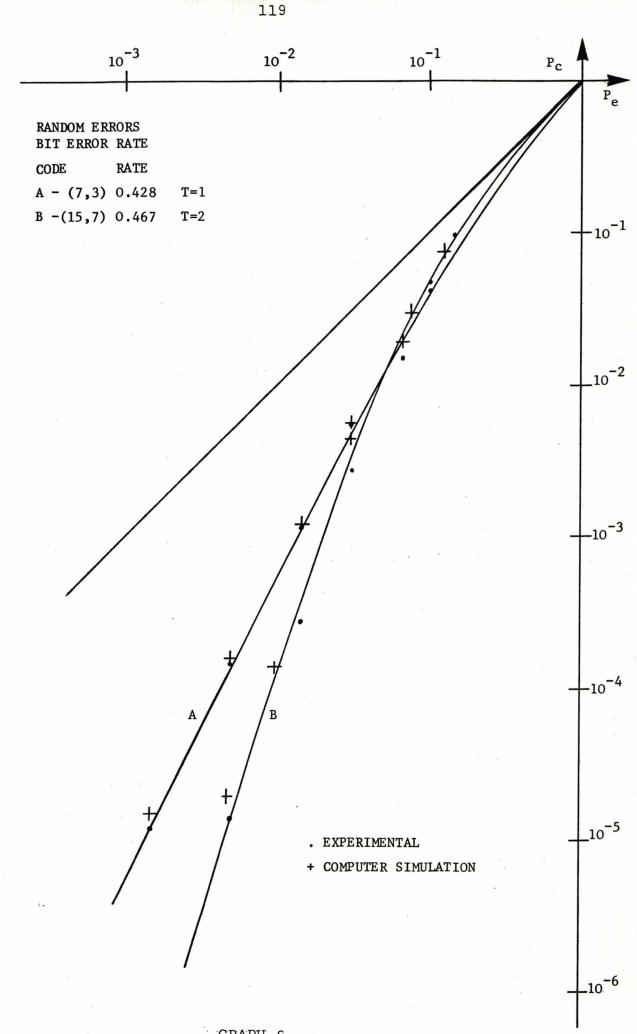

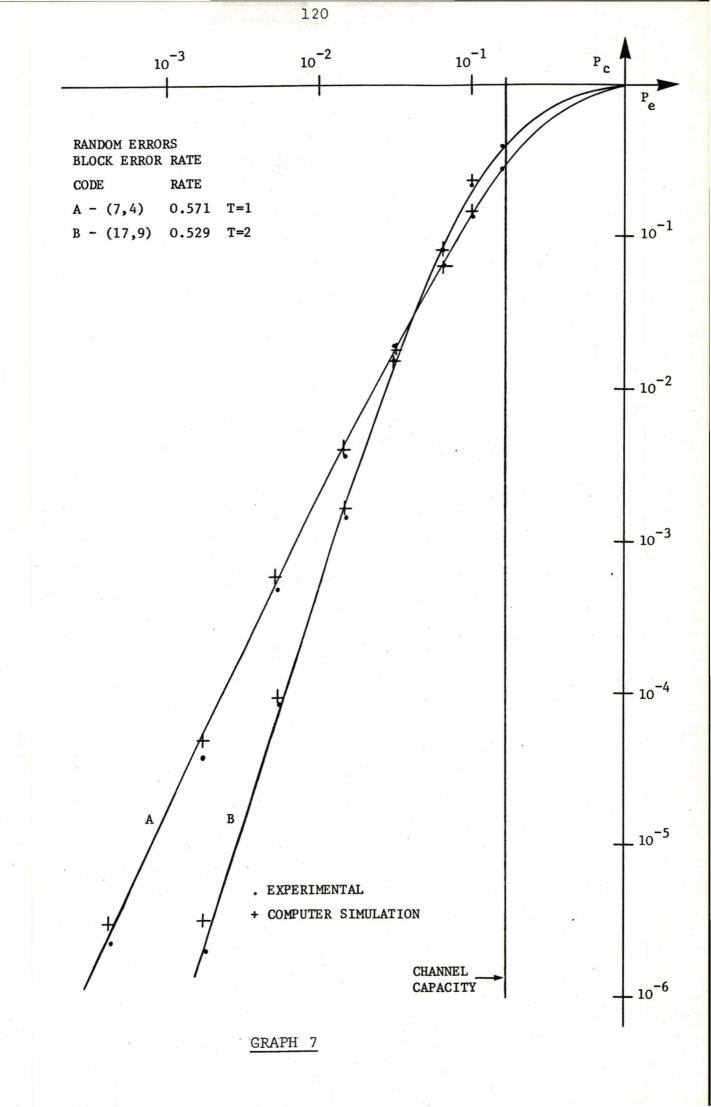

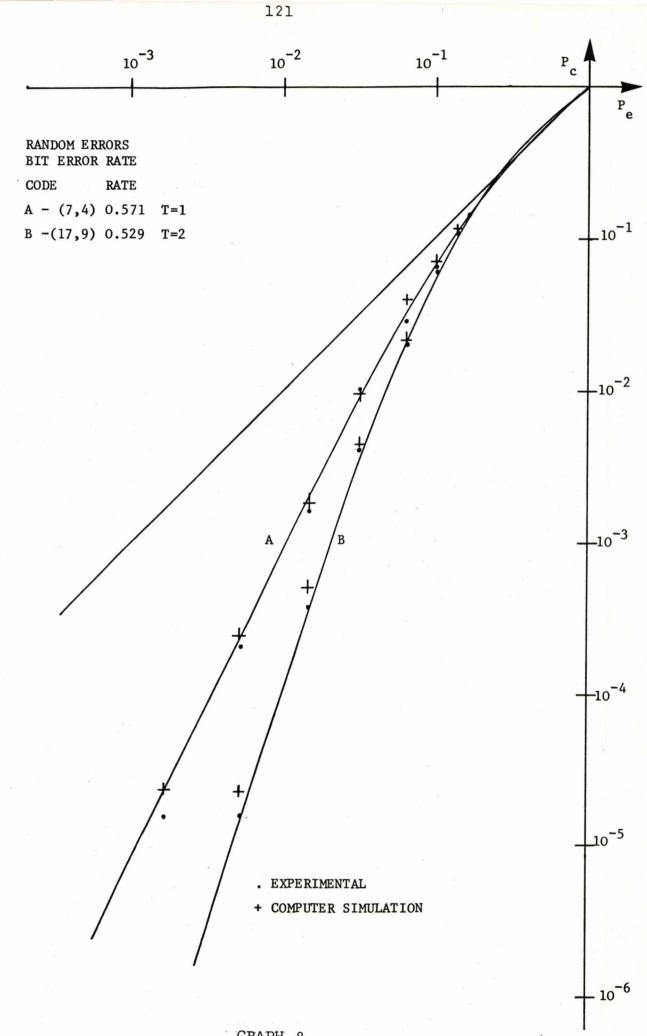

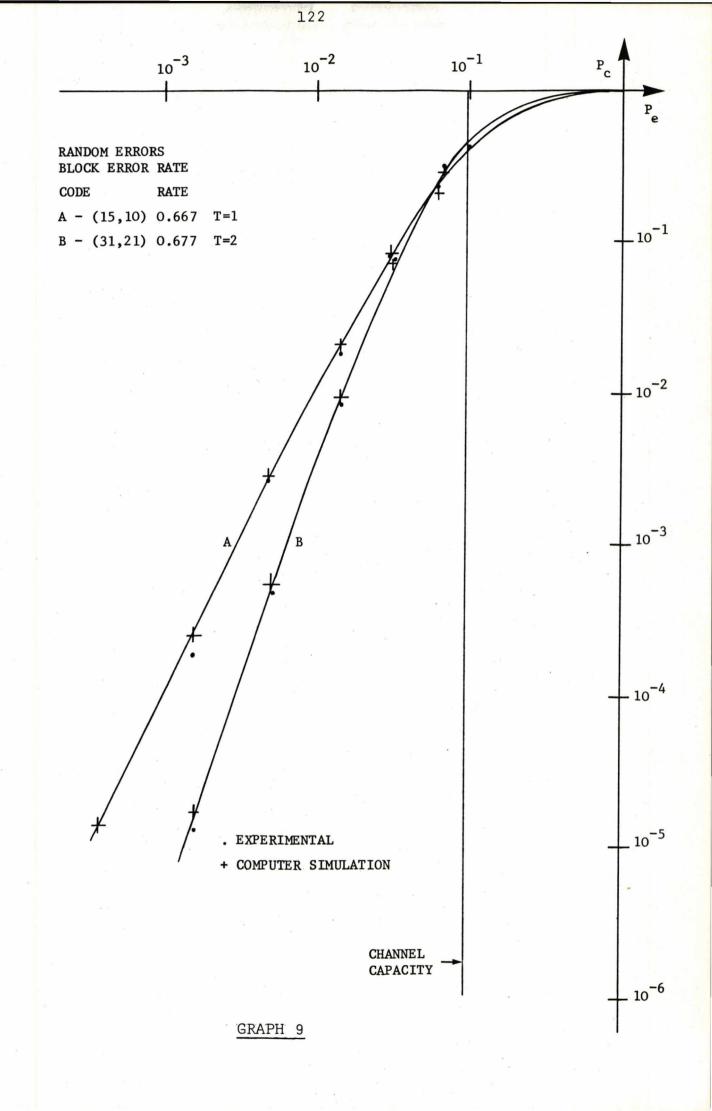

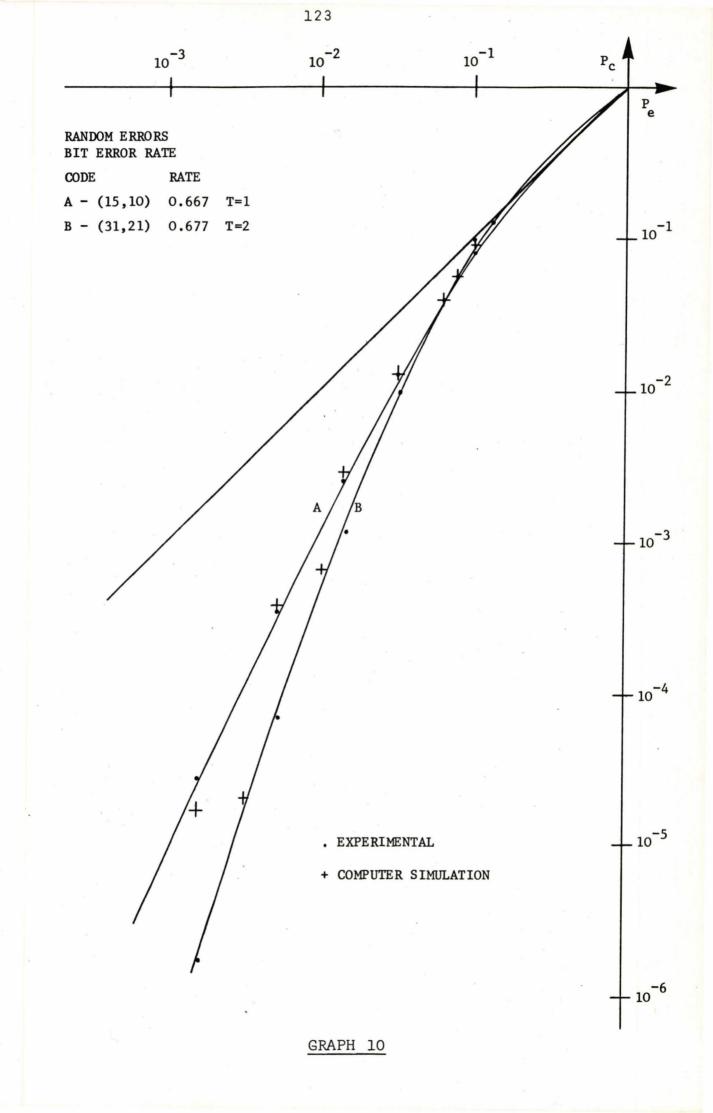

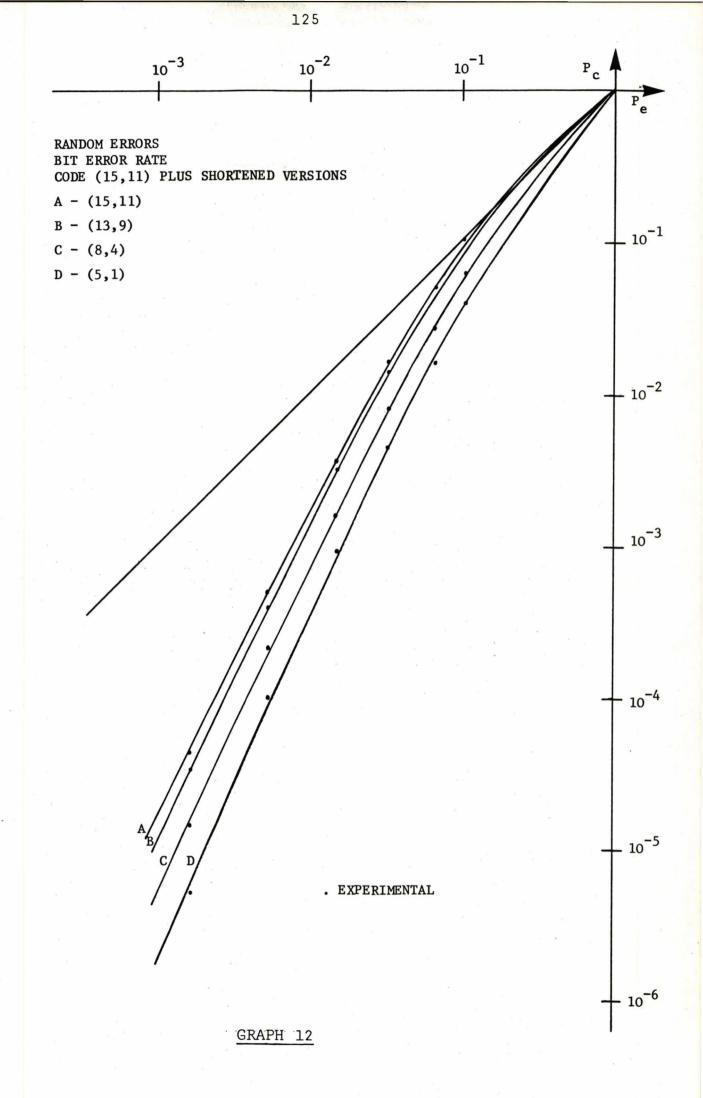

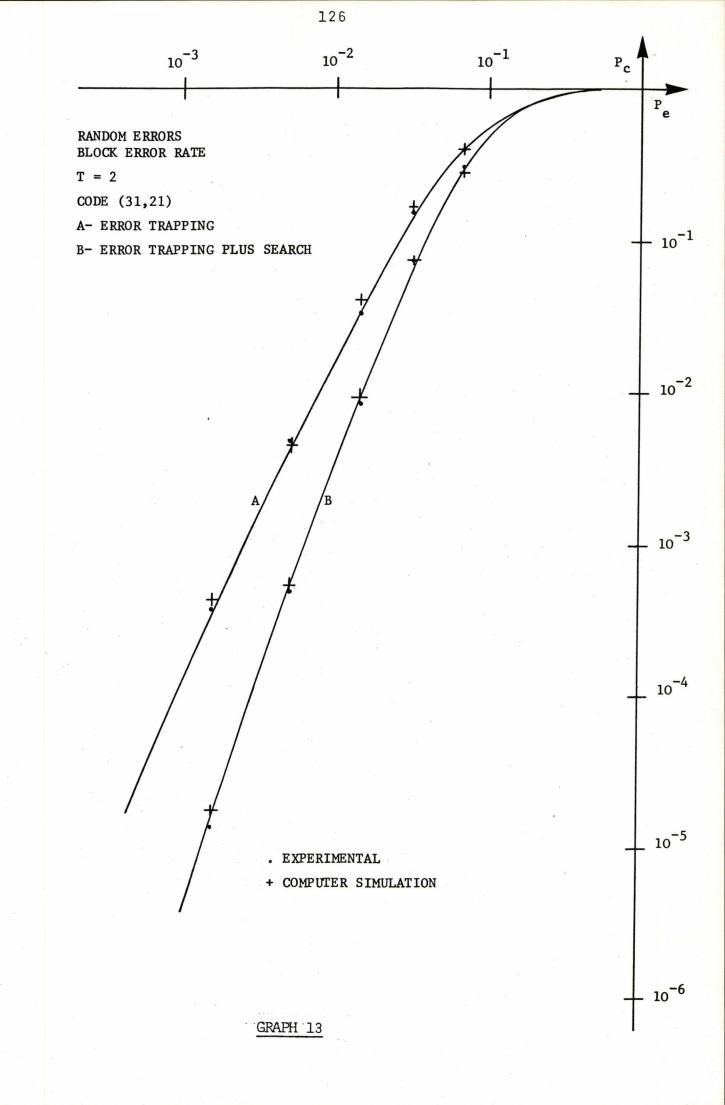

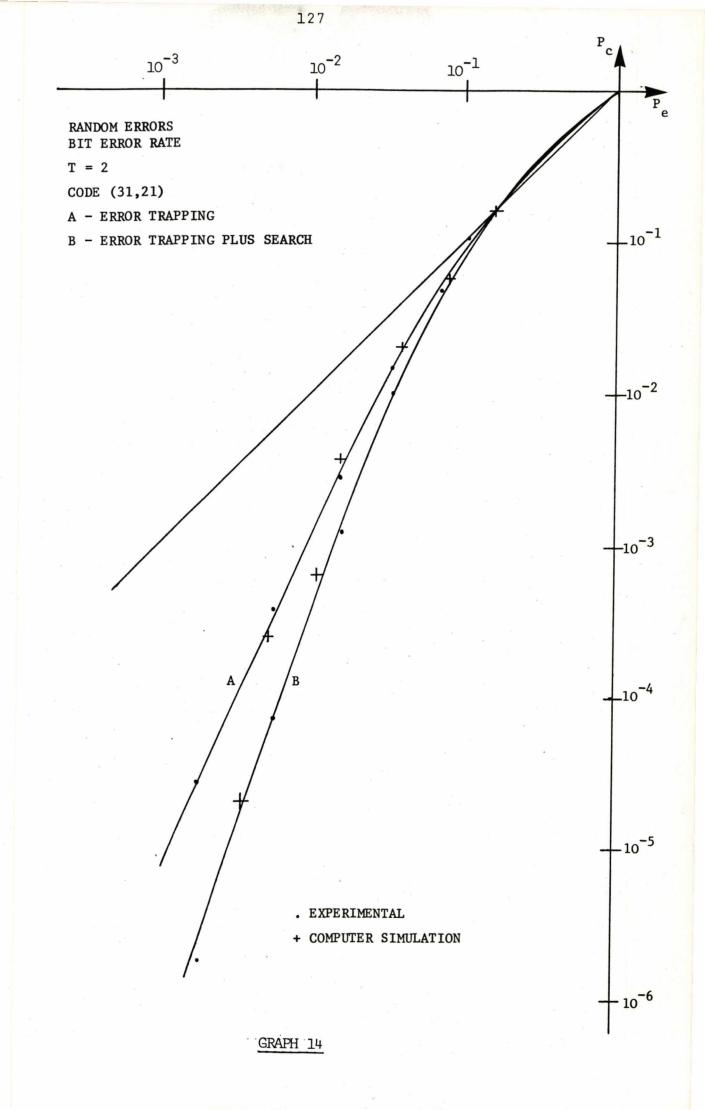

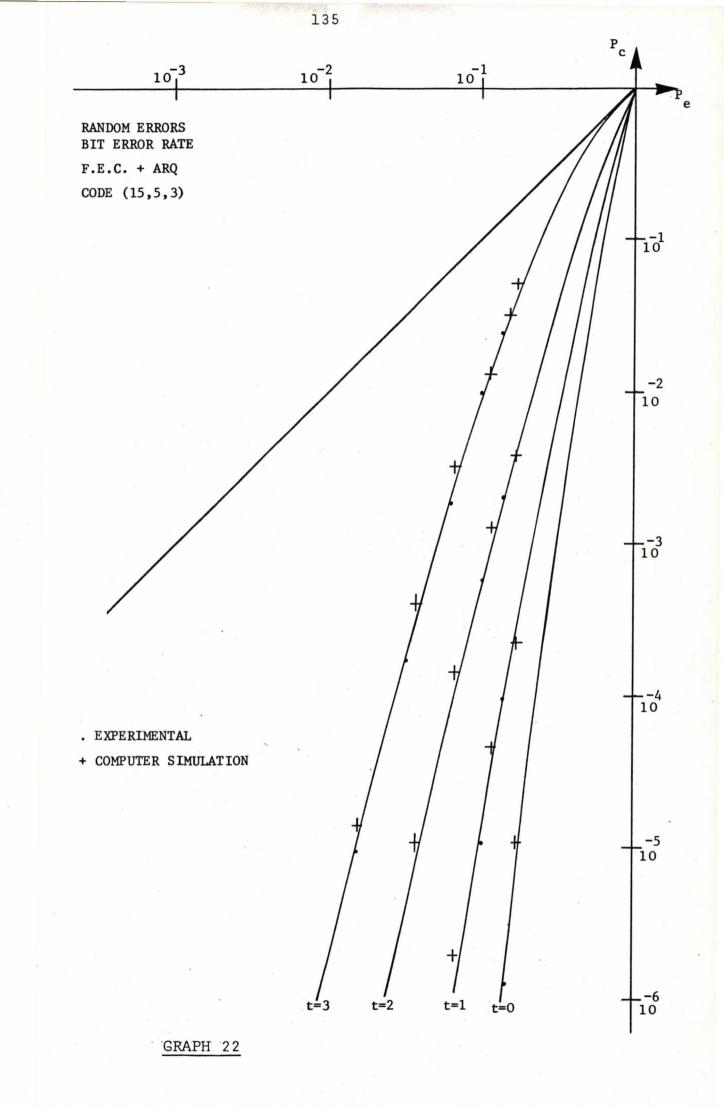

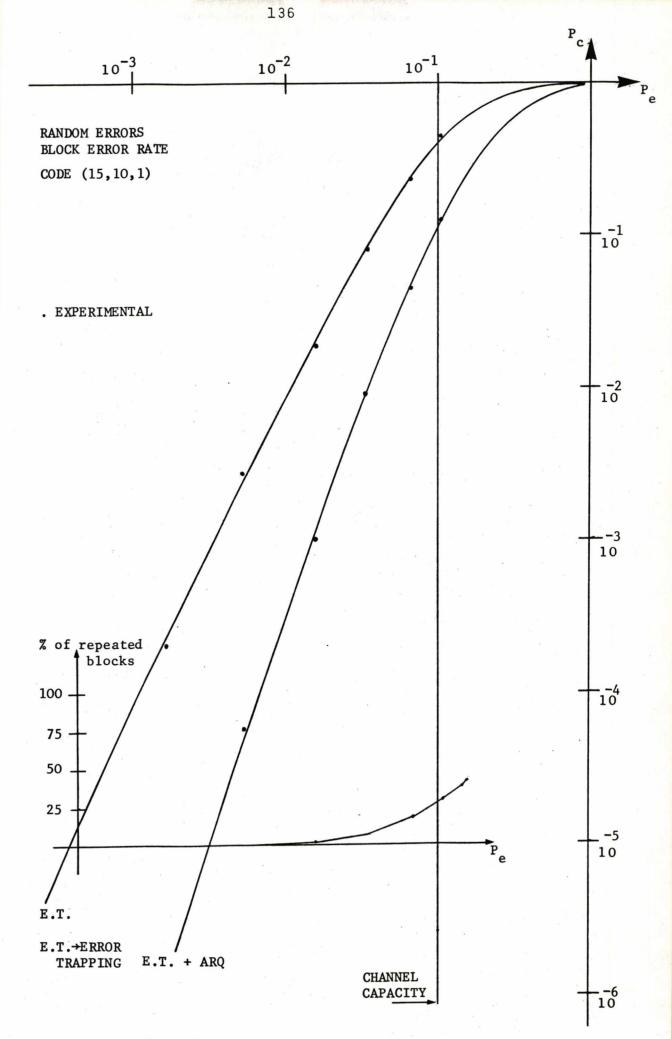

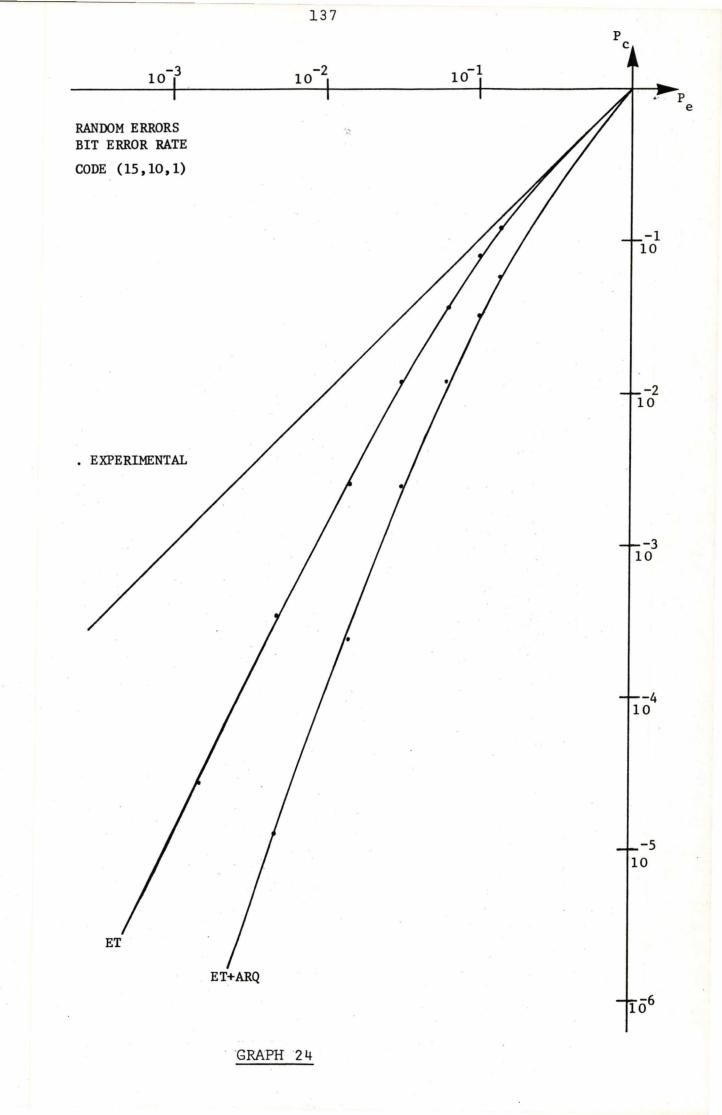

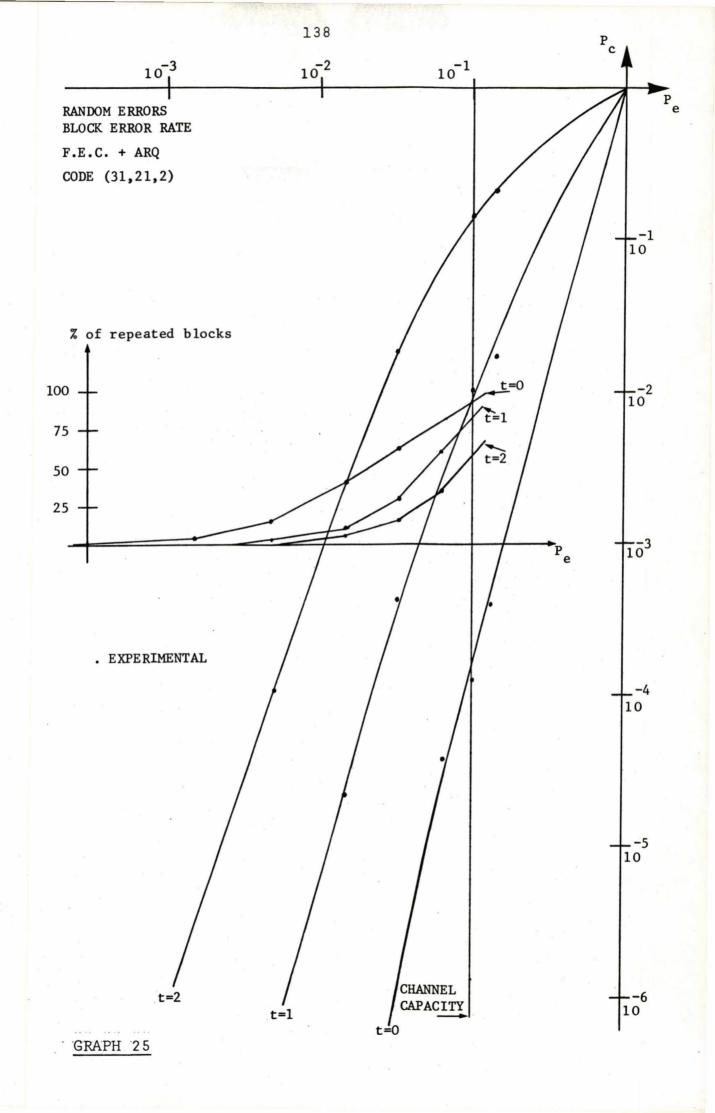

| 5.2 Cyclic Random Error Correcting Codes        | 104  |

| 5.2.1 Shortened Cyclic Codes                    | 106  |

| 5.2.2 Error Trapping Plus Systematic Search     | 107  |

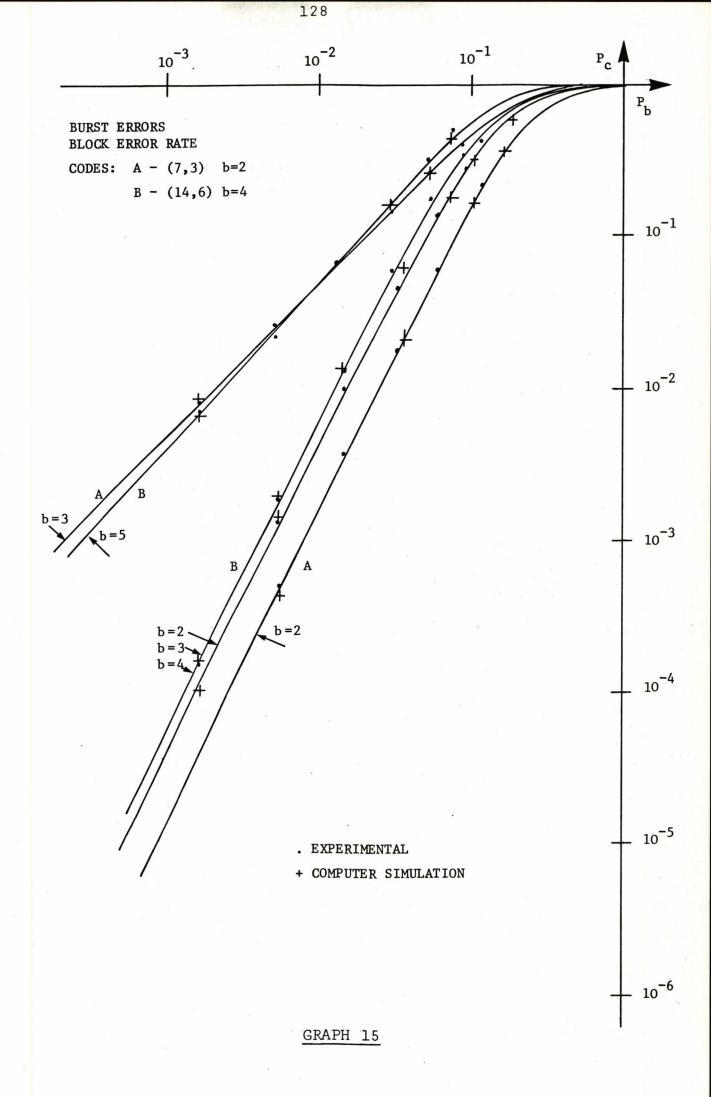

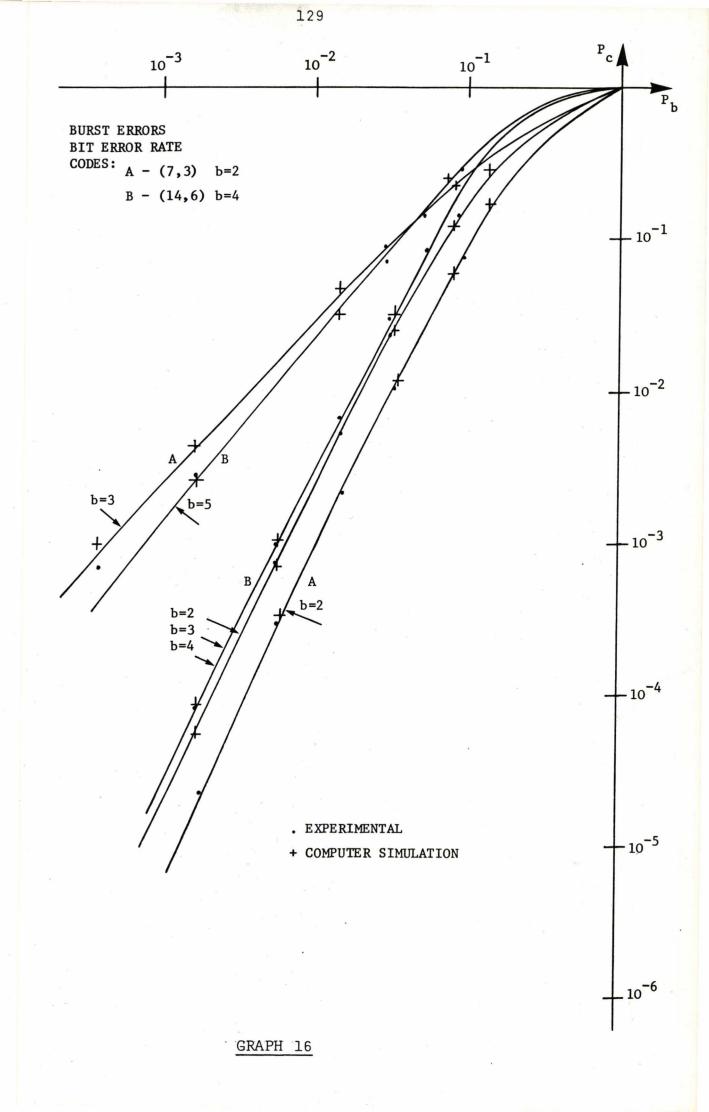

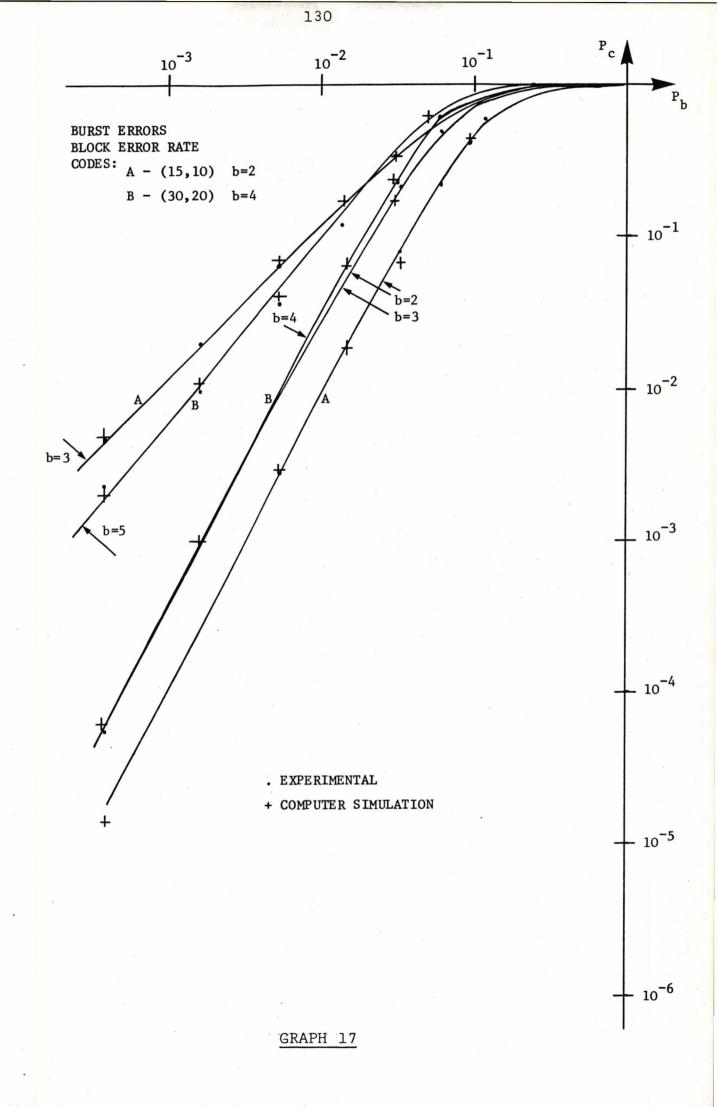

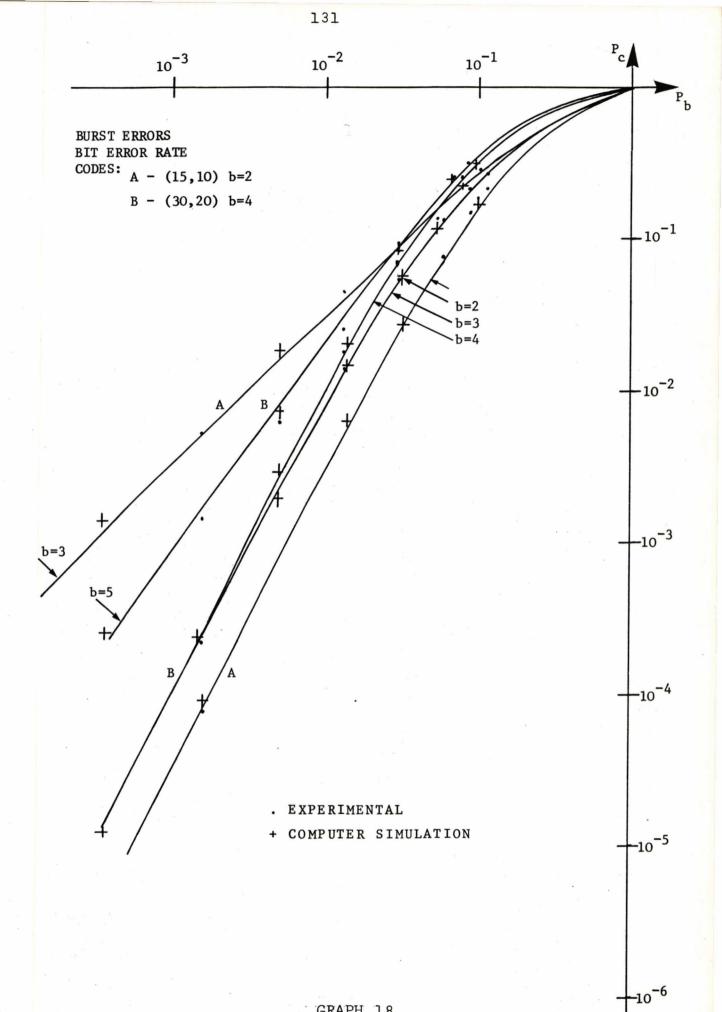

| 5.3 Cyclic Burst-Error-Correcting Codes         | 108  |

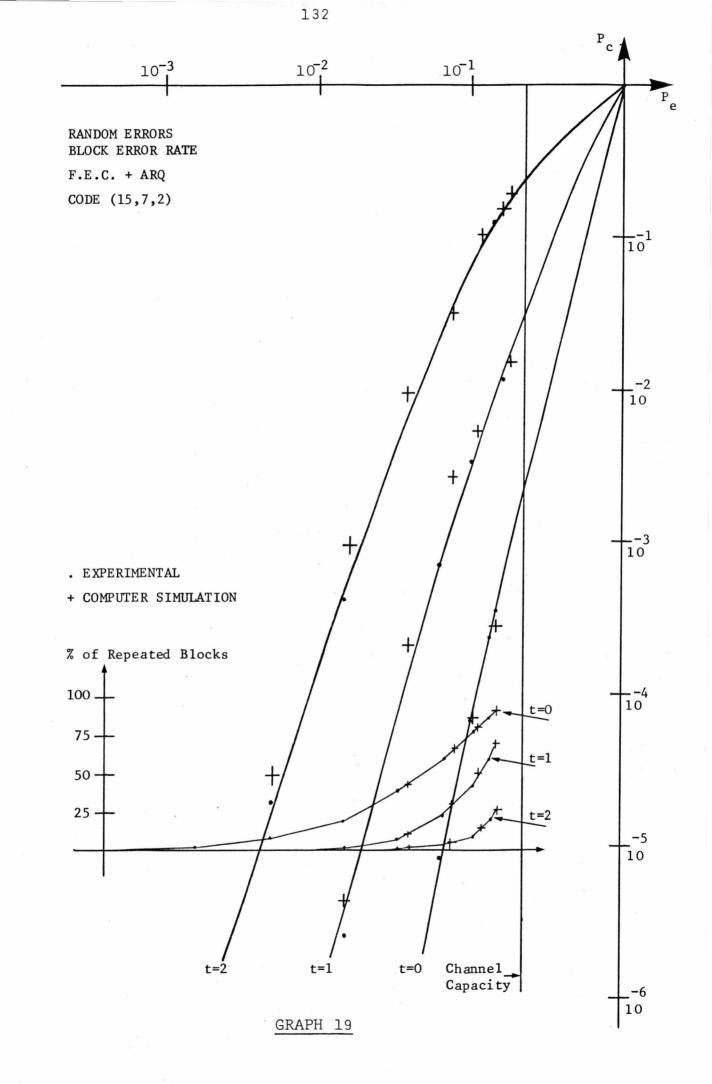

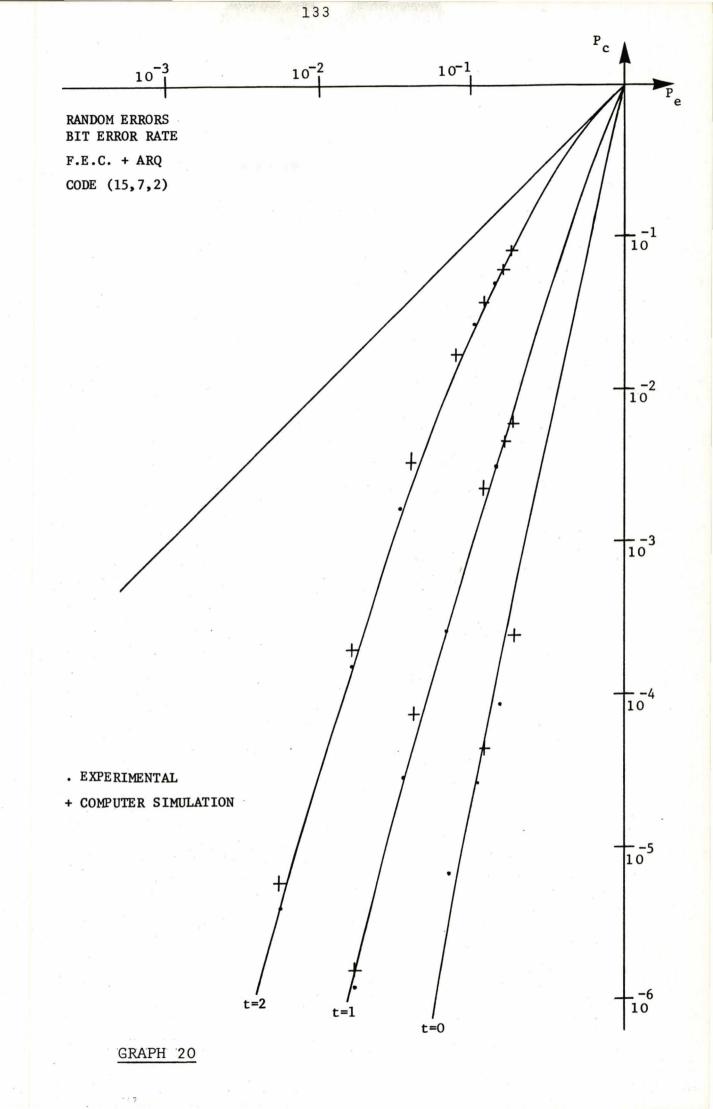

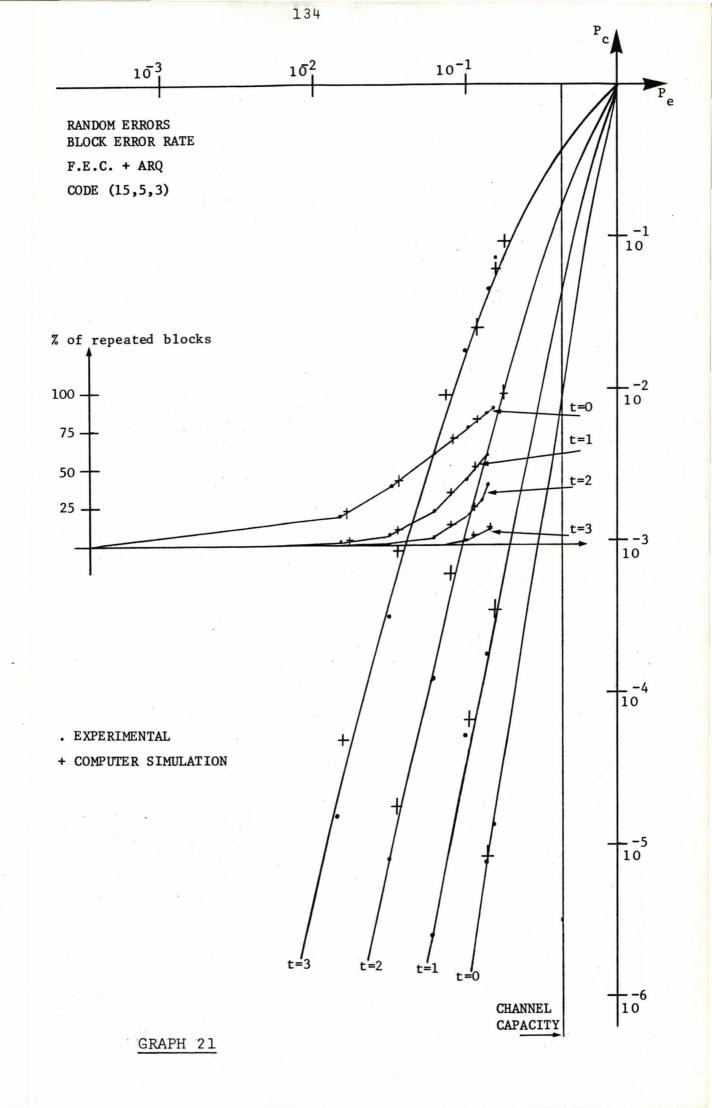

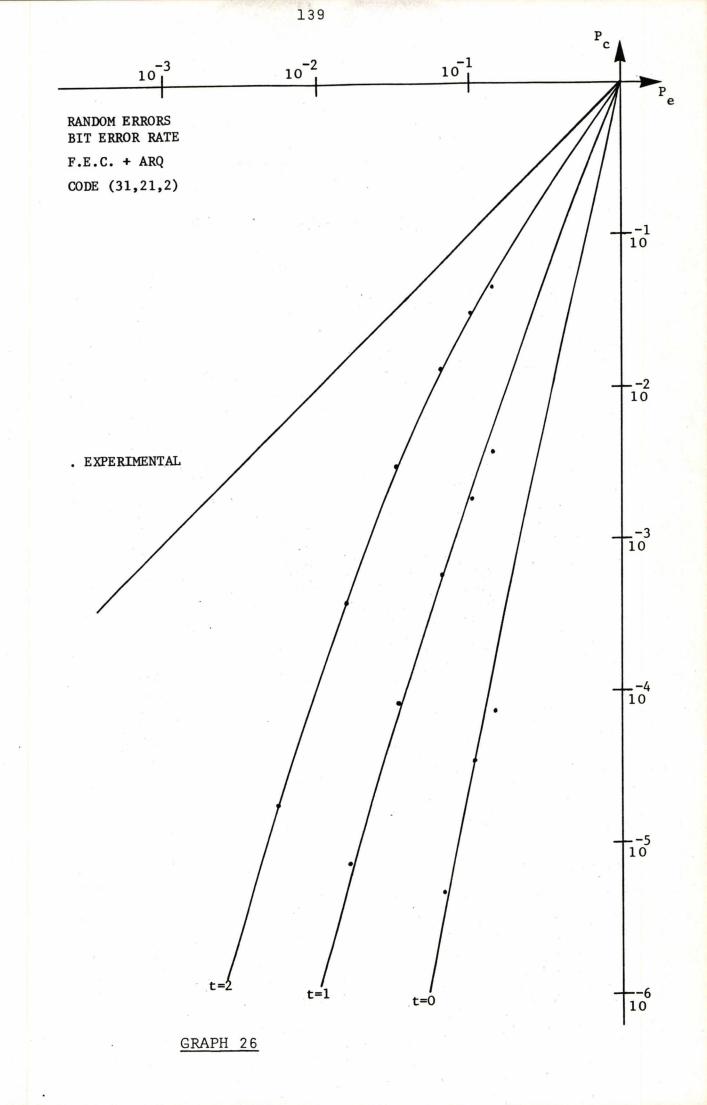

| 5.4 Forward Error Correction with A.R.Q.        | 111  |

| 5.5 Possible Sources of Inaccuracy in the       |      |

| Results                                         | 112  |

|                                                 |      |

| CHAPTER 6 : Conclusion                          | 140  |

|                                                 |      |

| APPENDIX I : Modern Algebra and Vector Spaces   | 146  |

| APPENDIX II : Computer Programmes               | 151  |

| APPENDIX III : List of Integrated Circuits      | 158  |

|                                                 |      |

| BIBLIOGRAPHY                                    | 159  |

| INDEX                                           | 176  |

vii

## Symbols and Abbreviations

| α                             | Primitive element of a Galois Field                      |

|-------------------------------|----------------------------------------------------------|

| A.R.Q.                        | Automatic repeat request                                 |

| b                             | Maximum burst length that a code can effectively correct |

| B.C.H.                        | Bose-Chaudhuri-Hocquenghem                               |

| B.S.C.                        | Binary Symmetric Channel                                 |

| с                             | Number of parity check digits in a block code            |

| C                             | Channel capacity                                         |

| C(x)                          | Remainder polynomial                                     |

| CLC                           | Combinational logic circuit                              |

| $C_n^t = \frac{n!}{(n-t)!t!}$ |                                                          |

| D                             | Unit delay<br>Number of errors a code can detect         |

| d                             | Hamming distance                                         |

| E                             | Noise error pattern                                      |

| E(x)                          | Polynomial representation of an error pattern            |

| EB                            | Error buffer                                             |

| EC                            | Error correcting code                                    |

| ED                            | Error detecting code                                     |

| ET                            | Error trapping                                           |

| F/B                           | Feedback                                                 |

| FF                            | Flip-flop                                                |

| FEC                           | Forward error correction                                 |

| FSR                           | Feedback shift register                                  |

| G                             | Generator matrix of a linear code                        |

| G(x)           | Generator polynomial of a cyclic code                  |

|----------------|--------------------------------------------------------|

| GF(q)          | Galois field with q elements                           |

| [H]            | Parity check matrix                                    |

| H(x)           | Parity check polynomial of a cyclic code               |

| I/P            | Input                                                  |

| I(x)           | Polynomial representation of k informa-<br>tion digits |

| J              | Number of orthogonal parity check equations            |

| k              | Number of information digits in a block code           |

| LCM            | Least common multiple                                  |

| MPLX           | Multiplexer                                            |

| n              | Block length of a code                                 |

| (n <b>,</b> k) | Block code with parameters n and k                     |

| (n,k,d)        | Block code with parameters n, k and d                  |

| 0/P            | Output                                                 |

| p .            | Exponent to which a polynomial belongs                 |

| P(x)           | Primitive polynomial<br>Quotient polynomial            |

| Pc             | Probability of erroneous decoding                      |

| P <sub>b</sub> | Probability of a burst occurring                       |

| Pe             | Probability of a random error occurring                |

| PN             | Pseudo-noise                                           |

| PROM           | Programmable Read Only memory                          |

| q              | Number of levels that a digit can assume               |

| Q(x)           | Quotient polynomial                                    |

| [R]            | Received codeword                                      |

| R              | Code information rate or efficiency                    |

| R(X)           | Polynomial representation of a received n-tuple        |

| REM            | Remainder (from a division)                            |

ix

| [s]    | Syndrome vector                                           |

|--------|-----------------------------------------------------------|

| S(x)   | Polynomial representation of a syndrome vector            |

| S.C.R. | Syndrome calculating register                             |

| S/N    | Signal-to-noise power ratio                               |

| S.P.C. | Single parity check                                       |

| S.R.   | Shift register                                            |

| t      | Number of random errors a code can correct (per codeword) |

|        | Transmitted codeword                                      |

| V(x)   | Polynomial representation of a trans-<br>mitted codeword  |

| X      | Determinant X                                             |

| [X]    | Largest integer $\leq X$                                  |

| X      | Matrix X                                                  |

|        | Transpose of $[X]$                                        |

| W      | Channel frequency bandwidth                               |

| W(v)   | Weight of an n-tuple $v$                                  |

| W/F    | Waveform                                                  |

|        | Two input exclusive-OR gate                               |

| =D     | Two input OR-gate                                         |

| =D     | Two input AND-gate                                        |

|        | Logical inverter                                          |

\_

x

#### CHAPTER 1

#### Introduction

People in their desire to communicate with others have, since the very early days of history, been challenged by the problem of how to achieve reliable communication, i.e. reliable transmission of information. Though the formulation of this problem has varied a lot over the centuries, it remains very much alive and is of major concern among the communication engineers of today.

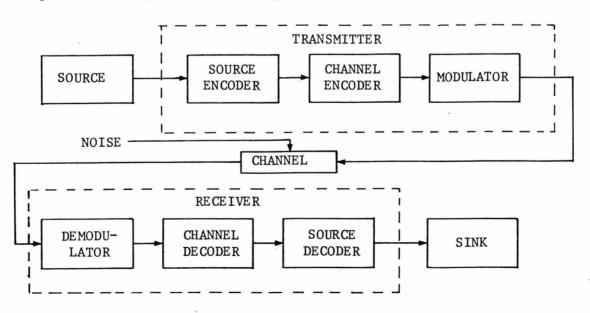

Practical communication systems keep changing their external aspect as technology changes, e.g. the old systems evolved from electromechanical switching relays to vacuum tubes, later to transistors, etc. However, a closer look reveals that in general terms these systems can all be represented by a block diagram like that of Figure 1.1.

FIGURE 1.1 : General Communication System

l

<u>SOURCE</u>: Originating point for the information to be transmitted. It can be, for example, the output from a remote sensor in a telemetering system. <u>TRANSMITTER</u>: Converts the source output into waveforms suitable for transmission over the channel. The function of the transmitter can be subdivided as follows:

#### 1. SOURCE ENCODER

This can be in many cases simply an analogue to digital converter or in other situations a more **sophisti**cated piece of equipment to remove unnecessary detail from the information, as in data compression schemes.

2. <u>CHANNEL ENCODER</u> Controlled redundancy is added to the information by the channel encoder to counteract as far as possible the effects of noise.

#### 3. MODULATOR

In many cases the output from the channel encoder is not matched to the channel. It is the function of the modulator to translate the channel encoder output into a waveform suitable for transmission over the channel.

<u>CHANNEL</u>: Physical path over which the information has to pass before reaching the receiver. A channel can take a variety of forms. Pair of wires, or microwave links, are examples of practical channels. As the information is carried through a channel, it is subjected to unpredictable and unwanted disturbances called noise. As a result

of noise part of the information can be badly corrupted.

<u>RECEIVER</u>: Estimates which waveform has been transmitted from the received version, possibly corrupted by noise, of the original waveform. This is normally the most complex part of a communication system and can be subdivided as follows:

#### 1. DEMODULATOR

On receiving a waveform from the channel the demodulator tries to estimate which waveform was sent by the transmitter and outputs the corresponding digital version. Due to noise, this version will not always be a correct one and so estimates containing errors will be passed on to the channel decoder.

#### 2. CHANNEL DECODER

By applying the coding rules to the digits provided by the demodulator, the channel decoder tries to correct possible errors and then produce its estimation of the source encoder output digits.

#### 3. SOURCE DECODER

Processes, to replace the redundancy removed at the transmitter, the channel decoder output before passing it to the sink. If a correct estimate of the transmitted message has been made by the channel decoder, then the source decoder will supply a replica of the original information to the sink.

<u>SINK</u> Final recipient of the information transmitted. The sink can be a human being at the end of a telephone line, or a computer, for example.

No matter how well designed, any communication system will always suffer from the effects of noise, i.e. the messages coming from its output may contain errors. It can take a long time before an error appears, but eventually it will happen. However, the practical problem is not the provision of error-free communication, but the design of systems which provide an acceptably low error rate for the user. For example, an error rate of  $10^{-4}$  for the letters in a book is perfectly acceptable, while the same error rate within a computer would be disastrous.

The ultimate potential of error-correcting codes was established in 1948 with Shannon's "Coding Theorem" for a noisy channel (Shannon, 1948). The coding theorem for a noisy channel states the following:

- every channel has a definite maximum capacity C, and for any rate R less than C, there exist codes of rate R which, with maximum likelihood decoding, have an arbitrarily small probability of erroneous decoding.

This means more specifically that for any given R<C and length n, there exists a code such that  $P_c \leq e^{-nE(R)}^*$  where E(R) > 0, for R<C, and is specified by channel transition probabilities (Lin, 1970). The coding theorem proves the existence of codes which can make the probability of erroneous decoding very small but gives no clue on how to construct such codes. However, it indicates that  $P_c$  can be

\* P is the probability of erroneous decoding.

reduced by increasing n. When n is increased, the complexity of the systemsincrease, sometimes exponentially with n. The ways by which the error rate of a system can be reduced are all dependent on the parameters contained in the famous expression below, where W represents the channel bandwidth and S/N is the signal-to-noise power ratio

$$C = W \log(1 + S/N)$$

derived by Shannon (1948). The most ingenious of all is the trading of bandwidth and signal-to-noise power ratio by the use of coding (i.e. the controlled addition of redundant information) to allow the receiver to detect and possibly correct errors using a decoder.

From this discussion, it becomes apparent that the objective of coding theory is to:

- (1) find long good codes

- (2) find practical methods for encoding and efficient decoding

The present need for processing enormous amounts of data, mostly digital, transmitted in many cases automatically and at high-speed, demands solutions that a few years ago would be considered impractical. The recent developments in digital hardware technology have made possible the use of fairly complex coding schemes and as more sophisticated processors become available, thanks to microelectronic technology, the advantages that can be gained by the use of coding will be even greater.

The second chapter in this thesis reviews some of the

published literature in the field and discusses the advantages of various coding techniques. After presenting linear block codes, attention is from then on concentrated on cyclic codes, which is the subject of Chapter 3.

The first part of Chapter 3 presents the mathematical background necessary for the study of cyclic codes and examines existing methods of encoding and their practical implementation. In the second part of Chapter 3 various ways of decoding cyclic codes are studied and from these considerations a general decoder for cyclic codes is devised and is presented in Chapter 4. Also a review of the principal classes of cyclic codes is presented.

Chapter 4 describes an experimental system constructed for measuring the performance of cyclic codes initially perturbed by random errors and then by bursts of errors. Simulated channels are used both for random and burst errors. A computer simulation of the whole system was made in order to verify the accuracy of the experimental results obtained.

Chapter 5 presents the various results obtained with the experimental system and by computer simulation which allow a comparison of the efficiency of various cyclic codes to be made. Finally, Chapter 6 summarises and discusses the main results of the research and suggests interesting points for future investigation in the area.

The main objective of this research is to contribute towards the solution of a fairly wide range of problems arising in the design of efficient coding schemes for practical applications; i.e. a study of coding from an engineering point of view.

#### CHAPTER 2

#### Survey of Coding

#### 2.1 Introduction

Since the advent of the coding theorem (Shannon, 1948) and of Hamming's Single-Error-Correcting Code (Hamming, 1950), coding theory has developed enormously, and at present it generates a fairly extensive area of research. Apart from the more general applications, there are codes designed for special applications like synchronisation recovery (Stiffler, 1971), asymmetric channels (Kautz and Levitt, 1969), comma-free codes (Scholtz, 1969), etc., but these are not studied here. After a brief discussion of the two main types of code construction this survey is directed towards linear binary group codes. By comparison with other types of codes, linear codes are fairly well developed and understood.

#### 2.2 Block and Convolutional Codes

Depending on how redundancy is added to blocks of information digits two basically different types of code result. Codes for which the redundancy in a block checks for errors only in that particular block are called <u>block</u> codes. Codes where the redundancy in a block checks for

errors in more than one block are called <u>convolutional</u> <u>codes</u> (Elias, 1955). There is no intention here of considering convolutional codes any further; their definition has been given just to point out the basic difference between block and convolutional codes. For a treatment of convolutional codes see Peterson (1972). Block and convolutional codes are competitive in many situations. The final choice between them is a function of factors like the data format, the decoding delay, the complexity of the overall system needed to achieve a specified output error rate, etc.

#### 2.3 Linear Block Codes

Block codes can be linear or nonlinear. For linear codes the redundant digits are calculated with modulo-2 adders while nonlinear codes require the use of nonlinear logic like AND, NOR, NAND gates, etc. However, the overwhelming majority of published articles on block codes is concerned with the linear case. The reason for this is the fact that linear block codes turn out to be mathematically more tractable, and in general are simpler to implement in practice, than nonlinear block codes. Despite these difficulties there is still research being done on nonlinear codes, and discoveries like that of a (15,8) code which corrects two random errors per block (Nordstrom et al,1967) which it is impossible to obtain by linear means, stimulates further work in nonlinear code construction techniques. The theory of linear block codes owes much to the work of

Hamming (1950), Golay (1949) and Slepian (1956a, 1956b, 1960). The treatment of linear block codes that follows uses the concept of vector space (see Appendix I for definition of terms), and only binary codes are assumed throughout unless the contrary is specified. Linear block codes are normally represented by the ordered pair (n,k) where n represents the number of digits in each codeword and is referred to as block length, and k is the number of information digits per block; or the ordered triplet (n,k,d) where n and k are the same as before and d is the code minimum distance (to be defined later in this chapter).

<u>DEFINITION</u> 2.1 An (n,k) linear block code is a set of  $2^k$  n-tuples which form a subspace of the vector space of all n-tuples.

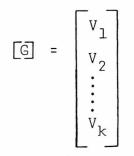

#### 2.4 Generator Matrix

An (n,k) binary code has 2<sup>k</sup> distinct codewords, each of them n digits long. To use such a code, without further consideration, it is necessary to store n×2<sup>k</sup> binary digits (bits) at the transmitter. This is one way of having the 2<sup>k</sup> codewords ready for transmission. However, when the 2<sup>k</sup> n-tuples form a subspace of the space of all n-tuples (i.e. a linear code) it is possible to obtain a set of k linearly independent vectors\*, which by linear combinations generate all the elements of the subspace. For example if:

The words vector and codeword will be used interchangeably throughout this thesis.

$$[v_1], [v_2], \dots, [v_k]$$

are k independent n-tuples (i.e. form a basis) then any other n-tuple in their subspace can be obtained as:

$$[U] = m_1 [V_1] + m_2 [V_2] + \ldots + m_k [V_k]$$

where  $m_i$  is either zero or one, and  $1 \le i \le k$ . Then, the way to generate the 2<sup>k</sup> codewords for a linear block code is best described in terms of a generator matrix [G]. The rows of the generator matrix are chosen to be k independent vectors from the code alphabet; i.e. [G] is a k×n matrix where the rows form a basis:

Any codeword in the code can be generated as follows. Let  $[m] = [m_1, m_2, \ldots, m_k]$  be a message sequence. The matrix product  $[m] \cdot [G]$  results in a vector [U], which is a linear combination of rows of [G]:

$$[U] = [m] \cdot [G] = m_1 [V_1] + m_2 [V_2] + \ldots + m_k [V_k]$$

[U] is the codeword associated with the k-tuple message block [m] and the matrix [G] is called the generator matrix of the code. It should be clear that the use of linear block codes reduces considerably the storage requirements at the transmitter. Basically, the encoder for a linear block code can consist of enough storage elements to accommodate the k rows of [G] and a logic circuit to perform a linear combination of these rows according to the incoming message sequence. Since [G] is non-singular (Peterson, 1961), it is possible to write [G] =  $[I_k : g]$  where  $I_k$  is a k×k unit matrix and g is a k×(n-k) matrix. In this situation [G] is said to be in standard echelon form and the codewords it generates have the first k positions occupied by the information digits while the last n-k digits are linear combinations of these information digits. A code with this structure is said to be <u>systematic</u>. The n-k redundant digits of a codeword are called parity checks and the linear functions that give the parity checks are called parity check equations.

#### 2.5 Parity Check Matrix

Given the k×n matrix [G] of a linear code it is possible to find a (n-k)×n matrix [H] such that the row space of [G]is orthogonal to [H], i.e. if  $[V_1]$  is a vector in the row space of [G] then  $[V_1] \cdot [H]^T = 0$ . The [H] matrix is called the parity check matrix of the code and can be represented as  $[H] = [h] : I_{n-k}$  where h is an (n-k)×k matrix and  $I_{n-k}$  is an (n-k)×(n-k) unit matrix. It can be shown that  $[h] = [g]^T$ where  $[g]^T$  is the transpose of the [g] matrix. Since the rows of [H] are linearly independent they generate an (n,n-k) linear code which is called the dual of the (n,k) linear code generated by [G]. This (n,n-k) code can be regarded as the

null-space of the (n,k) code generated by [G].

#### 2.6 Error Syndrome and Decoding

Suppose a codeword [V] in a linear block code with generator matrix [G] and parity check matrix [H] is transmitted through a noisy channel. At the receiver an n-tuple [R] is received which may differ from [V] due to the noise added in the channel during transmission. It is the task of the decoder to recover [V] from [R]. The first step is to check whether [R] is a codeword. This step can be represented by the equation below.

## $[R][H]^T = [S]$

where [S] is an (n-k)-tuple called the syndrome of [R]. If [S] = [O] (an all zero (n-k)-tuple) it is assumed that no errors occurred, i.e. [R] is assumed to be equal to [V]. However, if  $[S] \neq [O]$ , [R] does not correspond to a code vector in the row space of [G] and the decoder uses this syndrome for error detection and/or correction purposes. The received n-tuple [R] can be written as [R] = [V] + [E]where [E] is an n-tuple representing the error pattern. A number of relevant terms is presented below which are very useful in establishing the error correcting properties of linear block codes.

<u>DEFINITION</u> 2.2 The number of non-zero components of an n-tuple [V] is called the <u>Hamming weight</u> of [V] and is denoted by W(V).

<u>DEFINITION</u> 2.3 The number of positions in which two n-tuples  $[V_1]$  and  $[V_2]$  differ is called the <u>Hamming distance</u> between  $[V_1]$  and  $[V_2]$  and is denoted by  $d_{(V_1,V_2)}$ .

<u>DEFINITION</u> 2.4 The smallest distance between any pair of codewords in a code is called the <u>minimum distance</u> of the code, denoted  $d_{min}$  or simply d.

Due to the group properties of vector spaces, the addition of two codewords in a linear code gives as a result another codeword. This fact can be represented as:

$$\begin{bmatrix} v_1 \end{bmatrix} + \begin{bmatrix} v_2 \end{bmatrix} = \begin{bmatrix} v_1 + v_2 \end{bmatrix} = \begin{bmatrix} v_3 \end{bmatrix}$$

So,

$W(V_1+V_2) = W(V_3)$

or

$d_{(v_1,v_2)} = W_{(v_3)}$

The last expression above means that for linear codes the minimum distance is equal to the weight of the minimum weight non-zero codeword. With the exception of Hamming codes (d=3 and d=4), which are described later, the problem of constructing non-trivial error correcting codes with a given d is very difficult. In the linear case an important property for code construction is now introduced which relates d with the parity check matrix [H]. If the minimum weight non-zero codeword is multiplied by the code parity check matrix [H], the result is obviously an all zero (n-k)-tuple. This all zero (n-k)-tuple can be thought of as resulting from a linear combination of d columns of [H]. Consequently, no linear combination of less than d columns of [H] will give as a result an all zero (n-k)-tuple; otherwise the code minimum distance would be less than d. The minimum distance of a linear code can be expressed in terms of the [H] matrix as follows.

THEOREM 2.1 A linear code whose parity check matrix[H] contains d-l linearly independent columns has minimum distance at least d.

For a formal proof of Theorem 2.1 see Peterson (1972).

Though only the Hamming metric is considered in this thesis, other metrics exist, e.g. the Lee metric (Lee, 1958); the choice of a particular metric, aiming at optimum results, is a function of the type of modulation and channel characteristic to be used (see Berlekamp, 1968).

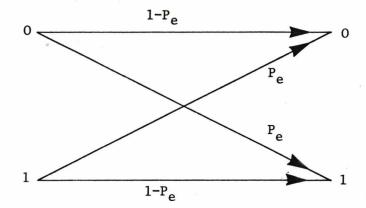

In order to assess the performance of a coding scheme it is vital to have a knowledge of the statistical behaviour of the channel. In practice, these statistics normally turn out to be very difficult to obtain and a theoretical model of the channel is used instead. One of the most commonly used channel models is that of the binary symmetric channel (B.S.C.) . The B.S.C. assumes that errors occur independently (i.e. the channel is memoryless) and that zeros and ones have the same probability of being in error (see Figure 2.1). In some applications it can be more convenient to use other channel models, e.g. the binary erasure channel (Elias, 1954).

FIGURE 2.1 : Binary Symmetric Channel

The ultimate performance that can be achieved with error correcting codes is theoretically expressed in terms of bounds (Hamming, 1950; Gilbert, 1952; Plotkin, 1960; Varshamov, 1957). There are many classes of codes which meet these bounds for small values of block length, but which soon fall short in performance as n is increased. For a code with minimum distance d to be able to correct t or less errors per codeword, the following inequality must hold:

$d \ge 2 t+1$  (Peterson, 1961).

In general, to correct C errors and to detect D errors per codeword, the inequality above is expressed as:

### $d \geq C+D+1$ ,

where  $D \ge C$  as errors must be detected before they can be corrected.

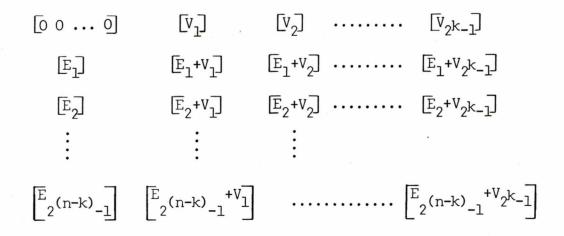

#### 2.7 The Standard Array

When an n-tuple [R] is received, the decoder has to decide among all possible codewords which particular codeword has been transmitted. In order to properly consider this decoding problem, it is sometimes convenient to use the concept of the standard array. This applies to linear codes, and consists of splitting the vector space containing the 2<sup>n</sup> distinct n-tuples into 2<sup>k</sup> disjoint subsets, each one of them containing one and only one codeword. The 2 $^{\rm k}$  disjoint subsets are constructed as follows. Write all the 2<sup>k</sup> code vectors in a row. Below the all zero codeword, write an n-tuple  $[E_1]$  which does not appear in the first row. This n-tuple can be associated with an error pattern which the code is to detect and/or correct, as will be shown later. The second row is formed by adding  $[E_1]$  to each of the nonzero code vectors as indicated below:

$\begin{bmatrix} 0 & \cdots & 0 \end{bmatrix} \begin{bmatrix} v_1 \end{bmatrix} \begin{bmatrix} v_2 \end{bmatrix} & \cdots & \begin{bmatrix} v_2 k_{-1} \end{bmatrix}$  $\begin{bmatrix} E_1 \end{bmatrix} \begin{bmatrix} E_1 + v_2 \end{bmatrix} & \begin{bmatrix} E_1 + v_2 \end{bmatrix} & \cdots & \begin{bmatrix} E_1 + v_2 k_{-1} \end{bmatrix}$

The third and consecutive rows are constructed in a similar manner, every new row starting with an n-tuple not used before. The following table results:

#### TABLE 1

The  $2^{n-k}$  rows in the table above are called cosets and the leading element in each row is called the coset leader. This table is called the <u>standard array</u> or the <u>coset decomposition</u> of the code.

The syndrome [S] associated with an n-tuple [R] is given by:

$[S] = [R] \cdot [H]^{T} = [E+V] \cdot [H]^{T} = [E] \cdot [H]^{T} + [V] \cdot [H]^{T} = [E] \cdot [H]^{T}$

since  $[V] \cdot [H]^T = 0$ , i.e.  $[S] = [E] \cdot [H]^T$ . This equation for the syndrome clearly shows that all elements in one coset of the standard array have the same syndrome because it depends only on the <u>coset leader</u> n-tuple [E]. This suggests the use of the standard array and the equation  $[S] = [E] \cdot [H]^T$  to decode linear codes as follows:

(1) Calculate the syndrome [S] of a received n-tuple [R]. (2) Find the coset leader  $[E_i]$  associated with this syndrome.

This coset leader is assumed to be the errors introduced by noise on the channel.

(3) Subtract the coset leader found in step 2 above from [R] in order to obtain the estimate of the transmitted codeword, i.e.  $[V_i] = [R] - [E_i]$ .

From these discussions it is concluded that, based on noise statistics of the channel, the coset leaders should be chosen as the most likely error patterns. However, as mentioned earlier, detailed statistics of the noise are not always available and it usually becomes very difficult to find codes to exactly match the channel. Also, in order to use the standard array, it is necessary to find the coset (and therefore the appropriate coset leader) to which the received n-tuple belongs. This is, in general, not easy to implement, so that the concept of the standard array is more useful as a way of understanding the structure of linear codes, rather than as a practical decoding algorithm.

Two potentially practical methods of decoding linear codes are now presented. Further procedures are described in Peterson (1972) and Lucky et al (1968), but so far the use of the linearity property alone has not resulted in any simple decoding algorithm for linear codes, at least in the published literature.

#### 2.8 Maximum Likelihood Decoding

If the codewords of an (n,k) code are selected independently and all have the same probability of being sent

through a channel, an optimum way of decoding them is as follows. On receiving an n-tuple [R], the decoder compares it with all possible codewords in the code. For the binary case this means comparing [R] with the 2<sup>k</sup> distinct n-tuples which form the code. Select the codeword which is nearest to [R] in terms of Hamming distance, i.e. the word which differs from [R] in the least number of places. This is assumed to be the transmitted codeword. Unfortunately, the time required to decode a received n-tuple can become prohibitively long even for moderate values of k. It should be noted that the decoder has to compare [R] with 2<sup>k</sup> codewords during a time interval corresponding to the duration of n channel digits. This fact makes this process of decoding inadequate for many practical cases.

#### 2.9 Systematic Search Decoding

A general procedure for decoding linear block codes consists of associating a correctable error pattern with each of the non-zero syndromes. It has been mentioned before that one property of the standard array is that all n-tuples belonging to one coset have the same syndrome. Also, the coset leaders should be chosen as the most likely error patterns in their cosets. A simple way of decoding these codes is:

(1) Calculate the syndrome for the received n-tuple.

(2) By systematic search find the correctable error pattern, (coset leader), associated with the syndrome of the received n-tuple.

(3) Subtract the error pattern found in step 2 from the received n-tuple in order to remove the errors from it.

To implement this procedure it is necessary to generate all correctable error patterns successively, and feed them into a combinational circuit that gives the associated syndromes at its output. Using a multiple input logic gate it is possible to detect when the locally generated syndrome matches the syndrome of the received n-tuple. If this (n,k) code is t error correcting, the total number of patterns it is necessary to generate in the search is given by (Lucky et al, 1968):

$$C_n^1 + C_n^2 + \dots + C_n^t = \sum_{i=1}^t C_n^i \le 2^{n-k} - 1$$

From this expression it is easy to see that the number of error patterns increases very rapidly with n and t. This fact sets a limit to the applicability of this technique.

The decoding methods described above in sections 2.8 and 2.9 are generally applicable to all linear block codes. Less complex methods of decoding can be devised for certain classes of linear codes, by virtue of their particular structure. Some simple block codes are now presented.

#### 2.10 Single Parity Check (S.P.C.) Codes

These constitute one of the simplest forms of coding because only one redundant digit (parity check) is used per codeword. This parity check digit is calculated according

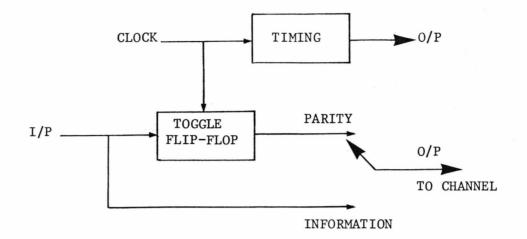

to the following rule. Make the parity check digit equal to one if the number of ones in the information block is odd; otherwise make the parity check equal to zero. This procedure is equivalent to making the check digit equal to the sum modulo-2 of the information digits in a block, i.e. a linear code results. By using this rule to calculate the parity check, the number of ONES in a codeword is always even\*. As a consequence of the presence of the single parity check, the decoder is able to detect any odd number of errors but fails to detect an even number of errors. Thus, these codes have minimum distance d=2. Figure 2.2 shows the diagram of an encoder for these codes. A toggle flip-flop is used to calculate the parity check. The output of this type of flipflop changes with the next clock pulse whenever the present input is a one. With the flip-flop initially reset, information digits are sent to the channel and simultaneously into the encoder. After k shifts, an odd number of ones in the information section causes a one to appear at the output of the flip-flop; otherwise a zero will be produced. A timing circuit controls the delivery of information and parity digits to the channel.

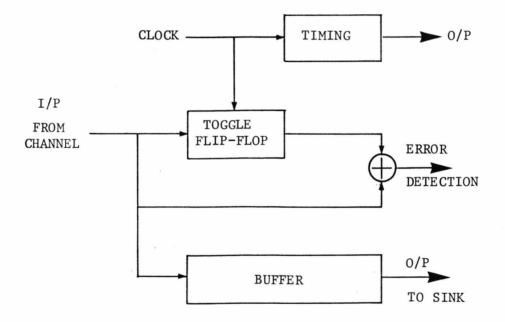

The decoding rule for S.P.C. codes is simply to count the number of ones in a received block. If the resulting count is even, the received block is assumed to be error-free and can be delivered to the data sink. If the count gives an odd number, errors have been detected and the received block is either tagged and delivered to the data sink or just dis-

<sup>\*</sup> An alternative way of calculating the check digit (odd parity) is by making it equal to zero when the number of ones in the information block is odd; otherwise the parity check is made equal to one.

FIGURE 2.2 : Encoder for S.P.C. Codes

carded. Another alternative is to ask the transmitter, assuming a feedback channel is available, to retransmit the erroneous block. This last possibility is called automatic repeat request (A.R.Q.). Though S.P.C. codes permit only error detection, they are very powerful in systems using A.R.Q., because their efficiency is usually high for moderate n and the circuitry required for their implementation is very simple. The efficiency of S.P.C. codes is given by the expression:

$$R = \frac{k}{n} = \frac{n-1}{n} = 1 - \frac{1}{n}$$

It is clear from this expression that R approaches 1 as n is increased. This improved efficiency should always be weighed against the increase in the probability of undetected errors. The block error rate for S.P.C. codes in a B.S.C. channel is given by (Farrell, 1969):

$$P_c = C_n^2 P_e^2 (1-P_e)^{n-2} + C_n^4 P_e^4 (1-P_e)^{n-4} + \dots$$

If  $P_e$  is sufficiently small  $P_c$  can be approximated as

$$P_{c} = C_{n}^{2} P_{e}^{2} (1-P_{e})^{n-2}$$

Figure 2.3 shows the diagram of a decoder for S.P.C. codes.

FIGURE 2.3 : Decoder for S.P.C. Codes

### 2.11 Hamming Codes

These codes (Hamming, 1950), were the first non-trivial error correcting codes to be proposed. Hamming codes are linear single error correcting codes, i.e. their minimum distance is d=3.They have block length  $n\leq 2^{c}-1$ , where c is the number of parity check digits. This condition on n ensures the availability of sufficient redundancy to check for single errors in a codeword since then the number of non-zero syndromes  $(2^{C}-1)$  is always greater than or equal to the number of single error positions (n). The construction of the parity check equations for these codes is best explained with the aid of an example.

EXAMPLE. Consider the construction of the (7,4) Hamming code. The ideas described here are easily generalised for any (n,k) Hamming code. The number of check digits for this (7,4) code is c=7-4=3. Consider the non-zero binary numbers that can be formed using c=3 digits.

TABLE 2

| i.e. | 001   | cl             |

|------|-------|----------------|

|      | 0 1 0 | °2             |

|      | 0 1 1 | kl             |

|      | 100   | c <sub>3</sub> |

|      | lOl   | k <sub>2</sub> |

|      | 1 1 0 | k <sub>3</sub> |

|      | 1 1 1 | k <sub>4</sub> |

Hamming associated the numbers of the form 2<sup>i</sup>, i = 0,1,2, ... with parity check positions. The other positions were associated with information digits, as indicated in the table above. Now, looking down the columns, the parity check equations are written as the modulo-2 addition of the information positions where a one appears in the particular column being considered.

i.e.

$$c_1 = k_1 + k_2 + k_4$$

$c_2 = k_1 + k_3 + k_4$

$c_3 = k_2 + k_3 + k_4$

On receiving a codeword, the decoder recalculates the parity checks and adds them modulo-2 to the received ones in order to obtain the syndrome. If, for example,  $k_3$  is in error, parity checks  $c_2$  and  $c_3$  will fail while  $c_1$  will agree because it does not check  $k_3$ . This situation is represented as:

This binary number corresponds to the position of k<sub>3</sub> in the table considered above. The error is thus located and can then be corrected. This method generalises to cover any value of n. For practical reasons the codewords are normally transmitted in a systematic manner. In his work, Hamming (1950) also mentioned that the minimum distance of these codes can be increased by 1 to become d=4, by annexing an overall parity check to each codeword. This overall parity check is determined in the same manner as the one for S.P.C. codes, i.e. by the modulo-2 addition of all other digits in the codeword. This procedure applies not only to Hamming codes but to any code with an odd minimum distance (Peterson, 1972), i.e. if d is odd, by annexing an overall parity check the new minimum distance is d+1. Hamming codes

are quite unique in the sense that no other class of nontrivial error correcting codes can be so easily decoded, and also because Hamming codes are perfect or quasi-perfect codes as defined below.

<u>DEFINITION</u> 2.5 An (n,k) t-error-correcting code is called a perfect code if, and only if,

q = number of levels  $\sum_{i=0}^{t} C_{n}^{i} = q^{n-k}$

Codes in which the information digits are repeated a number of times are called repetition codes and are perfect in a trivial sense. Repetition codes are decoded by taking a majority vote. Apart from the Hamming codes, the (23,12) t=3 Golay code and the ternary (11,6)t=3 code, there are no other non-trivial perfect codes (van Lint, 1970; Tietäväinen, 1973). Codes where

$$\sum_{i=0}^{t+1} C_n^i > q^{n-k} > \sum_{i=0}^{t} C_n^i$$

are called the quasi-perfect if the remaining redundancy can be used to correct only some of the patterns containing t+1 errors. Perfect and quasi-perfect codes are optimum (i.e. they minimise the probability of error) when used in a B.S.C. (Slepian, 1956a).

### 2.12 Product Codes

These codes are usually linear and result from a combination of two or more codes in order to obtain a more powerful code. When two codes are used to form a product code, the information digits may be arranged in a rectangular matrix form, and row and column parity check digits are calculated in accordance with the coding rules for the two codes respectively, along each of the two dimensions. The minimum distance of this product code is  $d = d_1 \times d_2$ , where  $d_1$  and  $d_2$  are the individual minimum distances of the two codes used (Elias, 1954). The resulting two dimensional array has the following general structure:

| INFORMATION | ROW    |

|-------------|--------|

| DIGITS      | PARITY |

|             | CHECKS |

| COLUMN      | CHECKS |

| PARITY      | ON     |

| CHECKS      | CHECKS |

Product codes are efficient when used for error detection with A.R.Q. (Farrell, 1969) because a very low probability of undetected error can be achieved. Also they find practical use in coding for digital multiplex systems (Riley, 1975) and in general wherever the data format is rectangular. Product codes have been studied by Elias (1954), Burton and Weldon (1965), Berlekamp (1968), and

Peterson (1972), and others.

# 2.13 Constant Weight Codes

These codes are also known as: fixed ratio, m out of n and constant ratio codes. Their characteristic is to have codewords all with the same weight i.e., the same number of ONES.

The number of codewords in an m out of n code is given by:

$$M = \frac{n!}{m!(n-m)!}$$

The van Duuren A.R.Q. system (van Duuren, 1961) uses a 3 out of 7 constant weight code and is a good example of the use of such codes on radio-telegraph circuits. In this case any single error causes a received block to have either weight 2 or 4 and so is detected. However, a double error can happen which changes a one into a zero and a zero into a one and this will pass undetected. In general, these codes are guaranteed to detect odd numbers of errors but can fail to detect an even number of them. Constant weight codes are less efficient than S.P.C. codes but can have their error detecting capability improved by carefully reducing the number of codewords. These codes are very often nonlinear, but there are exceptions like the m-sequence codes (see Chapter 3).

The next chapter introduces cyclic codes which are linear codes with some additional mathematical structure. This allows relatively simple decoders to be constructed for codes normally more powerful than the ones presented above.

### CHAPTER 3

### Cyclic Codes

## 3.1 Introduction

The codes described in this chapter constitute the most powerful sub-class of linear block codes as far as practical implementation and mathematical structure are concerned. Prange (1957) was the first to study cyclic codes. Subsequently, these codes have been studied in the context of modern algebra using the concepts of Galois fields, (see Peterson, 1972 and Berlekamp, 1968).

# 3.2 Basic Definitions

<u>Definition</u> 3.1 A linear block code is called a cyclic code if the result of any cyclic permutation of any of its codewords is another valid codeword, i.e. if  $\begin{bmatrix} V \end{bmatrix} = \begin{bmatrix} V_0, V_1, V_2, \dots, V_{n-1} \end{bmatrix}$  is a codeword,  $\begin{bmatrix} V^{i} \end{bmatrix} = \begin{bmatrix} V_{n-i}, V_{n-i+1}, \dots, V_0, V_1, \dots, V_{n-i-1} \end{bmatrix}$  is also a codeword in the same code, and the indices are reduced modulo-n.

Any n-tuple like [V] above, can be represented in the form of a polynomial V(x) of degree at most n-l as follows:

$$V(X) = V_0 + V_1 x + V_2 x^2 + \dots + V_{n-1} x^{n-1}$$

With the use of the properties of finite fields it can be proved (see Peterson (1961), for example) that all codewords of an (n,k) cyclic code are multiples of a polynomial G(x), of degree n-k, which is unique; and conversely that every polynomial of degree n-l or less which is a multiple of G(x) must be a codeword. Furthermore, G(x) is called the code generator polynomial, and it divides  $X^{n}$ +l. The mathematical properties just mentioned for cyclic codes are those of a mathematical ideal (see Appendix I for definition). This allows the properties of cyclic codes to be derived from the study of ideals and an equivalent definition of cyclic codes is:

<u>Definition</u> 3.2 Cyclic codes are ideals in the algebra of polynomials modulo X<sup>n</sup>+1.

The factorisation of  $X^{n}+1$  gives as a result:  $X^{n}+1 = (X+\alpha_{1})(X+\alpha_{2})(X+\alpha_{3})...(X+\alpha_{n})$ , where the roots  $\alpha_{1}(1 \le i \le n)$  are elements of an extension field. Each of these n roots can be expressed as a power of  $\alpha$ , where  $\alpha$  is called a primitive root, i.e.  $\alpha, \alpha^{2}, \alpha^{3}, ..., \alpha^{n-1}, \alpha^{n}=1=\alpha^{0}$ . The lowest degree polynomial with binary coefficients which is a factor of  $X^{n}+1$  and contains  $\alpha_{1}$  as a root is called the minimum polynomial of  $\alpha_{1}$ . If  $n = 2^{m}-1$  it can be shown that the maximum degree of a minimum polynomial  $m_{\alpha_{1}}(x)$  is m. In the binary case  $m_{\alpha_{1}}^{2}(x) = m_{\alpha_{1}}(x^{2})$  which implies that if  $\alpha_{j}$  is a root of  $m_{\alpha_{1}}(x)$  so are  $\alpha_{j}^{2}, \alpha_{j}^{4}, ...,$ i.e. the minimum polynomial of any even power of  $\alpha$  is the same as the minimum polynomial of some odd power of  $\alpha$ . Cyclic codes can also be specified in terms of the roots of G(x), in an extension field. If G(x) has non-repeated

roots  $\alpha_1, \alpha_2, \ldots, \alpha_{n-k}$  then any polynomial V(x) will belong the code if, and only if,  $V_{(\alpha_i)}=0$ ,  $1 \le i \le n-k$ .

THEOREM 3.1 If  $\beta$  is a root of a polynomial V(x), then V(x) is divisible by M(x), the minimum polynomial of  $\beta$ .

PROOF Let V(x) = P(x)M(x)+S(x)

Then  $V(\beta) = P(\beta)M(\beta)+S(\beta)=0$  and,

$S(\beta)=0$ , since  $V(\beta)=M(\beta)=0$ . By the Euclidean division algorithm S(x) is of degree less than M(x) and so it must be zero, (i.e. S(x)=0) because the definition of minimal polynomial guarantees M(x) to be the lowest degree polynomial with  $\beta$  as a root.

Q.E.D.

As a consequence of Theorem 3.1, if the minimum polynomial of  $\alpha_i$  is  $M_{\alpha_i}(x)$  then V(x) is a codeword in a cyclic code if and only if V(x) is divisible by  $M_{\alpha_1}(x), M_{\alpha_2}(x), \ldots, M_{\alpha_{n-k}}(x)$ , i.e. V(x) must divide the least common multiple of  $M_{\alpha_1}(x), M_{\alpha_2}(x), \ldots, M_{\alpha_{n-k}}(x)$ . Therefore, the code generator polynomial G(x) can be written as:

$G(\mathbf{x}) = L C M\{M_{\alpha_1}(\mathbf{x}), M_{\alpha_2}(\mathbf{x}), \dots, M_{\alpha_{n-k}}(\mathbf{x})\}$

where  $\alpha_i$ ,  $(1 \le i \le n-k)$  are the roots of G(x). If a cyclic code is required to have a generator polynomial G(x) with a root  $\alpha_i$  repeated p times, then the minimum polynomial of  $\alpha_i$  must appear p times as a factor of G(x). The condition for  $X^n+1$  to have only distinct roots is that the block length n and the number of levels q must be relatively prime (Peterson, 1961). In the binary case, this condition simply means that n must be odd for the roots of  $X^{n}$ +l to be distinct.

# 3.3 Matrix Representation of Cyclic Codes

From the definition of cyclic codes, the multiples of the generator polynomial G(x) are codewords. So the polynomials  $G(x), xG(x), x^2G(x), \ldots, x^{k-1}G(x)$  are all codewords, and are also linearly independent. Using these polynomials the following matrix can be formed, which represents the generator matrix of a cyclic code with generator polynomial G(x).

$$\begin{bmatrix} G \end{bmatrix} = \begin{bmatrix} x^{k-1}G(x) \\ \vdots \\ x^{2}G(x) \\ xG(x) \\ G(x) \end{bmatrix}$$

For encoding purposes the cyclic shift property allows a sequential implementation of [G] which is described in section 3.4. Also described there is a sequential implementation of the parity check matrix [H] as a function of the code parity check polynomial H(x). This relatively simple implementation turns out to be of great practical advantage for cyclic codes. Let  $V(x) = V_0 + V_1 x + V_2 x^2 + \ldots + V_{n-1} x^{n-1}$  be a codeword in a cyclic code with generator polynomial G(x) having roots  $\alpha_1, \alpha_2, \ldots, \alpha_{n-k}$ , i.e.  $V(\alpha_i)^{=0=} V_0 + V_1 \alpha_i + V_2 \alpha_i^2 + \ldots + V_{n-1} \alpha_i^{n-1}$ , where  $1 \le i \le n-k$ . This expression can be written as a matrix product as follows:

$$\begin{bmatrix} \mathbf{v}_0, \mathbf{v}_1, \mathbf{v}_2, \dots, \mathbf{v}_{n-1} \end{bmatrix} \cdot \begin{bmatrix} \mathbf{1}, \mathbf{\alpha}_1, \mathbf{\alpha}_1^2, \dots, \mathbf{\alpha}_1^{n-1} \end{bmatrix}^T = \mathbf{0}$$

or, in other words, V(x) is a codeword if and only if it is in the null space of the matrix [H] :

$$[H] = \begin{bmatrix} 1 & \alpha_1 & \alpha_1^2 & \alpha_1^{n-1} \\ 1 & \alpha_2 & \alpha_2^2 & \alpha_2^{n-1} \\ \vdots & \vdots & \vdots & \vdots \\ \vdots & \ddots & \vdots & \vdots \\ 1 & \alpha_{n-k} & \alpha_{n-k}^2 & \alpha_{n-k}^{n-1} \end{bmatrix}$$

# 3.4 Encoding With An (n-k)-Stage Shift-Register

This encoding procedure is based on the property that all codewords in a cyclic code are multiples of the code generator polynomial G(x). The k information digits can be represented by a polynomial I(x) of degree less than k as follows:

$$I(x) = k_1 x^{k-1} + k_2 x^{k-2} + \dots + k_k$$

where the  $k_i$   $(1 \le i \le k)$  are the information digits. Multiplying the information polynomial I(x) by  $x^{n-k}$  gives  $x^{n-k}I(x)$  which is of degree not greater than (n-1) and contains no terms of degree less than (n-k). Division of  $x^{n-k}I(x)$  by G(x) gives as a result

$$x^{n-k}I(x) = P(x)G(x) + C(x)$$

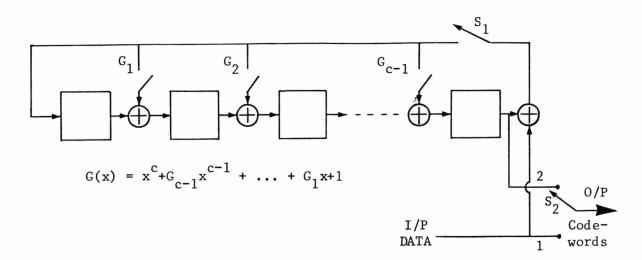

where P(x) and C(x) are respectively quotient and remainder polynomials. C(x), being the remainder, is of degree smaller than the degree of G(x), i.e.  $\leq (n-k)-1$ . If C(x) is subtracted from  $x^{n-k}I(x)$  the result is a multiple of G(x), i.e. a codeword. Also, since C(x) has degree  $\leq n-k-1$ , it represents the parity checks and does not overlap with the information section represented by  $x^{n-k}I(x)$ . The operations described can be performed by the circuit shown in Figure 3.1, keeping in mind that modulo-2 addition and subtraction are the same.

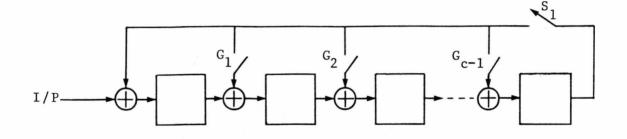

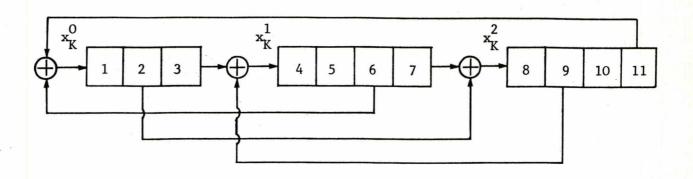

# FIGURE 3.1 : Encoder Using (n-k) S.R. Stages

The circuit shown in Figure 3.1 uses (n-k)-stages of shiftregister and pre-multiplies the information polynomial by  $x^{n-k}$  (Peterson, 1972). The switches  $G_{1}G_{2}, \ldots, G_{c-1}$  are

closed wherever the corresponding coefficient in G(x) is a ONE; otherwise they are left open. Starting with all zeros in the shift register, switches  $S_1$  closed and  $S_2$  in position 1, information digits are sent to the output and simultaneously into the division circuit. After the k information digits have been sent out, and the remainder (i.e. the parity checks) is in the register, switch  $S_1$  is opened and  $S_2$  is moved to position 2. During the next (n-k) clock pulses the parity checks are transmitted. This process is repeated for the next block of information digits.

# 3.5 Encoding with a k-Stage Shift-Register

Since G(x) divides  $x^n-1$  it follows that

$$x^{n}-1 = G(x)H(x)$$

(3.1)

The polynomial H(x) completely specifies an (n,k) cyclic code with generator polynomial G(x), as will be shown. Let V(x) be a codeword, i.e.

$$V(x) = P(x)G(x)$$

(3.2)

where  $V(x) = V_0 + V_1 x + V_2 x^2 + \ldots + V_{n-1} x^{n-1}$ . Multiplying both sides in (3.2) by H(x) gives:

$$V(x)H(x) = P(x)G(x)H(x)$$

(3.3)

or,  $V(x)H(x) = P(x)(x^{n}-1)=P(x)x^{n}-P(x)$  (3.4)

From (3.2) it is seen that P(x) has degree at most k-1. This fact allows us to conclude that (3.4) can not contain the terms  $x^k, x^{k+1}, \ldots, x^{n-1}$ , i.e. their coefficients in (3.4) are zero. This implies that:

$$\sum_{i=0}^{k} H_{i}V_{n-i-j} = 0 \quad \text{for } 1 \le j \le n-k \quad (3.5)$$

Since, from (3.1) it is known that  $H_0=1$  and  $H_k=1$ , (3.5) can be written as:

$$V_{n-k-j} = \sum_{i=0}^{k-1} H_i V_{n-i-j}$$

for  $l \le j \le n-k$  (3.6)

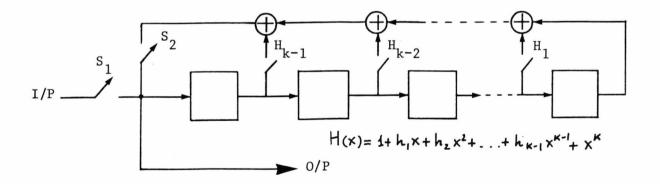

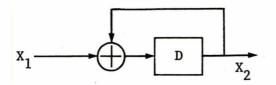

Expression (3.6) represents a recurrence relation which is also known as a difference equation (Lin, 1970) and provides a rule for calculating the parity check digits  $V_{n-k-1}$ ,  $V_{n-k-2},\ldots,V_0$ , given the k information digits  $V_{n-1},V_{n-2},V_{n-3}$ ,  $\ldots,V_{n-k}$ . So, an (n,k) cyclic code with generator polynomial G(x) is completely specified by the polynomial H(x), which is called the parity polynomial of the code. The following circuit diagram (Figure 3.2) shows an encoder based on expression (3.6), using a k-stage shift-register.

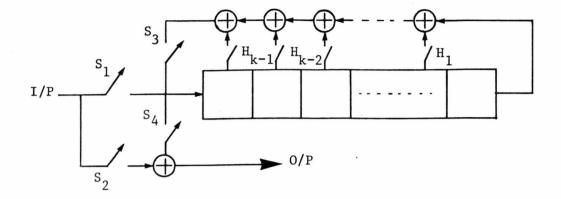

FIGURE 3.2 : Encoder Using k S.R. Stages

This circuit works as follows:

(1) With switch S<sub>1</sub> closed and S<sub>2</sub> open. Information

digits are clocked into the circuit and simultaneously to the output.

- (2) After k shifts, switch  $S_1$  is opened and  $S_2$  is closed. At the output appears  $V_{n-k-1}$ , where  $V_{n-k-1} = H_0 V_{n-1} + H_1 V_{n-2} + \cdots + H_{k-1} V_{n-k}$ , and this constitutes the first parity check.

- (3) After one clock shift the first parity check is sent out and into the encoding circuit. The second parity check then appears at the output  $V_{n-k-2} = H_0 V_{n-2} + H_1 V_{n-3} + \dots + H_{k-2} V_{n-k}$ +  $H_{k-1} V_{n-k-1}$ .

This procedure continues until the last parity check has been sent out, then switch S<sub>1</sub> is closed and S<sub>2</sub> is opened. The next information block can now be shifted into the encoding circuit. The k-stage shift-register encoder should be used whenever n-k>k; otherwise the (n-k)-stage encoding circuit is preferable. It should be observed, however, that the k-stage encoder can be implemented with conventional integrated circuit shift registers since it does not require any external gates to be connected in between stages. This can be an advantage even if n-k<k.

On the other hand, for the calculation of syndromes (see next section) and subsequent error correction the n-k stage circuit is normally preferred because the operation of multiplying the syndrome polynomial by x and reducing modulo G(x) is easily accomplished.

# 3.6 Syndrome Calculation

It is the function of the decoder, on receiving an n-tuple R(x), to check whether or not it is a valid codeword. This is necessary because after passing through a noisy channel, part of the received codeword may be corrupted by noise. If errors are detected, i.e. the syndrome is non-zero, then the decoder starts attempting correction. This section deals only with syndrome calculation and consequent error detection, leaving error correction for a future section. In the case of cyclic codes, both syndrome calculation, and subsequent error correction, are relatively more simple than in the case of linear codes in general.

Since in a cyclic code all the codewords are multiples of the code generator polynomial, the first action of the decoder is to check whether the received n-tuple is divisible by G(x). The remainder of this division is the syndrome, and if it is zero it can be assumed that no errors have occurred. A non-zero syndrome indicates that the decoder has detected errors and can proceed with correction. If R(x) is the received n-tuple it can be written as

$$R(x) = V(x) + E(x)$$

,

where V(x) and E(x) represent respectively the transmitted codeword and the error pattern. Division of R(x) by G(x)gives:

$$R(x) = Q(x)G(x) + S(x)$$

(3.7)

where S(x) is the syndrome polynomial and has degree at most (n-k-l) i.e. it is an (n-k)-tuple. Expression (3.7) above can be written as:

$$V(x) + E(x) = Q(x)G(x) + S(x)$$

(3.8)

or

$$P(x)G(x) + E(x) = Q(x)G(x) + S(x)$$

(3.9)

Finally,

$$E(x) = (Q(x) + P(x))G(x) + S(x)$$

(3.10)

It is clear from expression (3.10) that there is a definite relation between syndrome and error pattern; i.e.

$$S(x) = REM \left\{ \frac{E(x)}{G(x)} \right\}$$

This will be explored later for error correction purposes. It follows from the properties of the standard array (see Chapter 2) that different E(x) polynomials can lead to the same syndrome and in what follows E(x) will always be assumed to be the polynomial of smallest weight satisfying the relation

$$S(x) = \text{REM}\left\{\frac{E(x)}{G(x)}\right\}$$

.

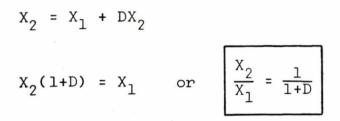

For the binary symmetric channel this leads to maximum likelihood decoding (Lucky et al, 1968). The circuits used for syndrome calculation are similar to those for the encoding of cyclic codes. This means that either k or (n-k)-stage syndrome calculating registers can be used. Figure 3.3 shows a circuit diagram for the (n-k) stage type of syndrome calculating register. Initially, the shift register contents are all zeros. The incoming ntuple is shifted into this circuit and after n clock pulses, the shift register has the syndrome as its contents. Before receiving the next n-tuple this shift register needs to be cleared. No pre-multiplication is required, since the received parity checks must be added to the recalculated parity checks anyway.

# FIGURE 3.3 : (n-k)-Stage Syndrome Calculating Register

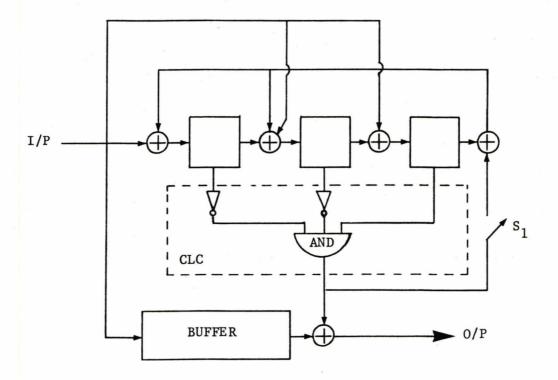

A k-stage syndrome calculating register is shown in Figure 3.4. In this circuit the incoming n-tuple is shifted into the register with switch  $S_1$  closed and switches  $S_2, S_3$  and  $S_4$  open. After k shifts switches  $S_2,$  $S_3$  and  $S_4$  are closed and  $S_1$  is opened, the recalculated parity checks are added modulo-2 to the received ones and the syndrome digits appear at the output.

FIGURE 3.4 : k-Stage Syndrome Calculating Register

# 3.6 Shortened Cyclic Codes

From an engineering point of view, it is important that a particular class of easily decodable codes should cover a wide range of code rates and error-correcting power. Since the generator polynomial of a cyclic code has to divide X<sup>n</sup>-1, the designer is left with a relatively small number of cyclic codes for a given n. However, for every i<k, it is possible to have an (n-i,k-i) code which is obtained from an (n,k) cyclic code by selecting all those codewords which begin with i zeros, and deleting these first i zeros. There are, of course, 2<sup>k-i</sup> codewords in this shortened code which is linear but no longer cyclic (Peterson, 1972). Encoding and syndrome calculation can be done with the circuits used for the original code since the i zeros deleted do not affect the calculation of the parity checks. This is the first important point

about shortened cyclic codes. They are as easy to implement as full cyclic codes. The second important point is that the Hamming distance of the shortened code is at least the same as that of the original code. For decoding the codewords are preceded by i zeros if the decoder for the original cyclic code is to be used. This solves the problem of decoding shortened cyclic codes, but the method does not fully exploit the fact that the redundancy of the code remains constant while the number of codewords has been reduced from  $2^k$  to  $2^{k-i}$ . This means that, potentially, more errors could be corrected with the shortened code because there are fewer information positions to be checked. Simplicity of implementation may offset the shortfall in performance, however, thus making shortened cyclic codes attractive in certain circumstances.

# 3.8 Pseudo-Cyclic Codes

So far what has been written about cyclic codes has implied working with polynomials reduced modulo  $X^{n}-1$ . If instead modulo f(x) is used, where f(x) is an arbitrary polynomial in x, the resulting codes are called pseudocyclic codes. Peterson (1972) proves the following theorems for cyclic codes:

<u>Theorem</u> 3.2 Every pseudo-cyclic code with minimum distance greater than 2 is a shortened cyclic code.

Theorem 3.3 Every shortened cyclic code is a

pseudo-cyclic code.\*

## 3.9 Decoding Cyclic Random Error Correcting Codes

In this section some of the more important algorithms for decoding cyclic codes are presented together with comments on their advantages and limitations. The decoding of random error correcting codes is in general a difficult matter, and one can say that in most practical situations, it is the complexity of the decoder that sets a limit as to which codes can be used. For cyclic codes, encoding and syndrome calculation have already been shown to be easily attainable with shift registers, modulo-2 adders, a few logic gates and a timing circuit.

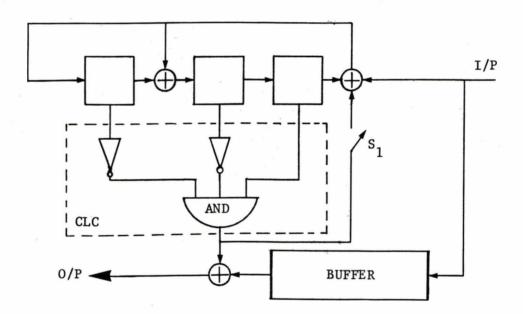

### 3.9.1 Meggitt Decoder

..

This type of decoder works as follows. A received ndigit codeword, possibly erroneous, is fed to a syndrome calculating register and simultaneously into a buffer register. The syndrome obtained is fed into a combinational logic circuit (CLC) whose output is a ONE if and only if this syndrome is associated with a correctable error pattern having an error in its highest order digit, i.e. an error in the first digit to be read out of the buffer register or the digit with highest degree in a polynomial representation.

In the multi-level case this still holds true because f(x) is a factor of  $x^{n}-1$ , for some n.

If the output of the CLC is zero, it is assumed that the highest order digit in the buffer is correct. So, the output from the CLC indicates whether the digit to come out from the buffer is in error or not. The contents of the buffer are read out one at a time, the syndrome register being shifted simultaneously. Every time a ONE is output from the CLC it is added modulo-2 to the buffer output and simultaneously to the feedback path of the syndrome register in order to remove the effect of the error from the syndrome calculation. After n shifts the contents of the syndrome register should be all zeros if the error pattern was a correctable one otherwise an uncorrectable error has been detected. A simple example is now given in order to make clear the points explained above.

<u>EXAMPLE</u> Consider the (7,4) single error correcting Hamming code whose generator polynomial is  $G(x)=x^3+x+1$ . The parity check equations for this code are:

> $c_1 = k_1 + k_2 + k_3$  $c_2 = k_2 + k_3 + k_4$  $c_3 = k_1 + k_2 + k_4$

Let the transmitted codeword be:

$\begin{bmatrix} k_1 & k_2 & k_3 & k_4 & c_1 & c_2 & c_3 \\ \begin{bmatrix} v \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 1 \end{bmatrix}$

Let the error vector be:

The received n-tuple will be:

R

=

[V]

+

[E]

R

=

[1]

1

1

0

0

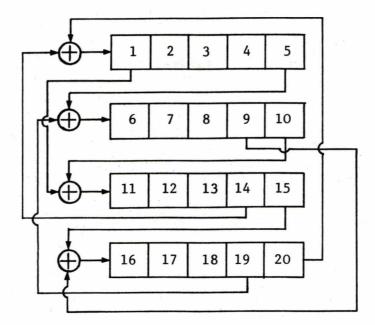

The received n-tuple is fed into the circuit shown in Figure 3.5 with the switch  $S_1$  open. The contents of the syndrome register after n shifts is the pattern

$$\begin{bmatrix} S \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 \end{bmatrix}$$

$$\begin{array}{c} c_1 & c_2 & c_3 \end{bmatrix}$$

FIGURE 3.5 : Meggitt Decoder for the (7,4) t=l Cyclic Code

S<sub>1</sub> is now closed and the contents of the buffer start being delivered, as follows in the table:

| Shift | Contents of<br>Syndrome Register | Output of<br>CLC | Output of<br>Buffer | Output of<br>Decoder |

|-------|----------------------------------|------------------|---------------------|----------------------|

| 1     | 001                              | 0                | 1                   | 1                    |

| 2     | 010                              | 0                | 1                   | 1                    |

| 3     | 100                              | ]*               | 1                   | 0                    |

| 4     | 0 0 0                            | 0                | 1                   | / 1                  |

| 5     | 000                              | 0                | 0                   | 0                    |

| 6     | 0 0 0                            | 0                | 0                   | 0                    |

| 7     | 000                              | 0                | l                   | l                    |

|       |                                  |                  |                     |                      |

\*Error located

#### TABLE 1

It is thus seen that the error in the third position  $(k_3)$  of the received n-tuple is corrected. If one is interested only in correcting errors in the information digits a k-stage buffer should be used. The decoder shown in this example uses pre-multiplication of the incoming sequence by  $x^{n-k}$  modulo G(x) so the resulting syndromes appear multiplied by  $x^{n-k}$  (Peterson, 1972). When decoding shortened cyclic codes the incoming codeword should either be pre-multiplied by

$$f(x) = \operatorname{REM}\left\{\frac{x^{n-k+1}}{G(x)}\right\}$$

(where i is the number of information digits removed from the code), or preceded by i zeros and applied to the

decoder for the original unshortened code. The next diagram (Figure 3.6) shows the Meggitt decoder for the code resulting from shortening by i=2 the (7,4) code of the above example. Pre-multiplication by

$$f(x) = \operatorname{REM}\left\{\frac{x^5}{x^3+x+1}\right\} = x^2+x+1$$

has been used.

FIGURE 3.6 : Meggitt Decoder for the (5,2) t=1 Shortened Cyclic Code

The difficulty with the Meggitt decoder is the complexity associated with its CLC for codes that correct two or more errors per codeword. However, with the advent of more complex integrated circuits, this decoding procedure can be attractive. The use of programmable read only memories (PROMs) simplifies drastically the design of the

CLC. The syndrome digits in the decoder may be used as addresses to the PROMs. With the aid of a small computer programme, those syndromes which are associated with error patterns having the highest order digit in error are determined, and the PROMs are then programmed to output a ONE in these cases and a zero otherwise. For a code having c check digits a 2<sup>°</sup> bit PROM is needed (or equivalent combination of PROMs). It is clear that in this way full use can be made of the 2<sup>°</sup> syndromes available. As a consequence, when decoding quasi-perfect codes, one is able to correct some error patterns with t+l errors which are usually left aside by other methods. Some quadratic residue codes, which have good distance properties but are hard to decode, can be considered for practical implementation using these techniques. The limitation of the extent to which PROMs can be applied is dictated by the available technology. Finally, the Meggitt decoder provides a general method of fully decoding any cyclic code, i.e. it does not suffer from the limitations of bounded distance decoders. The practical implementation of Meggitt decoders requires either the use of duplicate buffers or operation at twice the line clock rate.

## 3.9.2 Error Trapping Decoding

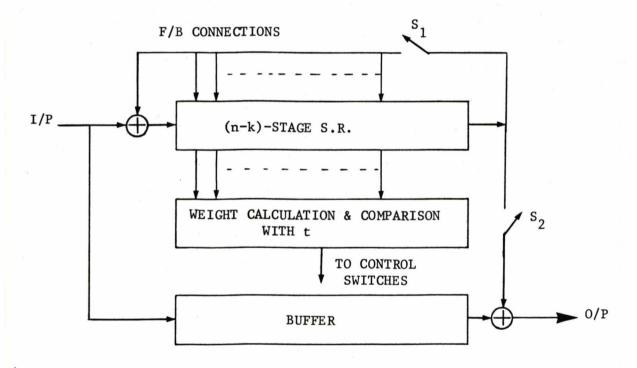

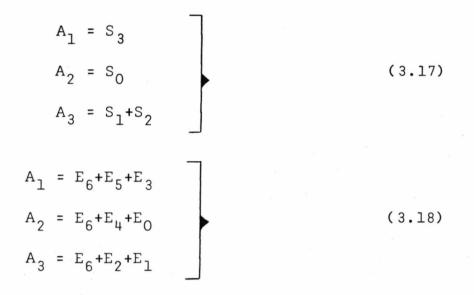

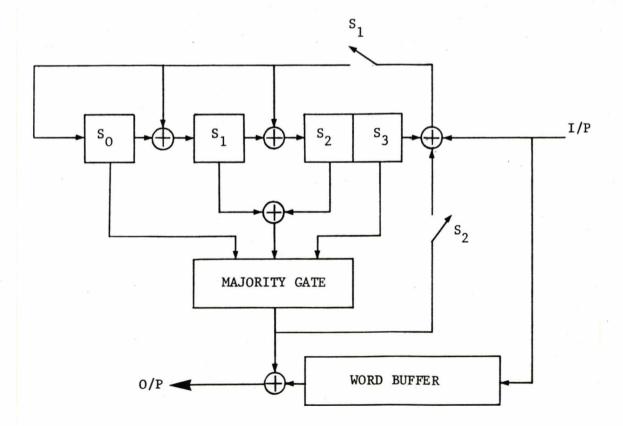

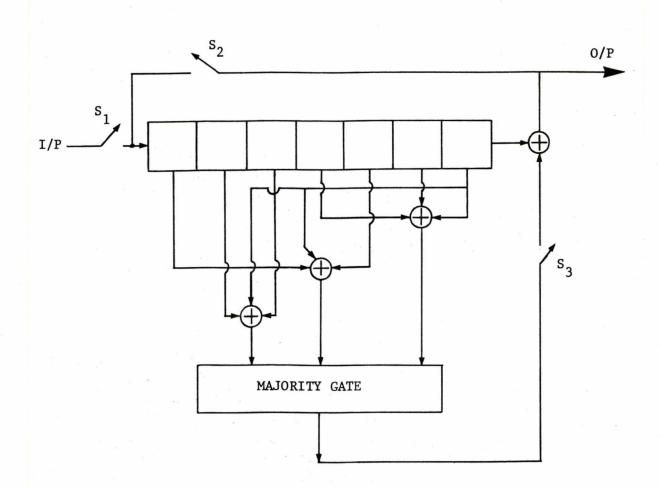

Error trapping decoding (Rudolph and Mitchell, 1964) is possibly the simplest way to decode a cyclic code when the errors to be corrected do not spread over a span greater than (n-k) digits, including the end around case